FEDR44V064B-02

MR44V064B

4/16

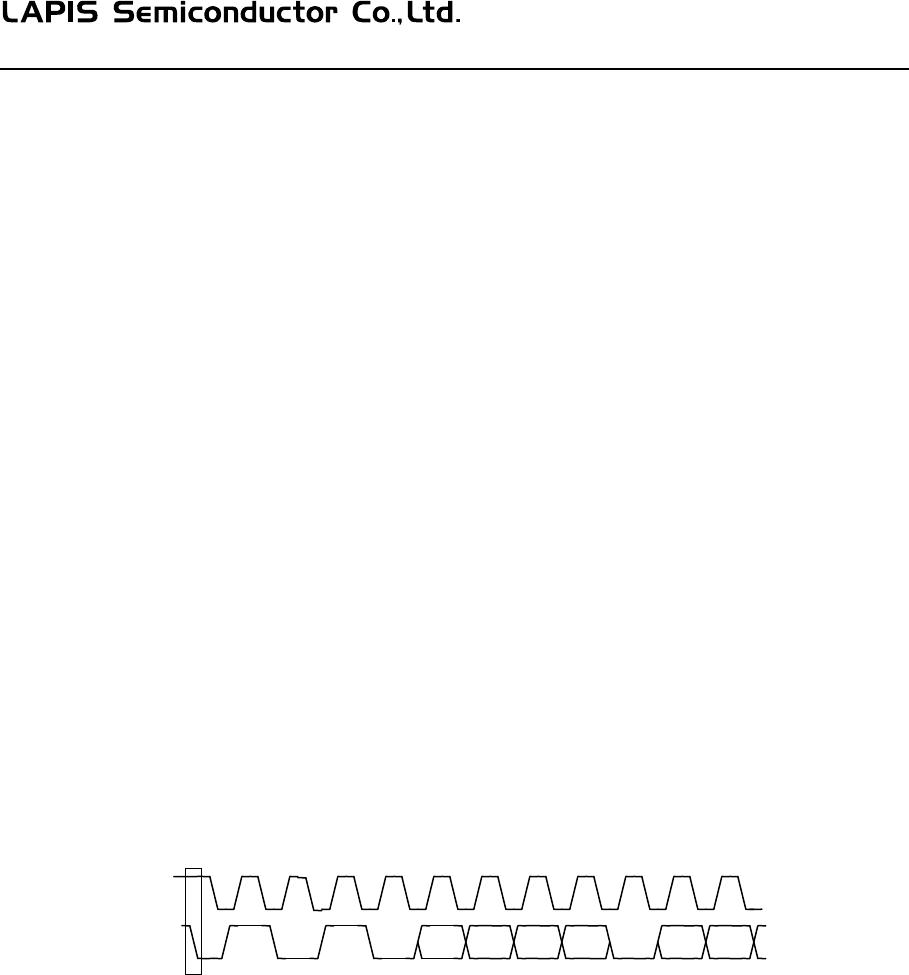

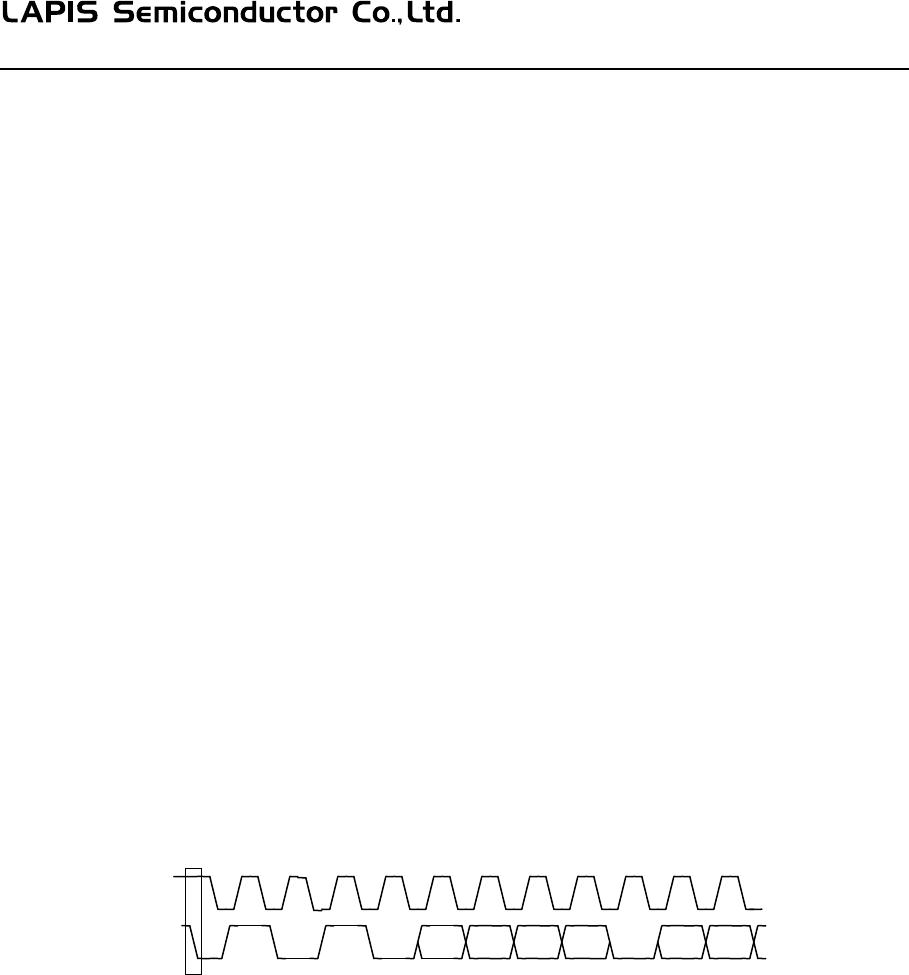

ACKNOWLEDGE ( ACK ) SIGNAL

This acknowledge ( ACK ) signal is a software rule to show whether data transfer has been made normally or not.

In master and slave, the device (μ-COM at slave address input of write command, read command, and this IC at

data output of read command) at the transmitter (sending) side releases the bus after output of 8bit data.

The device (this IC at slave address input of write command, read command, and μ-COM at data output of read

command) at the receiver (receiving) side sets SDA “LOW” during 9 clock cycles, and outputs acknowledge

signal ( ACK signal) showing that it has received the 8bit data.

This IC, after recognizing start condition and slave address (8bit), outputs acknowledge signal ( ACK signal)

“LOW”.

Each write action outputs acknowledge signal ( ACK signal ) “LOW”, at receiving 8bit data ( word address and

write data ).

Each read action outputs 8bit data ( read data ), and detects acknowledge signal ( ACK signal ) “LOW”.

When acknowledge signal ( ACK signal ) is detect, and stop condition is not sent from the master (μ-COM) side,

this IC continues data output. When acknowledge signal ( ACK signal ) is not detected, this IC stops data

transfer, and recognizes stop condition ( stop bit ), and ends read action. And this IC gets in status.

SLAVE ADDRESS

Output slave address after start condition from master.

The significant 4 bits of slave address are used for recognizing a device type. The device code of this IC is fixed

to “1010”.

Next slave addresses (A2 A1 A0 … device address) are for selecting devices, and plural ones can be used on a

same bus according to the number of device addresses.

The most insignificant bit (R/W…READ/WRITE) of slave address is used for designating write or read action,

and is as shown below.

Setting R/W to 0 write (setting 0 to word address setting of random read)

Setting R/W to 1 read

WRITE PROTECT

When WP terminal is set Vcc(H level), data rewrite of all addresses is prohibited. When it is set Vss(L level),

data rewrite of all address is enabled. Be sure to connect this terminal to Vcc or Vss, or control it to H level or L

level. Because this terminal is pulled down internally, in the case of Open the terminal will be recognized as L

level

During write cycle WP terminal must be always “L” level. WP terminal must be fixed from start condition to

stop condition.

SCL

SDA

START

condition

2 3

ACK

56 89741 12

1 0 01

2

1

0R/W