Low EMI Spectrum Spread Clock

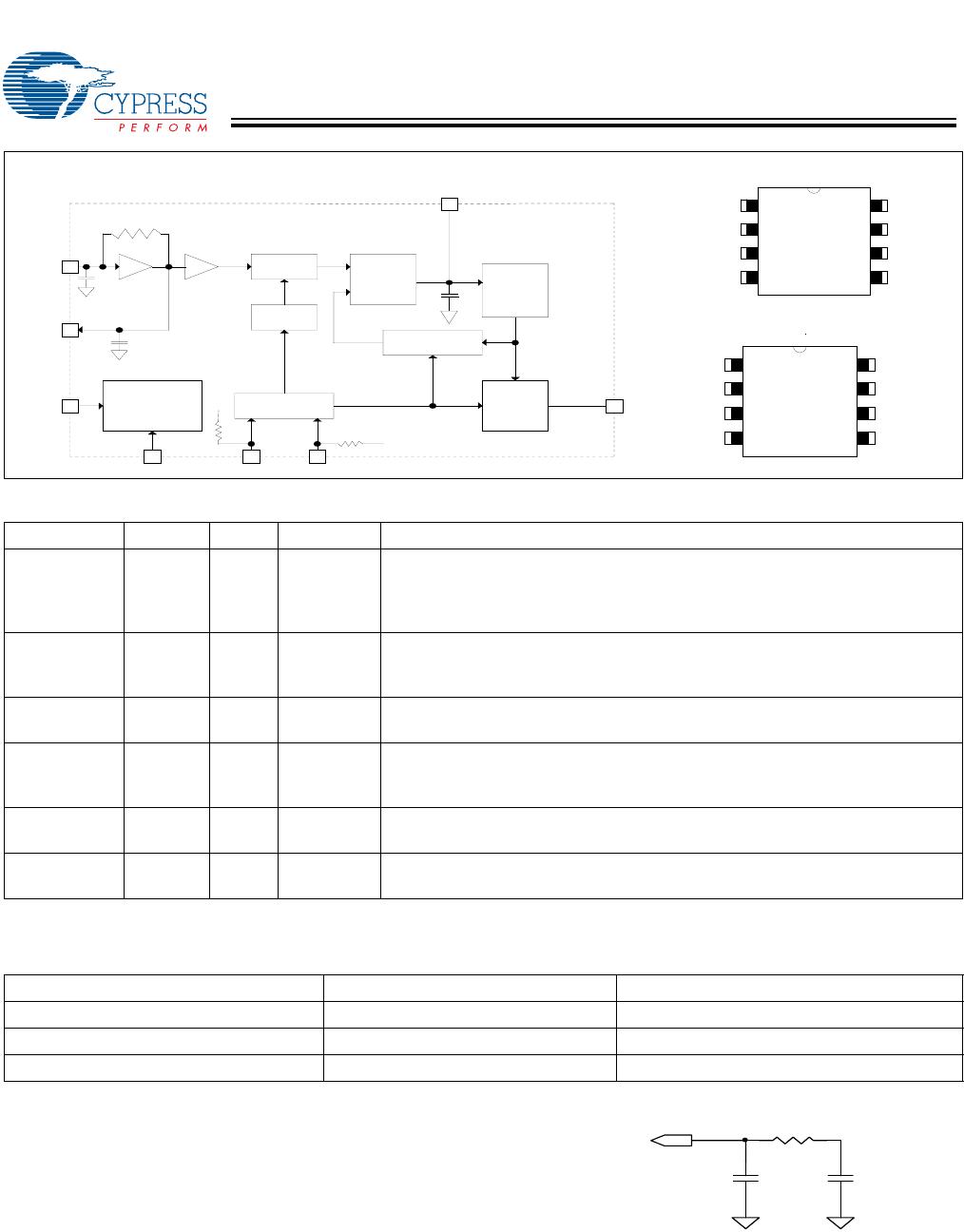

FS781/82/84

Cypress Semiconductor Corporation • 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Document #: 38-07029 Rev. *F Revised January 2, 2005

Features

• Spread Spectrum clock generator (SSCG) with 1×, 2×,

and 4× outputs

• 6- to 82-MHz operating frequency range

• Modulates external clocks including crystals, crystal

oscillators, or ceramic resonators

• Programmable modulation with simple R-C external

loop filter (LF)

• Center spread modulation

• 3V-5V power supply

• TTL-/CMOS-compatible outputs

• Low short-term jitter

• Low-power Dissipation

— 3.3 VDC = 37 mW – typical

— 5.0 VDC = 115 mW – typical

• Available in 8-pin SOIC and TSSOP packages

Applications

• Desktop/notebook computers

• Printers, copiers, and MFP

• Scanners and fax

• LCD displays and monitors

• CD-ROM, VCD, and DVD

• Automotive and embedded systems

• Networking, LAN/WAN

• Digital cameras and camcorders

•Modems

Benefits

• Programmable EMI reduction

• Fast time to market

• Lower cost of compliance

• No degradation in rise/fall times

• Lower component and PCB layer count

Functional Description

The Cypress FS781/82/84 are Spread Spectrum clock

generator ICs (SSCG) designed for the purpose of reducing

electromagnetic interference (EMI) found in today’s

high-speed digital systems.

The FS781/82/84 SSCG clocks use a Cypress-proprietary

technology to modulate the input clock frequency, XIN, by

modulating the frequency of the digital clock. By modulating

the reference clock the measured EMI at the fundamental and

harmonic frequencies of FSOUT is greatly reduced. This

reduction in radiated energy can significantly reduce the cost

of complying with regulatory requirements without degrading

digital waveforms.

The Cypress FS781/82/84 clocks are very simple and

versatile devices to use. By programming the two range select

lines, S0 and S1, any frequency from 6- to 82-MHz operating

range can be selected. The FS781/2/4 are designed to

operate over a very wide range of input frequencies and

provides 1×, 2×, and 4× modulated clock outputs.

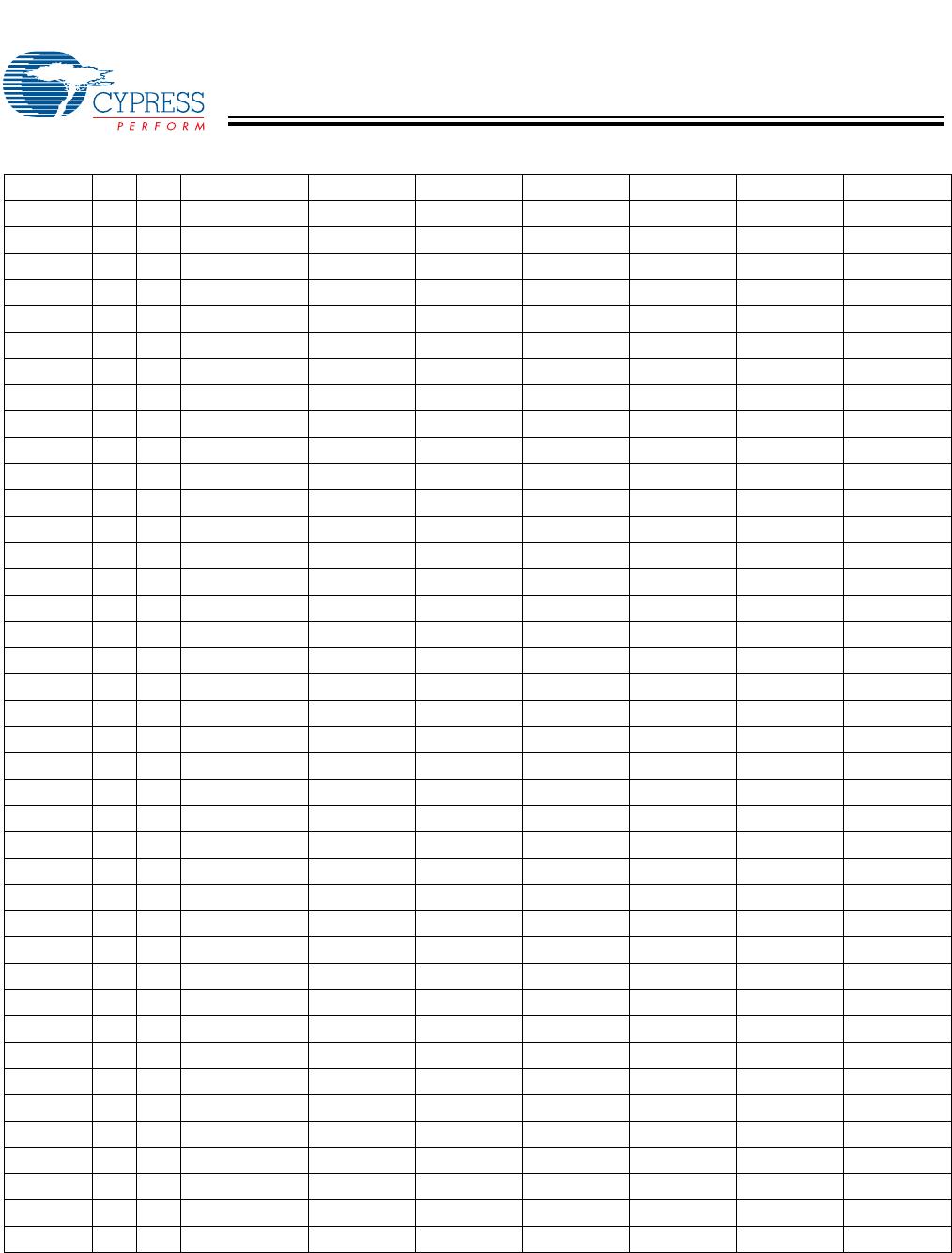

The FS78x devices have a simple frequency selection table

that allows operation from 6 MHz to 82 MHz in four separate

ranges. The bandwidth of the frequency spread at FSOUT is

determined by the values of the loop filter components. The

modulation rate is determined internally by the input frequency

and the selected input frequency range.

The Bandwidth of these products can be programmed from as

little as 1.0% up to as much as 4.0% by selecting the proper

loop filter value. Refer to the Loop Filter Selection chart in

Table 2 and Table 3 for the recommended values. Due to a

wide range of application requirements, an external loop filter

(LF) is used on the FS78x products. The user can select the

exact amount of frequency modulation suitable for the appli-

cation. Using a fixed internal loop filter would severely limit

the use of a wide range of modulation bandwidths (Spread %)

to a few discrete values. Refer to FS791/2/4 products for appli-

cations requiring 80- to 140-MHz frequency range.

[+] Feedback