FS781/82/84

Document #: 38-07029 Rev. *F Page 6 of 12

From the above parameters, the output clock at FSOUT will be

sweeping symmetrically around a center frequency of 20 MHz.

The minimum and maximum extremes of this clock will be

+200 kHz and –200 kHz. So we have a clock that is sweeping

from 19.8 MHz to 20.2 MHz and back again. If we were to look

at this clock on a spectrum analyzer we would see the picture

in Figure 3. Keep in mind that this is a drawing of a perfect

clock with no noise.

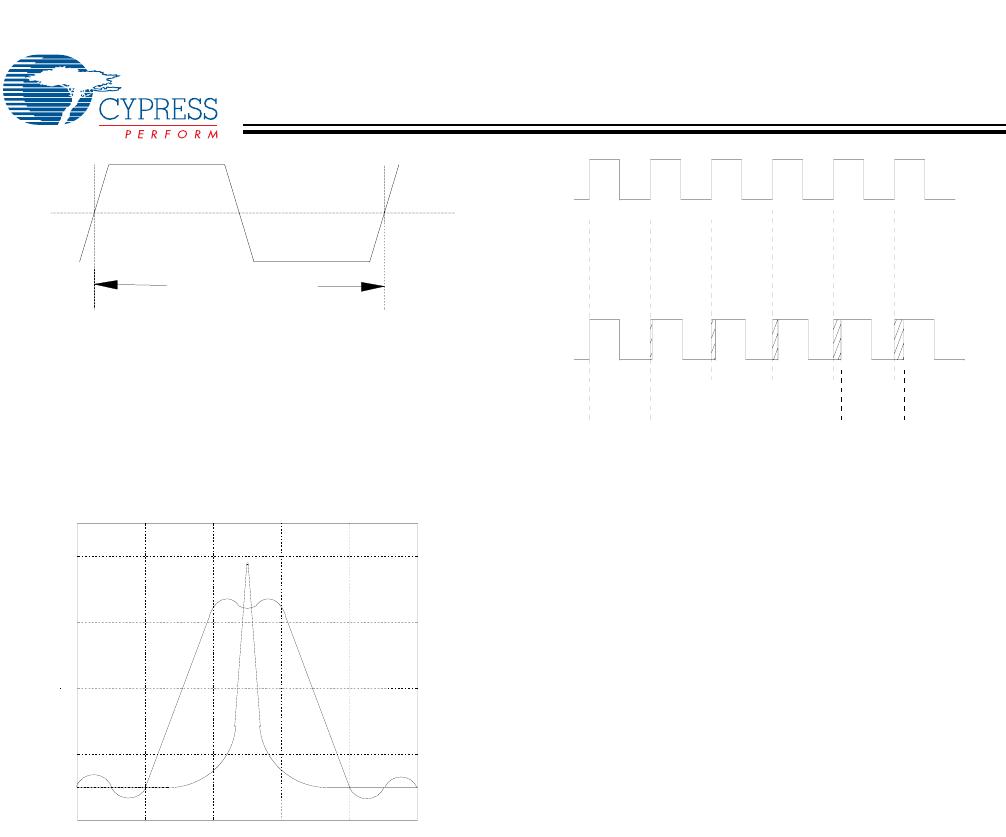

We see that the original 20-MHz reference clock is at the

center frequency (Cf), and the min. and max. extremes are

positioned symmetrically about the center frequency. This type

of modulation is called Center-Spread. Figure 4 shows a

20-MHz clock as it would be seen on an oscilloscope. The top

trace is the non-modulated reference clock. The bottom trace

is the modulated clock at pin 6. From this comparison chart

you can see that the frequency is decreasing and the period

of each successive clock is increasing. The Tc measurements

on the left and right of the bottom trace indicate the max. and

min. extremes of the clock. Intermediate clock changes are

small and accumulate to achieve the total period deviation.

The reverse of this figure would show the clock going from

minimum extreme back to the high extreme.

Looking at Figure 3, you will note that the peak amplitude of

the 20-MHz non-modulated clock is higher than the wideband

modulated clock. This difference in peak amplitudes between

modulated and unmodulated clocks is the reason why SSCG

clocks are so effective in digital systems. This figure refers to

the fundamental frequency of a clock. A very important charac-

teristic of the SSCG clock is that the bandwidth of the funda-

mental frequency is multiplied by the harmonic number. In

other words, if the bandwidth of a 20-MHz clock is 200 kHz,

the bandwidth of the third harmonic will be 3 × 200, or 600 kHz.

The amount of bandwidth is relative to the amount of energy

in the clock. Consequently, the wider the bandwidth, the

greater the energy reduction of the clock.

Most applications will not have a problem meeting agency

specifications at the fundamental frequency. It is the higher

harmonics that usually cause the most problems. With an

SSCG clock, the bandwidth and peak energy reduction

increases with the harmonic number. Consider that the

eleventh harmonic of a 20-MHz clock is 220 MHz. With a total

spread of 200 kHz at 20 MHz, the spread at the eleventh

harmonic would be 2.20 MHz, which greatly reduces the peak

energy content. It is typical to see as much as 12- to 18-dB

reduction at the higher harmonics, due to a modulated clock.

The difference in the peak energy of the modulated clock and

the non-modulated clock in typical applications will see a

2–3dB reduction at the fundamental and as much as 8 – 10

dB reduction at the intermediate harmonics: third, fifth,

seventh, etc. At the higher harmonics, it is quite possible to

reduce the peak harmonic energy, compared to the unmodu-

lated clock, by as much as 12 to 18 dB.

Application Notes and Schematic

Figure 5 is configured for the following parameters:

Package selected = FS781.

X

IN

= 20-MHz crystal

FSOUT = 20 MHz (S0 = 1 and S1 = 0).

Bandwidth of the FSOUT clock is determined by the values of

the loop filter connected to pin 4.

50% 50%

Tc = 50 ns.

Figure 2. 20-MHz Unmodulated Clock

Fc = 20 MHz

Fmin =

19.8 MHz

Fmax =

20.2 MHz

Figure 3. Spectrum Analysis of 19.8–20.2 MHz Clock

Tc = 50.50

Tc =49.50 ns.

Figure 4. Period Comparison Chart

[+] Feedback