5

Integrated

Circuit

Systems, Inc.

ICS9FG1904B-1

1255B—08/03/07

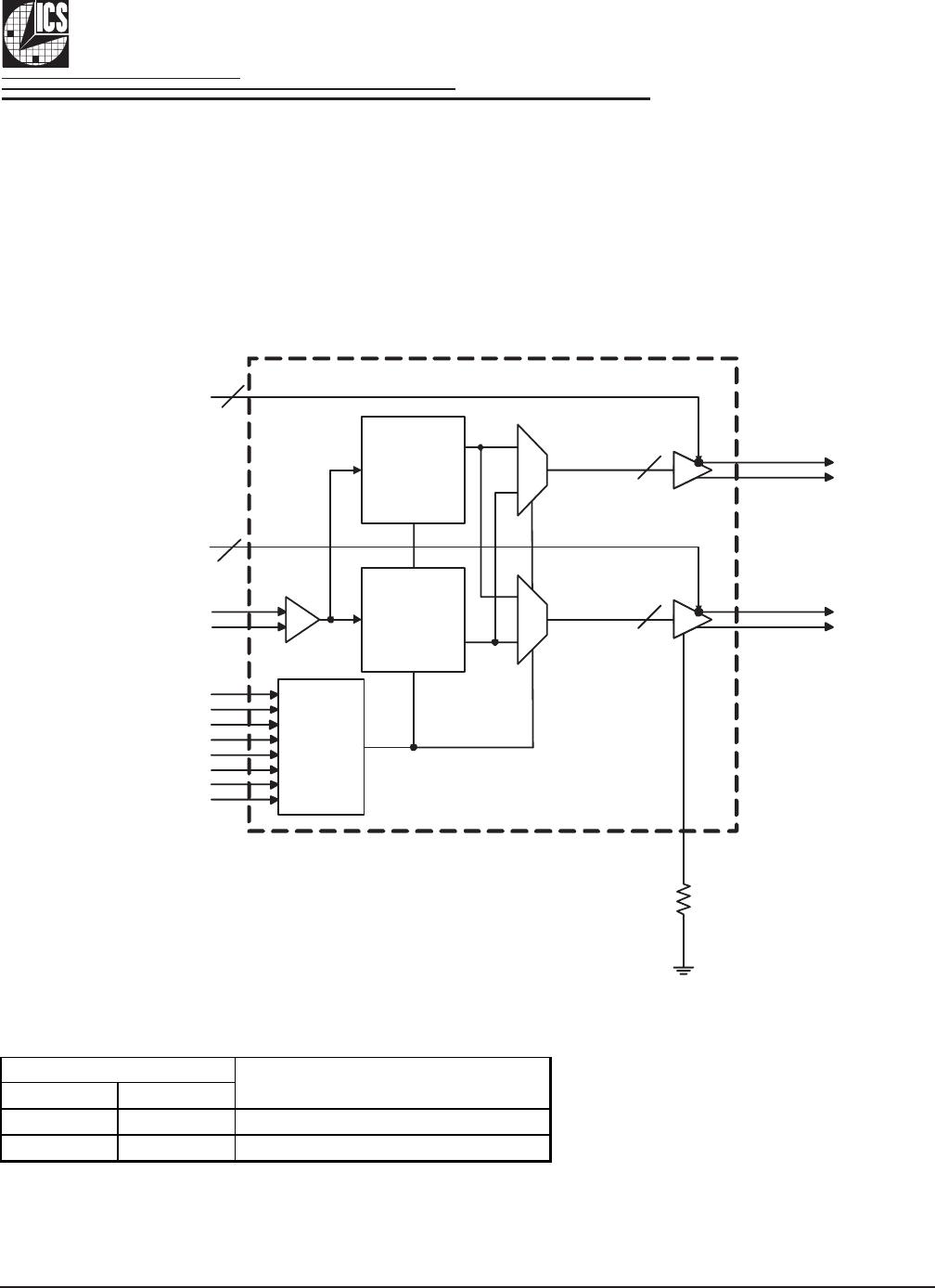

ICS 9FG1904B-1 Programmable Gear Ratios

CLK_IN

(CPU FSB)

MHz

Geared DIF

Outputs

MHz

Mn

Gear

Ratio n/M

(FS_A_410#)

Byte 0,

bit 4

FS4

Byte 0,

bit 3

FS3

Byte 0,

bit 2

FS2

Byte 0,

bit 1

FS1

Byte 0,

bit 0

FS0

Notes

100.00 133.33 3 4 1.333 0 0000

100.00 166.67 3 5 1.667 0 0001

100.00 200.00 1 2 2.000 0 0010

100.00 266.67 3 8 2.667 0 0011

100.00 333.33 3 10 3.333 0 0100

100.00 400.00 1 4 4.000 0 0101

133.33 166.67 4 5 1.250 0 01101

133.33 200.00 2 3 1.500 0 01111

133.33 266.67 1 2 1.250 0 1000

133.33 333.33 2 5 1.500 0 1001

133.33 100.00 4 3 0.750 0 1010

166.67 133.33 5 4 0.800 0 1011

1,3

166.67 200.00 5 6 1.200 0 11001

166.67 266.67 5 8 1.600 0 1101

160/

166.67

320/

333.33

122.000 0 11101,2

166.67 400.00 5 12 2.400 0 1111

200.00 133.33 3 2 0.667 1 00001

200.00 166.67 6 5 0.833 1 00011

200.00 266.67 3 4 1.333 1 00101

200.00 333.33 3 5 1.667 1 00111

200.00 400.00 1 2 2.000 1 01001

266.67 133.33 2 1 0.500 1 01011

266.667/

320.00

166.67/

200.00

850.625 1 01101, 6

266.67 200.00 4 3 0.750 1 01111

333.33 133.33 5 2 0.400 1 10001

320/

333.33

160/

166.67

210.500 1 10011,5

333.33 200.00 5 3 0.600 1 10101

400.00 133.33 3 1 0.333 1 1011

1,4

400.00 160.00 5 2 0.400 1 11001

400.00 166.67 12 5 0.417 1 11011

400.00 320.00 5 4 0.800 1 11101

400.00 333.33 6 5 0.833 1 11111

Notes:

1. Targetted input/output frequency pairs

2. This Gear is also used for 160MHz/320 MHz.

3. Gear Ratio 5/4 is power up default for FS_A_410 = 1

4. Gear Ratio 3/1 is power up default for FS_A_410 = 0

5. This Gear is also used for 400MHz/200MHz

6. This Gear is also used for 320MHz/200MHz