AD8180/AD8182

–7–

REV. B

for R

L

> 10 kΩ. For heavier loads, the dc gain is approximately

that of the voltage divider formed by the output impedance of

the mux (typically 27 Ω) and R

L

.

High speed disable clamp circuits at the bases of Q5–Q8 (not

shown) allow the buffers to turn off quickly and cleanly without

dissipating much power once off. Moreover, these clamps shunt

displacement currents flowing through the junction capacitances

of Q1–Q4 away from the bases of Q5–Q8 and to ac ground

through low impedances. The two-pole high pass frequency

response of the T switch formed by these clamps is a significant

improvement over the one-pole high pass response of a simple

series CMOS switch. As a result, board and package parasitics,

especially stray capacitance between inputs and outputs may

limit the achievable crosstalk and off isolation.

LAYOUT CONSIDERATIONS:

Realizing the high speed performance attainable with the

AD8180 and AD8182 requires careful attention to board layout

and component selection. Proper RF design techniques and low

parasitic component selection are mandatory.

Wire wrap boards, prototype boards, and sockets are not recom-

mended because of their high parasitic inductance and capaci-

tance. Instead, surface-mount components should be soldered

directly to a printed circuit board (PCB). The PCB should have

a ground plane covering all unused portions of the component

side of the board to provide a low impedance ground path. The

ground plane should be removed from the area near input and

output pins to reduce stray capacitance.

Chip capacitors should be used for supply bypassing. One end

of the capacitor should be connected to the ground plane and

the other within 1/4 inch of each power pin. An additional large

(4.7 µF–10 µF) tantalum capacitor should be connected in

parallel with each of the smaller capacitors for low impedance

supply bypassing over a broad range of frequencies.

Signal traces should be as short as possible. Stripline or micros-

trip techniques should be used for long signal traces (longer

than about 1 inch). These should be designed with a character-

istic impedance of 50 Ω or 75 Ω and be properly terminated at

the end using surface mount components.

Careful layout is imperative to minimize crosstalk. Guards

(ground or supply traces) must be run between all signal traces

to limit direct capacitive coupling. Input and output signal lines

should fan out away from the mux as much as possible. If mul-

tiple signal layers are available, a buried stripline structure hav-

ing ground plane above, below, and between signal traces will

have the best crosstalk performance.

Return currents flowing through termination resistors can also

increase crosstalk if these currents flow in sections of the finite-

impedance ground circuit that is shared between more than one

input or output. Minimizing the inductance and resistance of the

ground plane can reduce this effect, but further care should be

taken in positioning the terminations. Terminating cables directly

at the connectors will minimize the return current flowing on the

board, but the signal trace between the connector and the mux will

look like an open stub and will degrade the frequency response.

Moving the termination resistors close to the input pins will im-

prove the frequency response, but the terminations from neigh-

boring inputs should not have a common ground return.

THEORY OF OPERATION

The AD8180 and AD8182 video multiplexers are designed for

fast-switching (10 ns) and wide bandwidth (> 750 MHz). This

performance is attained with low power dissipation (3.8 mA per

active channel) through the use of proprietary circuit techniques

and a dielectrically-isolated complementary bipolar process.

These devices have a fast disable function that allows the out-

puts of several muxes to be wired in parallel to form a larger mux

with little degradation in switching time. The low disabled output

capacitance (1.7 pF) of these muxes helps to preserve the system

bandwidth in larger matrices. Unlike earlier CMOS switches,

the switched open-loop buffer architecture of the AD8180 and

AD8182 provides a unidirectional signal path with minimal switch-

ing glitches and constant, low input capacitance. Since the input

impedance of these muxes is nearly independent of the load imped-

ance and the state of the mux, the frequency response of the ON

channels in a large switch matrix is not affected by fanout.

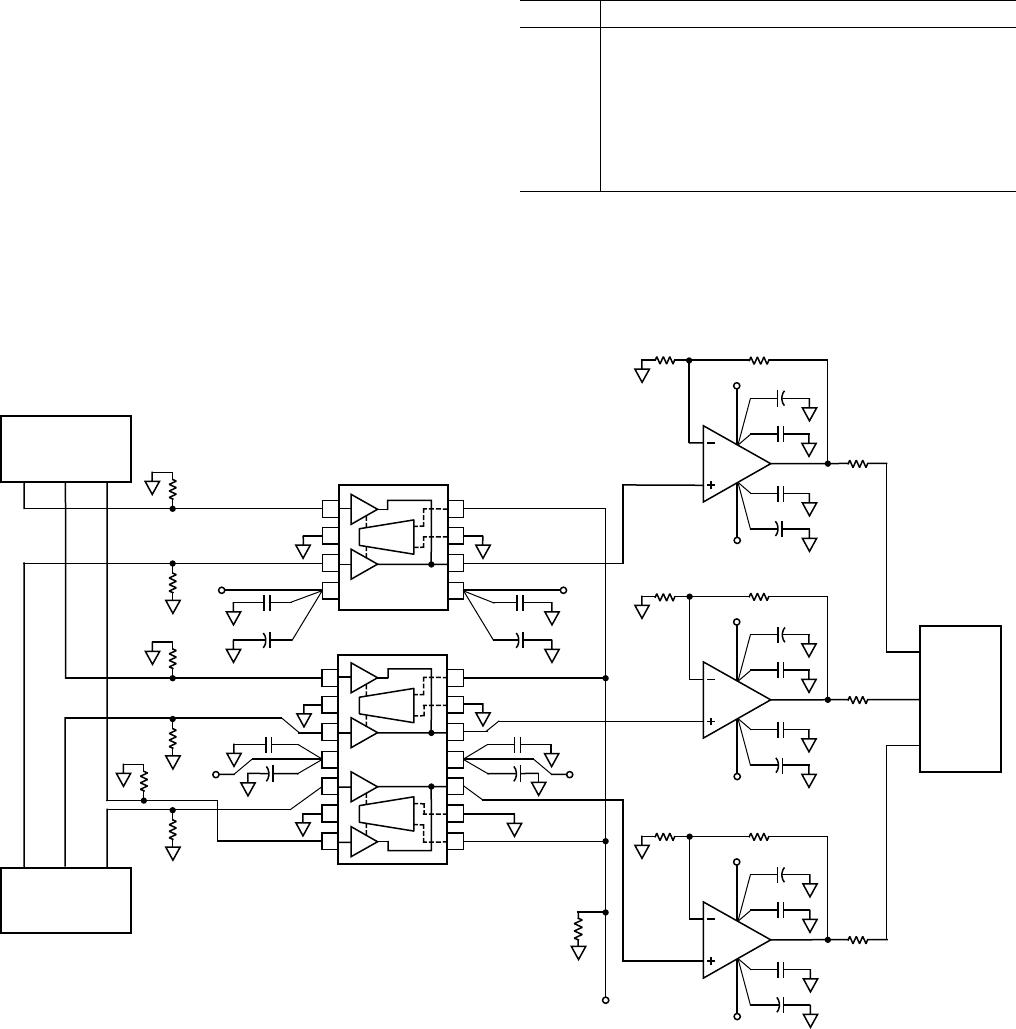

Figure 22 shows a block diagram and simplified schematic of the

AD8180, which contains two switched buffers (S0 and S1) that

share a common output. The decoder logic translates TTL-

compatible logic inputs (SELECT and ENABLE) to internal,

differential ECL levels for fast, low-glitch switching. The SELECT

input determines which of the two buffers is enabled, unless the

ENABLE input is HIGH, in which case both buffers are disabled

and the output is switched to a high impedance state.

Q5

Q7

Q3

Q1

S0

I1

I3

Q6

Q8

Q4

Q2

S1

I2

I4

DECODER

AD8180

1

2

3

4

IN0

GND

IN1

+V

S

8

7

6

5

–V

S

OUT

ENABLE

SELECT

Figure 22. Block Diagram and Simplified Schematic of the

AD8180 Multiplexer

Each open-loop buffer is implemented as a complementary

emitter follower that provides high input impedance, symmetric

slew rate and load drive, and high output-to-input isolation due to

its β

2

current gain. The selected buffer is biased ON by fast

switched current sources that allow the buffer to turn on quickly.

Dedicated flatness circuits, combined with the open-loop architec-

ture of the AD8180 and AD8182, keep peaking low (typically

< 1 dB) when driving high capacitive loads, without the need for

external series resistors at the input or output. If better flatness

response is desired, an input series resistance (R

S

) may be used

(refer to Figure 20), although this will increase crosstalk. The dc

gain of the AD8180 and AD8182 is almost independent of load