PCA9536 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

Product data sheet Rev. 6 — 7 November 2017 7 of 24

NXP Semiconductors

PCA9536

4-bit I

2

C-bus and SMBus I/O port

6.1.5 Register 3 - Configuration register

This register configures the directions of the I/O pins. If a bit in this register is set, the

corresponding port pin is enabled as an input with high-impedance output driver. If a bit in

this register is cleared, the corresponding port pin is enabled as an output. At reset, the

I/Os are configured as inputs with a weak pull-up to V

DD

.

‘Not used’ bits can be programmed with either logic 0 or logic 1.

6.2 Power-on reset

When power is applied to V

DD

, an internal Power-On Reset (POR) holds the PCA9536 in

a reset condition until V

DD

has reached V

POR

. At that point, the reset condition is released

and the PCA9536 registers and state machine will initialize to their default states.

Thereafter, V

DD

must be lowered below 0.2 V to reset the device.

For a power reset cycle, V

DD

must be lowered below 0.2 V and then restored to the

operating voltage.

6.3 I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a

high-impedance input with a weak pull-up (100 k typical) to V

DD

. The input voltage may

be raised above V

DD

to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is enabled, depending on the

state of the Output Port register. Care should be exercised if an external voltage is applied

to an I/O configured as an output because of the low-impedance paths that exist between

the pin and either V

DD

or V

SS

.

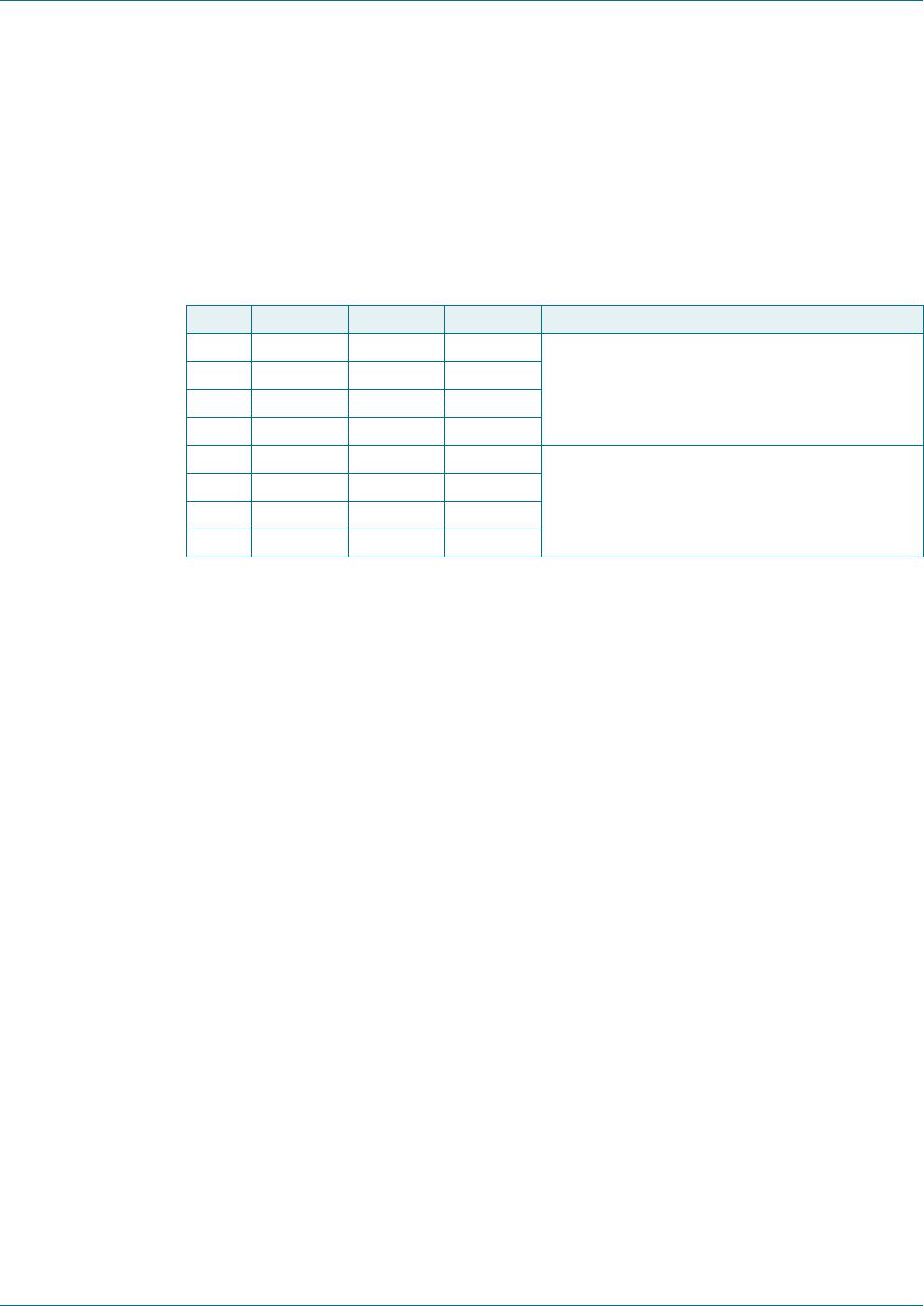

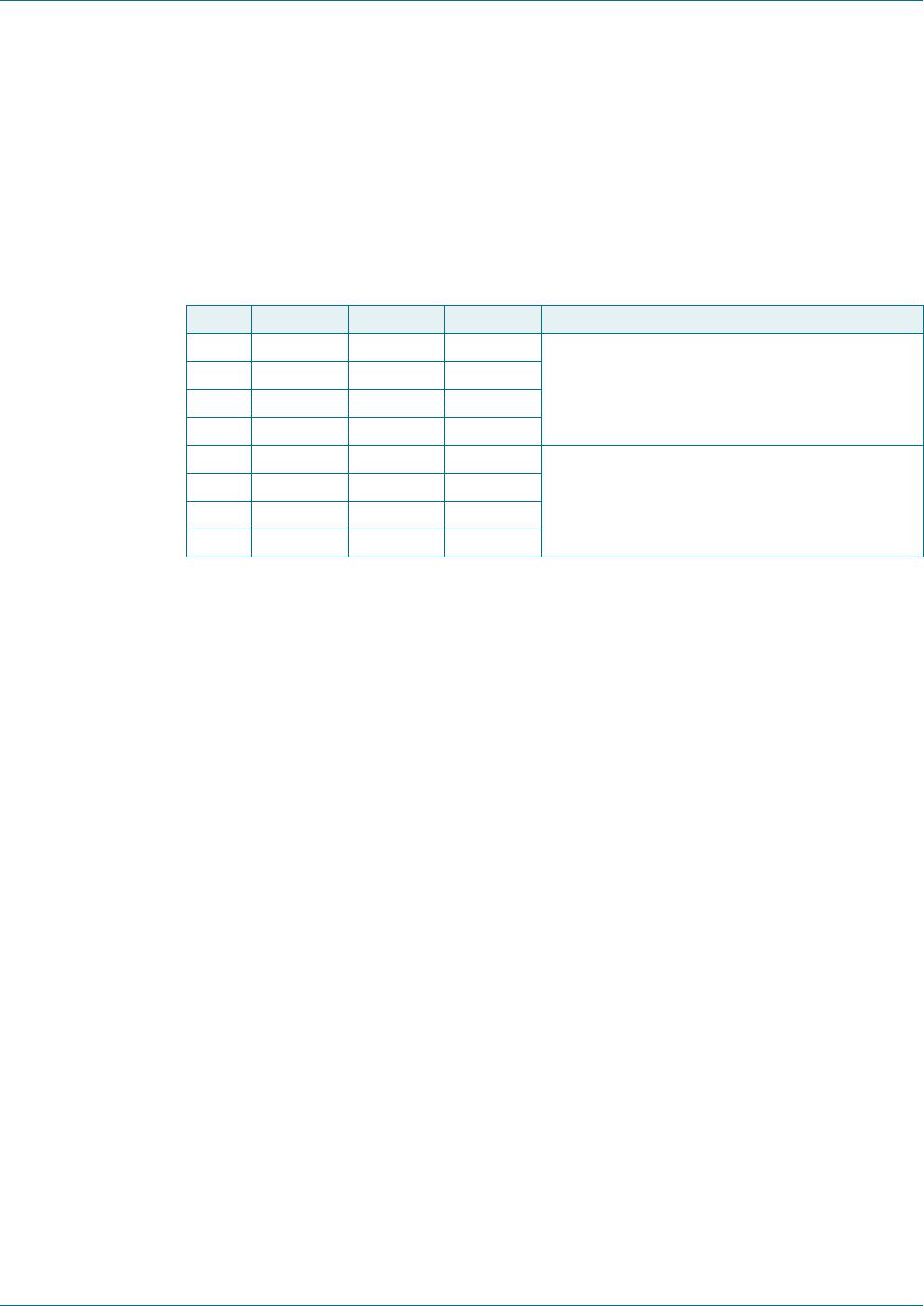

Table 8. Register 3 - Configuration register bit description

Legend: * default value

Bit Symbol Access Value Description

7 C7 R/W 1* not used

6C6 R/W 1*

5C5 R/W 1*

4C4 R/W 1*

3 C3 R/W 1* configures the directions of the I/O pins

0 = corresponding port pin enabled as an output

1 = corresponding port pin configured as input

(default value)

2C2 R/W 1*

1C1 R/W 1*

0C0 R/W 1*