IDT8N3SV76 Data Sheet LVPECL-FREQUENCY PROGRAMMABLE VCXO

IDT8N3SV76CCD

REVISION A NOVEMBER 19, 2013 3 ©2013 Integrated Device Technology, Inc.

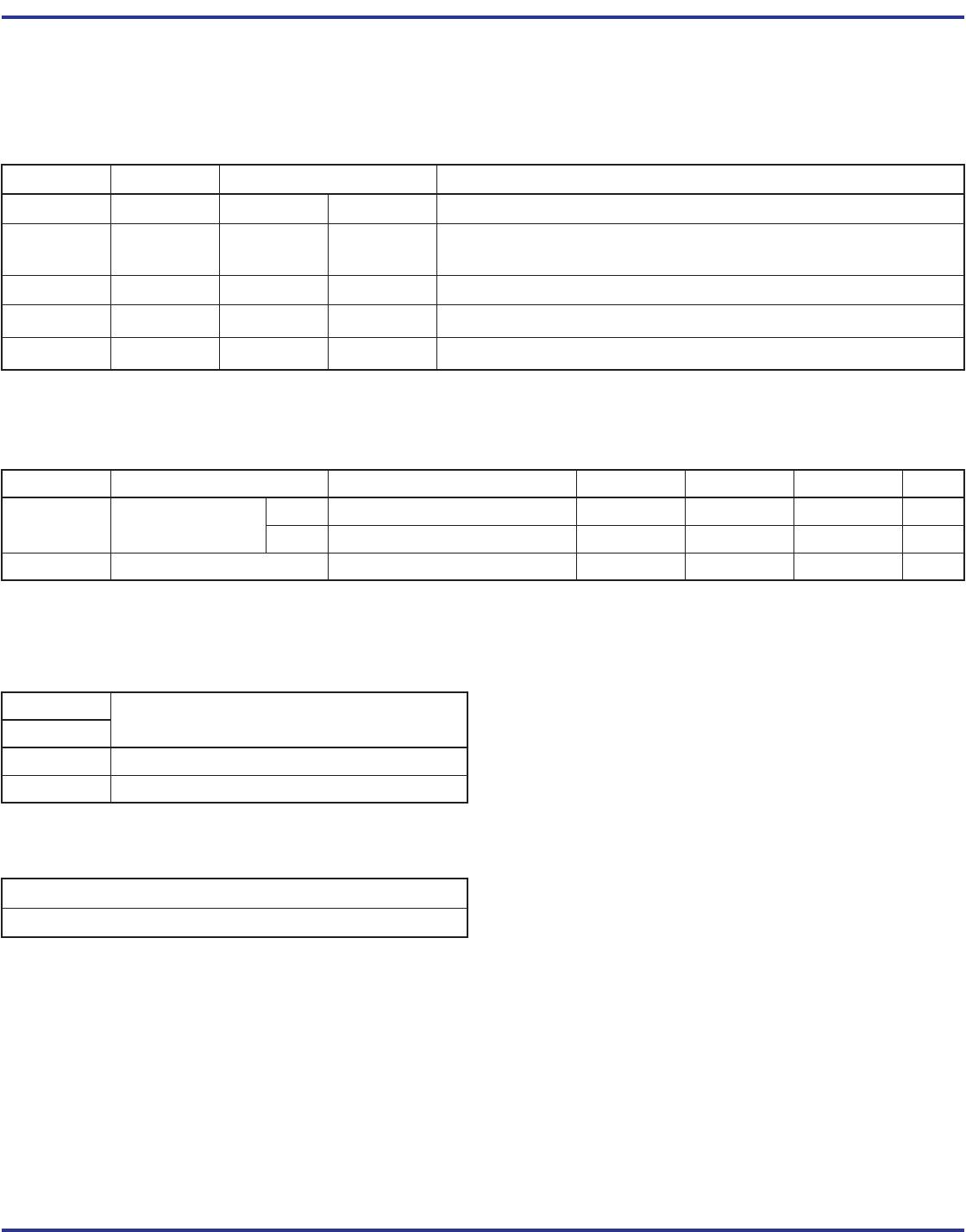

Principles of Operation

The block diagram consists of the internal 3

RD

overtone crystal and

oscillator which provide the reference clock f

XTAL

of 114.285MHz.

The PLL includes the FemtoClock® NG VCO along with the

Pre-divider (P), the feedback divider (M) and the post divider (N). The

P, M, and N dividers determine the output frequency based on the

f

XTAL

reference. The feedback divider is fractional supporting a huge

number of output frequencies. Internal registers are used to hold up

the factory pre-set configuration setting. The P, M, and N frequency

configurations support an output frequency range of 15.476MHz to

866.67MHz and 975MHz to 1,300MHz.

The devices use the fractional feedback divider with a delta-sigma

modulator

for noise shaping and robust frequency synthesis

capability. The relatively high reference frequency minimizes phase

noise generated by frequency multiplication and allows more efficient

shaping of noise by the delta-sigma modulator. The output frequency

is determined by the 2-bit pre-divider (P), the feedback divider (M)

and the 7-bit post divider (N). The feedback divider (M) consists of

both a 7-bit integer portion (MINT) and an 18-bit fractional portion

(MFRAC) and provides the means for high-resolution frequency

generation. The output frequency f

OUT

is calculated by:

f

OUT

f

XTAL

1

PN

------------- MINT

MFRAC 0.5+

2

18

-------------------------------------+=

Frequency Configuration

An order code is assigned to each frequency configuration and the

VCXO pull-range programmed by the factory (default frequencies).

For more information on the available default frequencies and order

codes, please see the Ordering Information Section in this document.

For available order codes, see the FemtoClock NG Ceramic-Package

XO and VCXO Ordering Product Information document.

For more information on programming capabilities of the device for

custom

frequency and pull-range configurations, see the FemtoClock

NG Ceramic 5x7 Module Programming Guide.