Production Data WM1824B

w

PD, Rev 4.0, November 2012

11

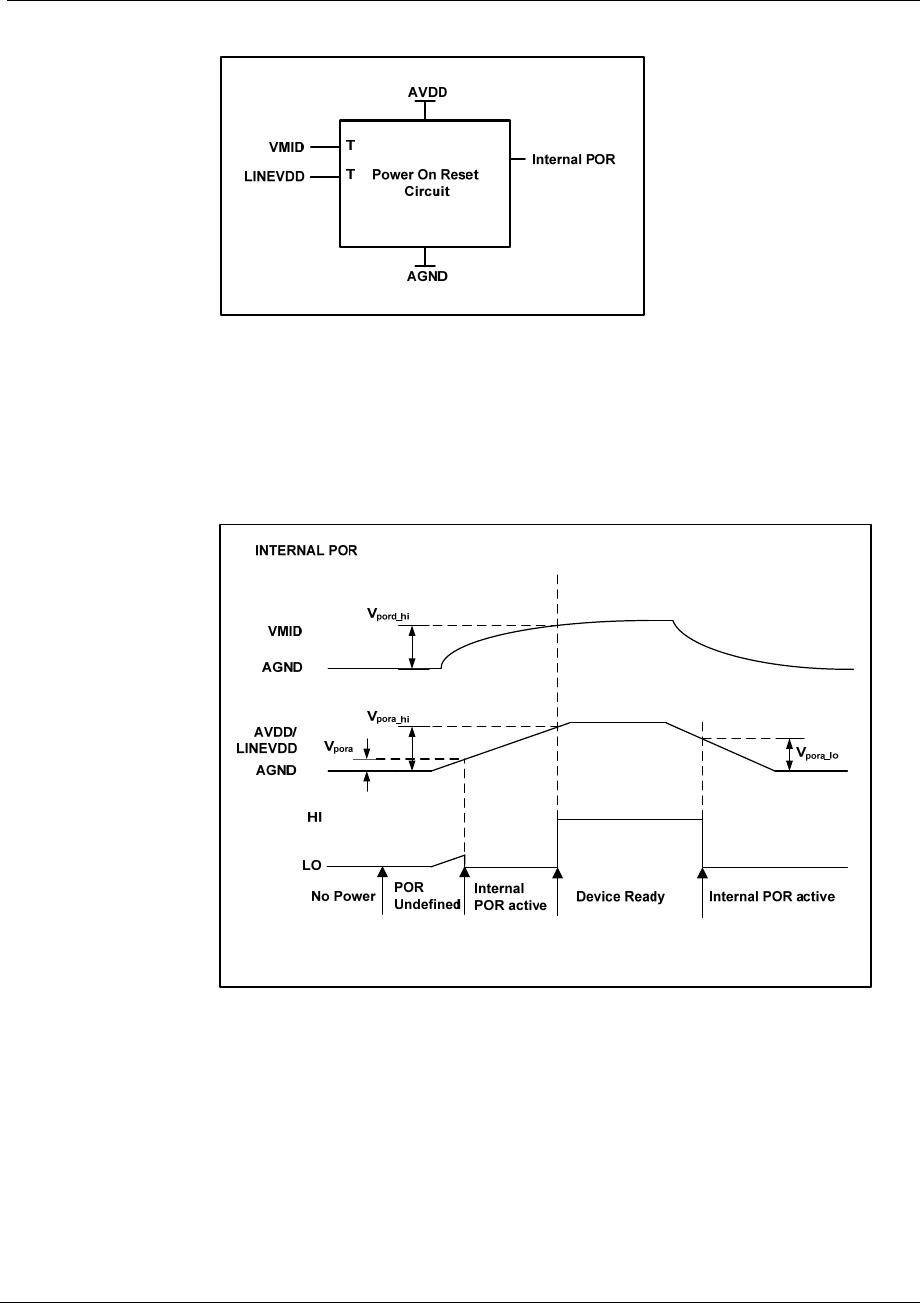

POWER ON RESET CIRCUIT

Figure 4 Internal Power on Reset Circuit Schematic

The WM1824B includes an internal Power-On-Reset circuit, as shown in Figure 4, which is

used to reset the DAC digital logic into a default state after power up. The POR circuit is

powered by AVDD and has as its inputs VMID and LINEVDD. It asserts POR low if VMID or

LINEVDD are below a minimum threshold.

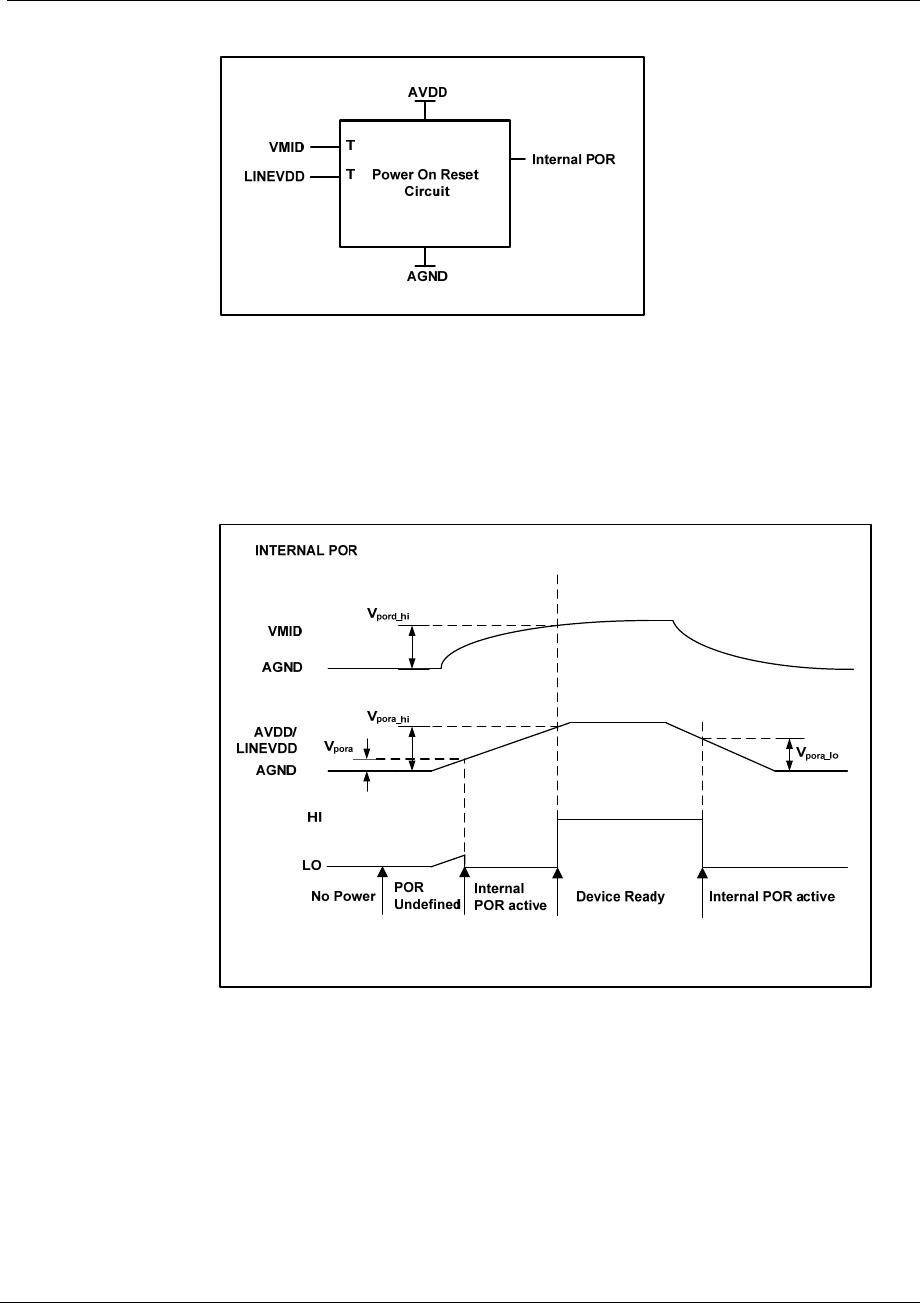

Figure 5 Typical Power Timing Requirements

Figure 5 shows a typical power-up sequence where LINEVDD comes up with AVDD. When

AVDD goes above the minimum threshold, V

pora

, there is enough voltage for the circuit to

guarantee POR is asserted low and the chip is held in reset. In this condition, all writes to the

control interface are ignored. After VMID rises to V

pord_hi

and AVDD rises to V

pora_hi,

POR is

released high and access to the control interface and audio interface may take place. This

assumes that DBVDD is at a level within the recommended operating conditions.

On power down, PORB is asserted low whenever LINEVDD or AVDD drop below the

minimum threshold V

pora_low

.