XC2C256 CoolRunner-II CPLD

6 www.xilinx.com DS094 (v3.2) March 8, 2007

Product Specification

R

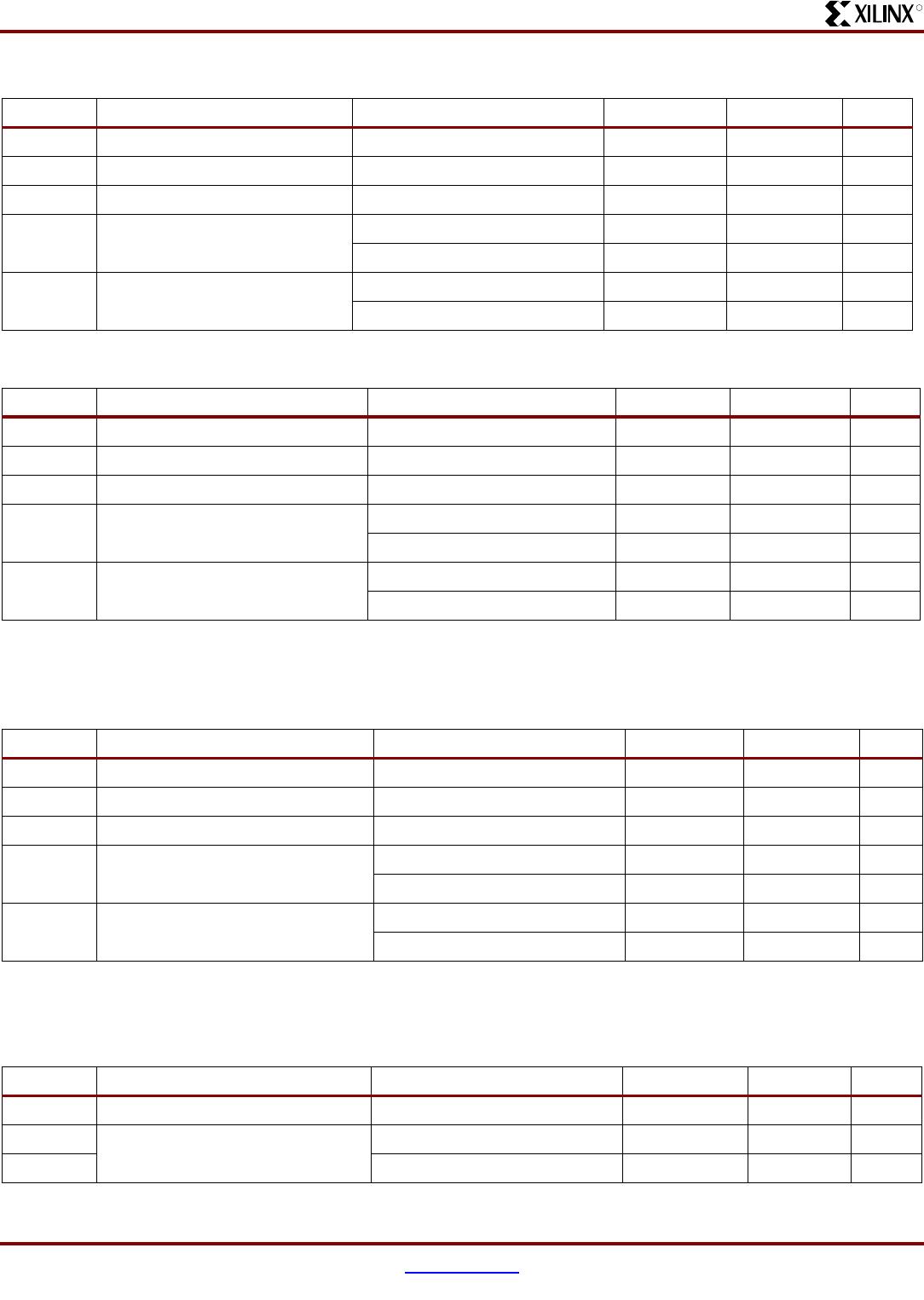

SSTL3-1 DC Voltage Specifications

HSTL1 DC Voltage Specifications

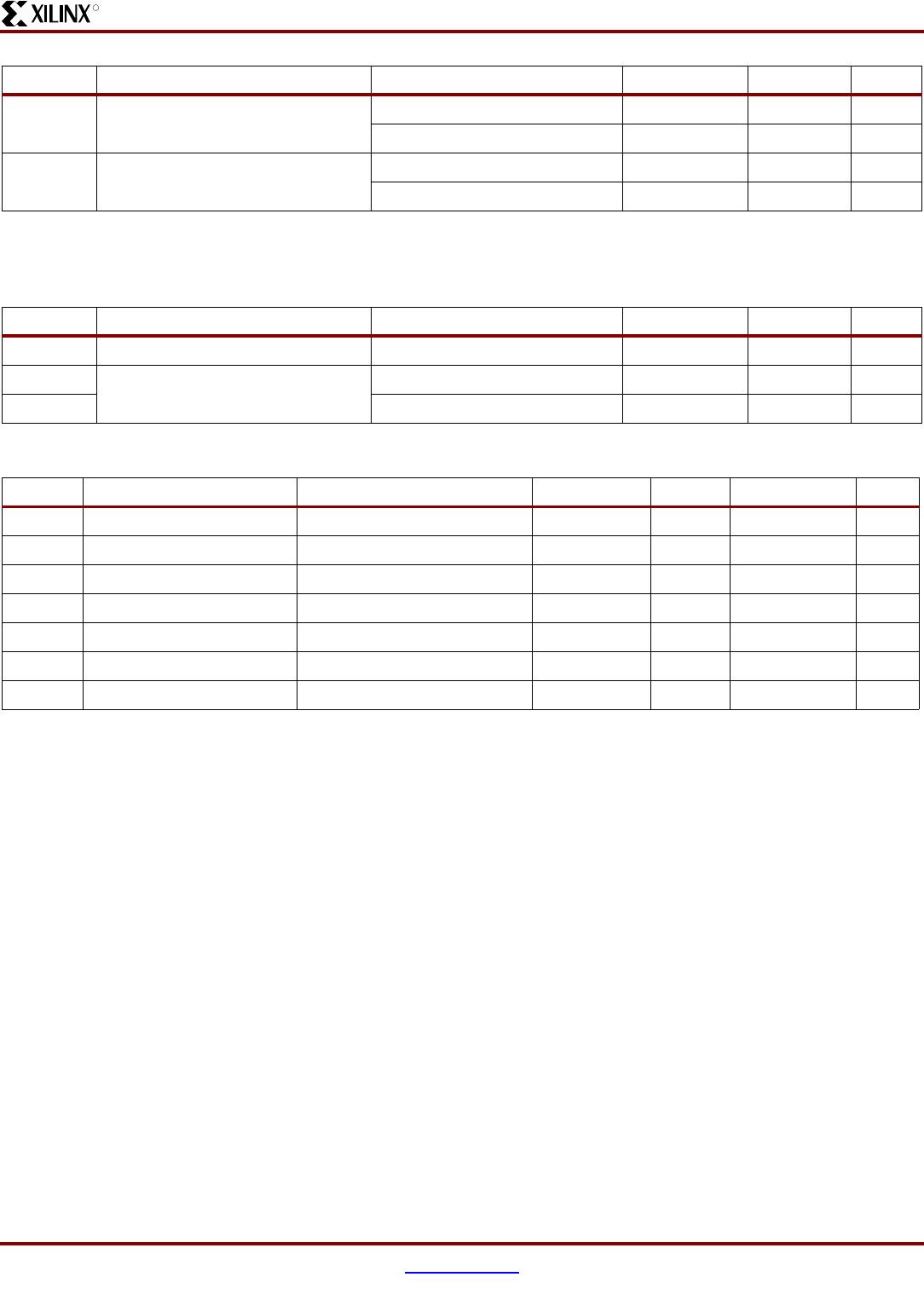

AC Electrical Characteristics Over Recommended Operating Conditions

Symbol Parameter Test Conditions Min. Typ Max. Units

V

CCIO

Input source voltage - 3.0 3.3 3.6 V

V

REF

(1)

Input reference voltage - 1.3 1.5 1.7 V

V

TT

(2)

Termination voltage - V

REF

– 0.05 1.5 V

REF

+ 0.05 V

V

IH

High level input voltage - V

REF

+ 0.2 - V

CCIO

+ 0.3 V

V

IL

Low level input voltage - –0.3 - V

REF

– 0.2 V

V

OH

High level output voltage I

OH

= –8 mA, V

CCIO

= 3V V

CCIO

– 1.1 - - V

V

OL

Low level output voltage I

OL

= 8 mA, V

CCIO

= 3V - - 0.7 V

Notes:

1. V

REF

should track the variations in V

CCIO

, also peak to peak AC noise on V

REF

may not exceed ± 2% V

REF

2. V

TT

of transmitting device must track V

REF

of receiving devices

Symbol Parameter Test Conditions Min. Typ Max. Units

V

CCIO

Input source voltage - 1.4 1.5 1.6 V

V

REF

(1)

Input reference voltage - 0.68 0.75 0.90 V

V

TT

(2)

Termination voltage - - V

CCIO

x

0.5 - V

V

IH

High level input voltage - V

REF

+ 0.1 - 1.9 V

V

IL

Low level input voltage - –0.3 - V

REF

– 0.1 V

V

OH

High level output voltage I

OH

= –8 mA, V

CCIO

= 1.7V V

CCIO

– 0.4 - - V

V

OL

Low level output voltage I

OL

= 8 mA, V

CCIO

= 1.7V - - 0.4 V

Notes:

1. V

REF

should track the variations in V

CCIO

, also peak-to-peak AC noise on V

REF

may not exceed ± 2% V

REF

2. V

TT

of transmitting device must track V

REF

of receiving devices

Symbol Parameter

-6 -7

UnitsMin. Max. Min. Max.

T

PD1

Propagation delay single p-term - 5.7 - 6.7 ns

T

PD2

Propagation delay OR array - 6.0 - 7.5 ns

T

SUD

Direct input register clock setup time 2.6 - 3.0 - ns

T

SU1

Setup time (single p-term) 2.4 - 2.8 - ns

T

SU2

Setup time (OR array) 2.7 - 3.3 - ns

T

HD

Direct input register hold time 0 - 0 - ns

T

H

P-term hold time 0 - 0 - ns

T

CO

Clock to output - 4.5 - 6.0 ns

F

TOGGLE

(1)

Internal toggle rate - 450 - 300 MHz

F

SYSTEM1

(2)

Maximum system frequency - 256 - 152 MHz

F

SYSTEM2

(2)

Maximum system frequency - 238 - 141 MHz

F

EXT1

(3)

Maximum external frequency - 145 - 114 MHz

F

EXT2

(3)

Maximum external frequency - 139 - 108 MHz

T

PSUD

Direct input register p-term clock setup time 1.3 - 1.7 - ns