MARCH 28, 2017 3 1.8V TO 3.3V LVCMOS HIGH PERFORMANCE CLOCK BUFFER FAMILY

5PB11xx DATASHEET

Pin Assignments for DFN/QFN Packages

Pin Descriptions for DFN/QFN Packages

Output Logic Table

After at least three cycles of input clock toggling. Output Enable function is asynchronous to eliminate any intermediate incorrect output clock cycles during transition which may cause

frequency peaking to the downstream device.

Device Number

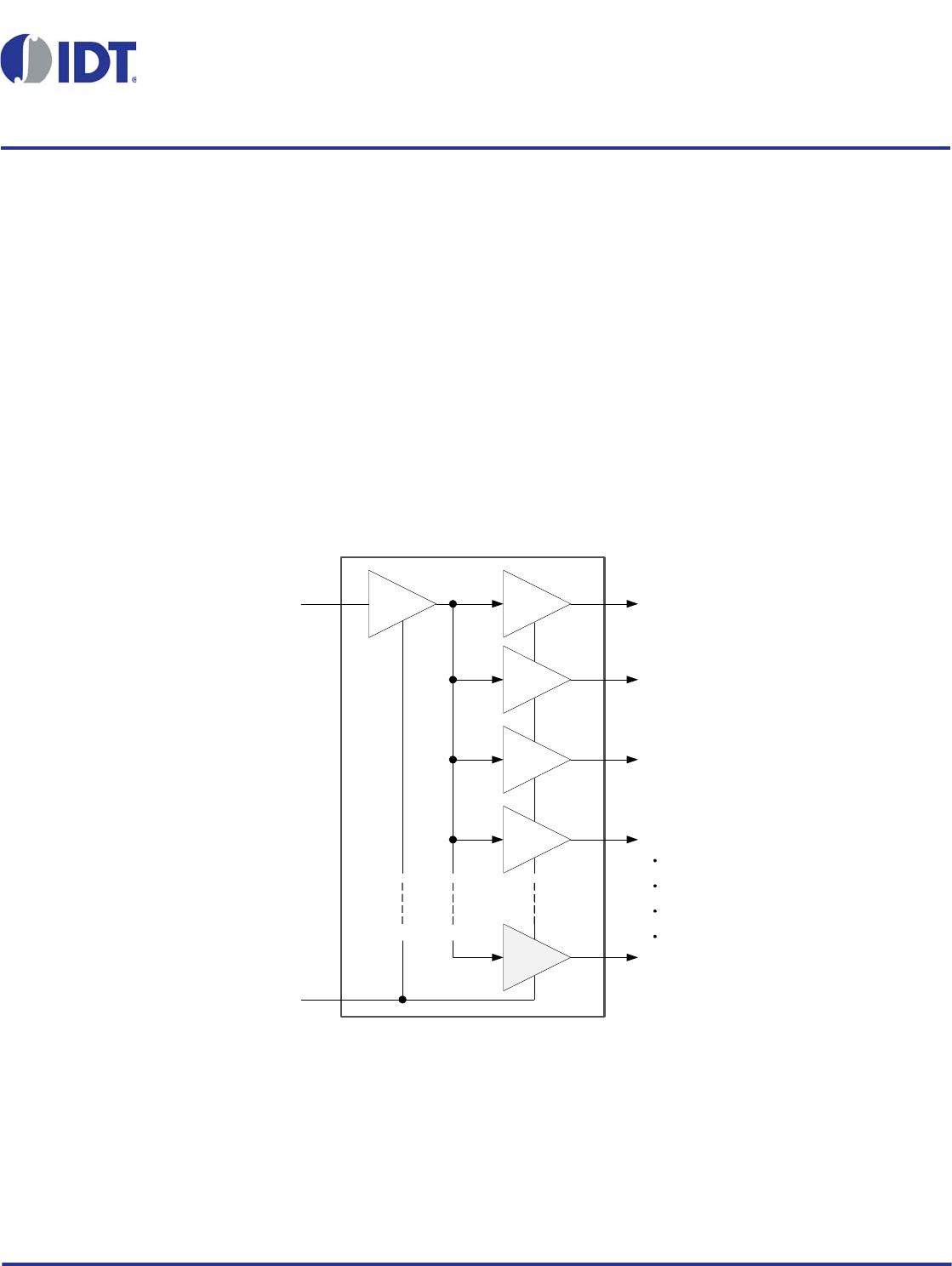

LVCMOS

Clock Input

Clock Output

Enable

LVCMOS Clock Output Supply Voltage Ground

CLKIN 1G Y0, Y1, . . . Y9 V

DD GND

5PB1102CMG 1 2 3, 8 6 4

5PB1104CMG 1 2 3, 5, 7, 8 6 4

5PB1106CMG 15 16 1, 4, 9, 11, 13, 14 3, 8, 12 2, 5, 10

5PB1108CMG 15 16 1, 4, 6, 7, 9, 11, 13, 14 3, 8, 12 2, 5, 10

5PB1110NDG 19 20 1, 4, 6, 8, 10, 11, 13, 15, 17, 18 3, 7, 12, 16 2, 5, 9, 14

Inputs Output

CLKIN 1G Yn

XLL

LHL

HHH

CLKIN

1

2

3

45

6

7

8

1G

Y0

GND

NC

VDD

NC

Y1

5PB1102CMG

CLKIN

1

2

3

45

6

7

8

1G

Y0

GND

Y2

VDD

Y3

Y1

5PB1104CMG

CLKIN

1

2

3

4

5

678

9

10

11

12

13

14

1516

1G

Y0

GND

VDD

Y4

GND

NC

Y5

VDD

Y2

GND

VDD

Y3

Y1

5PB1106CMG

NC

CLKIN

1

2

3

4

5

678

9

10

11

12

13

14

1516

1G

Y0

GND

VDD

Y4

GND

Y6

Y5

VDD

Y2

GND

VDD

Y3

Y1

5PB1108CMG

Y7

CLKIN

1

2

3

4

5

678910

11

12

13

14

15

1617181920

1G

Y0

GND

VDD

Y4

GND

Y6

VDD

Y9

GND

Y8

Y7

VDD

Y5

GND

Y2

VDD

Y3

Y1

5PB1110NDG