MAX6365–MAX6368

SOT23, Low-Power µP Supervisory Circuits

with Battery Backup and Chip-Enable Gating

_______________________________________________________________________________________ 9

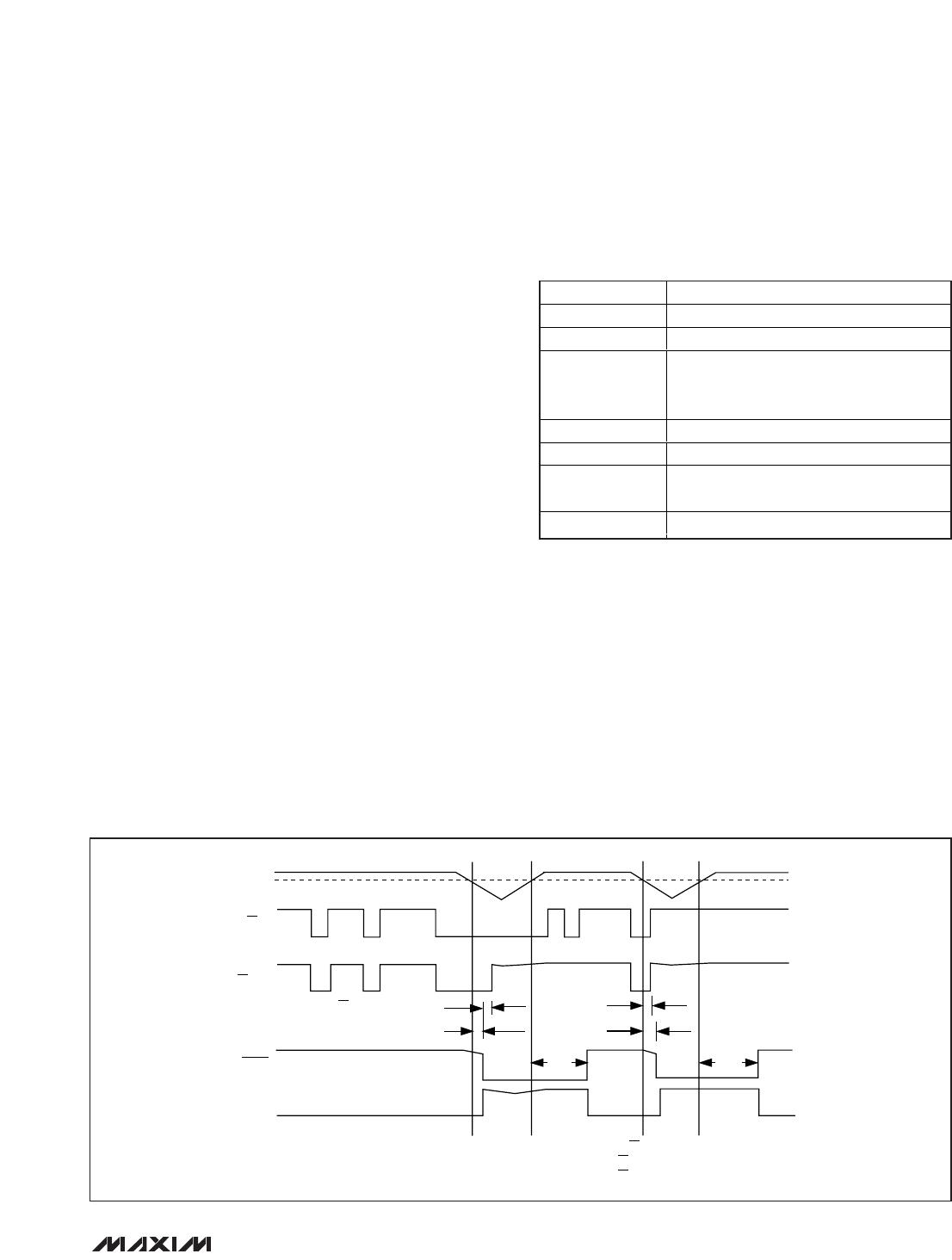

OUT goes high and stays high regardless of any sub-

sequent transitions on CE IN during the reset event.

When CE OUT is disconnected from CE IN, CE OUT is

actively pulled up to OUT.

The propagation delay through the chip-enable circuit-

ry depends on both the source impedance of the drive

to CE IN and the capacitive loading at CE OUT. The

chip-enable propagation delay is production tested

from the 50% point of CE IN to the 50% point of CE

OUT, using a 50Ω driver and 50pF load capacitance.

Minimize the capacitive load at CE OUT to minimize

propagation delay, and use a low-output-impedance

driver.

Backup-Battery Switchover

In a brownout or power failure, it may be necessary to

preserve the contents of the RAM. With a backup bat-

tery installed at BATT, the MAX6365–MAX6368 auto-

matically switch the RAM to backup power when V

CC

falls. The MAX6367 has a BATT ON output that goes

high in battery-backup mode. These devices require

two conditions before switching to battery-backup

mode:

1) V

CC

must be below the reset threshold.

2) V

CC

must be below V

BATT

.

Table 1 lists the status of the inputs and outputs in bat-

tery-backup mode. The devices do not power up if the

only voltage source is on BATT. OUT only powers up

from V

CC

at startup.

Manual Reset Input (MAX6365 Only)

Many µP-based products require manual reset capabili-

ty, allowing the user or external logic circuitry to initiate a

reset. For the MAX6365, a logic low on MR asserts reset.

Reset remains asserted while MR is low and for a mini-

mum of 150ms (t

RP

) after it returns high. MR has an inter-

nal 20kΩ pullup resistor to V

CC

. This input can be driven

with TTL/CMOS logic levels or with open-drain/collector

outputs. Connect a normally open momentary switch

from MR to GND to create a manual reset function; exter-

nal debounce circuitry is not required. If MR is driven

from long cables or the device is used in a noisy environ-

ment, connect a 0.1µF capacitor from MR to GND to pro-

vide additional noise immunity.

Figure 1. Reset and Chip-Enable Timing

CE IN GOES HIGH.

Connected to OUT. Current drawn from

= 0V.