ISL36111

8

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted

in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time

without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be

accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third

parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6974.2

July 19, 2012

For additional products, see www.intersil.com/product_tree

Products

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products

address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks.

Intersil's product families address power management and analog signal processing functions. Go to www.intersil.com/products

for a

complete list of Intersil product families.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on

intersil.com: ISL36111

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at http://rel.intersil.com/reports/search.php

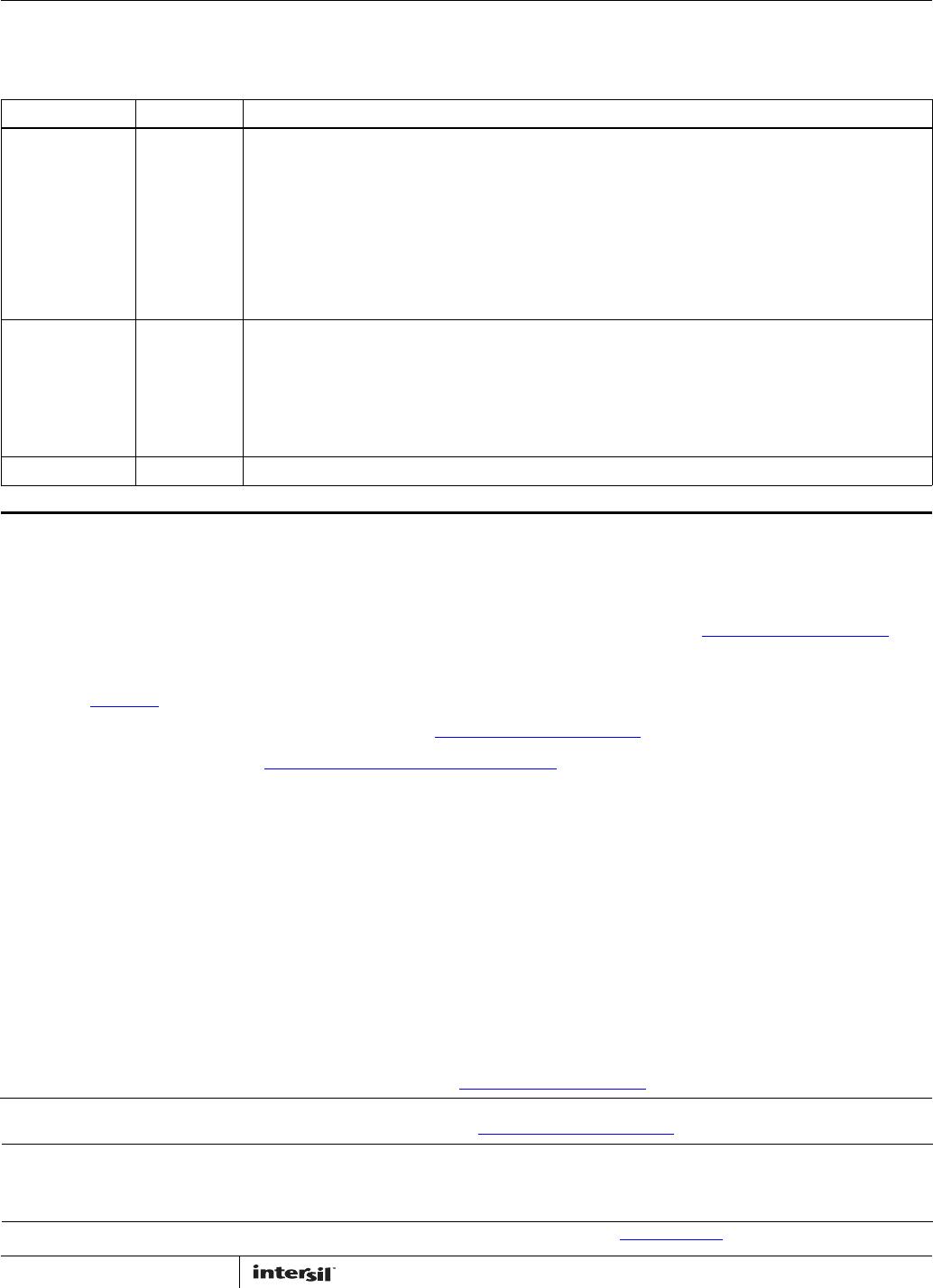

Revision History

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you

have the latest Rev.

DATE REVISION CHANGE

July 12, 2012 FN6974.2 On page 1, Column 1, changed last paragraph from:

"Operating on a single 1.2V power supply, the ISL36111 enables channel throughputs of 10Gb/s to 11.1Gb/s

while supporting lower data rates including 8.5, 6.25, 5, 4.25, 3.125 and 2.5Gb/s."

to:

"Operating on a single 1.2V power supply, the ISL36111 enables channel throughputs of 10Gb/s to 11.1Gb/s

while supporting lower data rates including 8.5, 6.25, 5, 4.25, 3.125, 2.5 and 1 Gb/s."

In “Electrical Specifications” on page 3 , changed Min Entry for “Bit Rate” from: "2.5Gb/s" to: "1Gb/s"

Added Note 14 to MIN and MAX columns of spec tables.

October 27, 2010 FN6974.1 1. Added “Application Information” on page 7, Figure 8 on page 7, and “PCB Layout Considerations” on page 7

2. Corrected “Pin Descriptions” on page 2 for VDD pin from "and 10nF decoupling capacitors.." to “and 47nF

decoupling capacitors.."

3. Corrected “Pin Descriptions” on page 2 for CP[A,B] pin from "Pins are read as a 3-digit number.." to "Pins are

read as a 2-digit number.."

November 19, 2009 FN6974.0 Initial Release to web