AMIS−49587

www.onsemi.com

11

4 ELECTRICAL CHARACTERISTICS

4.1 DC AND AC CHARACTERISTICS

4.1.1 Oscillator: Pin XIN, XOUT

In production the actual oscillation of the oscillator and duty cycle will not be tested. The production test will be based on the

static parameters and the inversion from XIN to XOUT in order to guarantee the functionality of the oscillator.

Table 8. OSCILLATOR

Parameter Test Conditions Symbol Min Typ Max Unit

Crystal frequency (Note 1) f

CLK

−100 ppm 24 +100 ppm MHz

Duty cycle with quartz connected (Note 1) 40 61 %

Start−up time (Note 1) T

startup

50 ms

Maximum Capacitive load on XOUT XIN used as clock input CL

XOUT

50 pF

Low input threshold voltage XIN used as clock input VIL

XOUT

0.3 V

DD

V

High input threshold voltage XIN used as clock input VIH

XOUT

0.7 V

DD

V

Low output voltage XIN used as clock input,

XOUT = 2 mA

VOL

XOUT

0.3 V

High input voltage XIN used as clock input VOH

XOUT

V

DD

−0.3 V

1. Guaranteed by design. Maximum allowed series loss resistance up to 80 W.

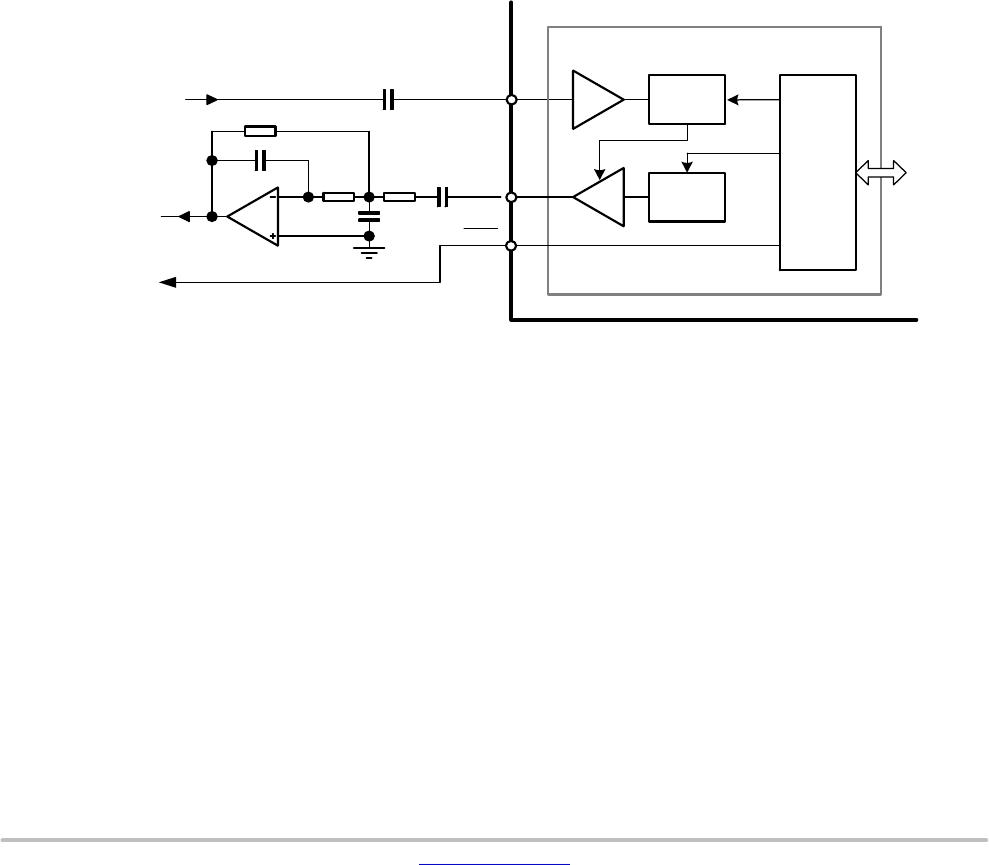

4.1.2 Zero Crossing Detector and 50/60 Hz PLL: Pin M50HZ_IN

Table 9. ZERO CROSSING DETECTOR AND 50/60 Hz PLL

Parameter Test Conditions Symbol Min Typ Max Unit

Maximum peak input current Imp

M50HZIN

−20 20 mA

Maximum average input current During 1 ms Imavg

M50HZIN

−2 2 mA

Mains voltage (ms) range With protection resistor at

M50HZIN

V

MAINS

90 550 V

Rising threshold level (Note 2) VIRM

50HZIN

1.9 V

Falling threshold level (Note 2) VIFM

50HZIN

0.82 V

Hysteresis (Note 2) VHY

50HZIN

0.4 V

Lock range for 50 Hz (Note 3) MAINS_FREQ = 0 (50 Hz) Flock

50Hz

45 55 Hz

Lock range for 60 Hz (Note 3) MAINS_FREQ = 0 (60 Hz) Flock

60Hz

54 66 Hz

Lock time (Note 3) MAINS_FREQ = 0 (50 Hz) Tlock

50Hz

15 s

Lock time (Note 3) MAINS_FREQ = 0 (60 Hz) Tlock

60Hz

20 s

Frequency variation without going out of

lock (Note 3)

MAINS_FREQ = 0 (50 Hz) DF

60Hz

0.1 Hz/s

Frequency variation without going out of

lock (Note 3)

MAINS_FREQ = 0 (60 Hz) DF

50Hz

0.1 Hz/s

Jitter of CHIP_CLK (Note 3) Jitter

CHIP_CLK

−25 25

ms

2. Measured relative to V

SS

.

3. These parameters will not be measured in production since the performance is totally dependent of a digital circuit which will be guaranteed

by the digital test patterns.