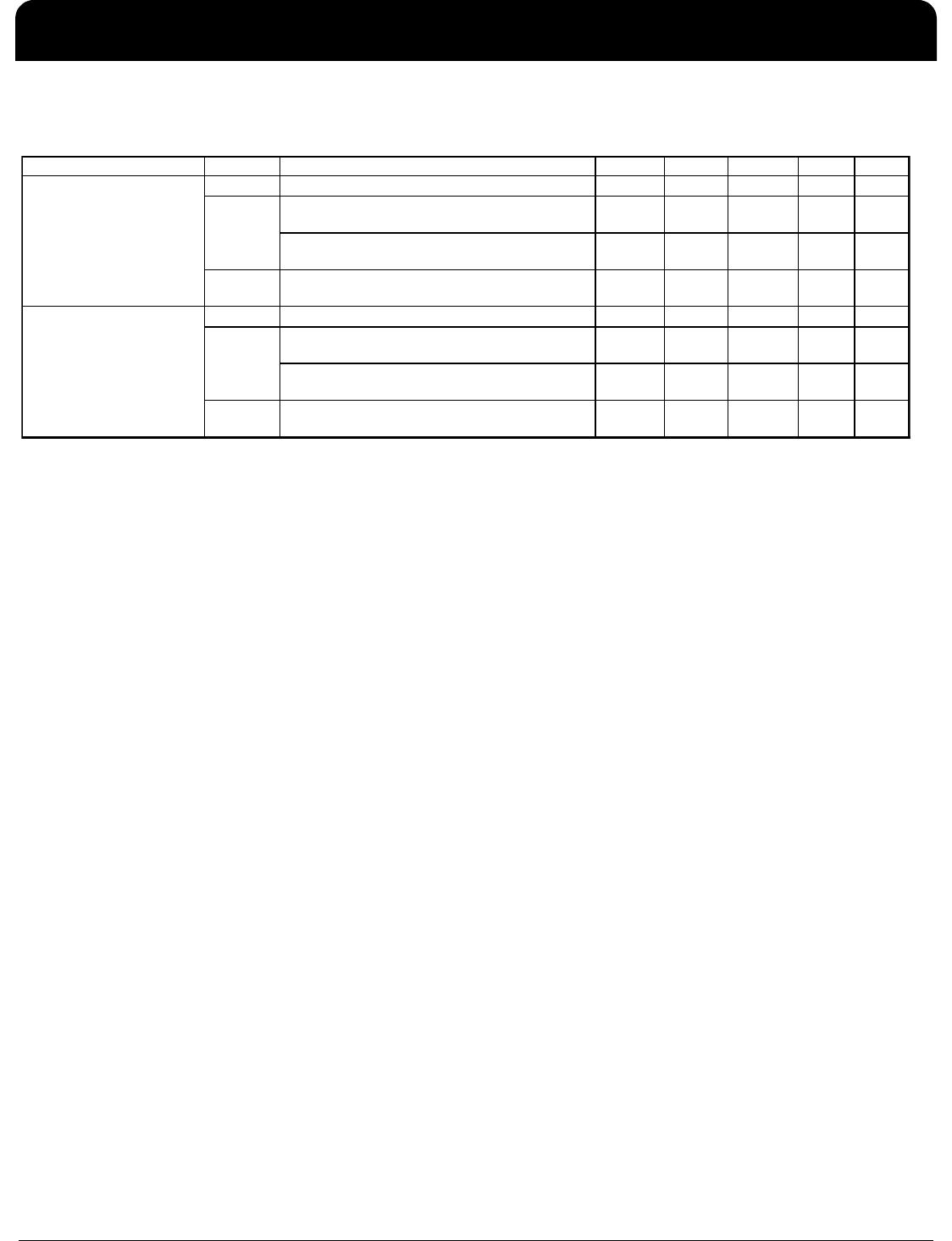

Common Recommendations for Differential Routing Dimension or Value Unit Figure

L1 length, route as non-coupled 50ohm trace 0.5 max inch 1

L2 length, route as non-coupled 50ohm trace 0.2 max inch 1

L3 length, route as non-coupled 50ohm trace 0.2 max inch 1

Rs 33 ohm 1

Rt 49.9 ohm 1

Down Device Differential Routing

L4 length, route as coupled microstrip 100ohm differential trace 2 min to 16 max inch 1

L4 length, route as coupled stripline 100ohm differential trace 1.8 min to 14.4 max inch 1

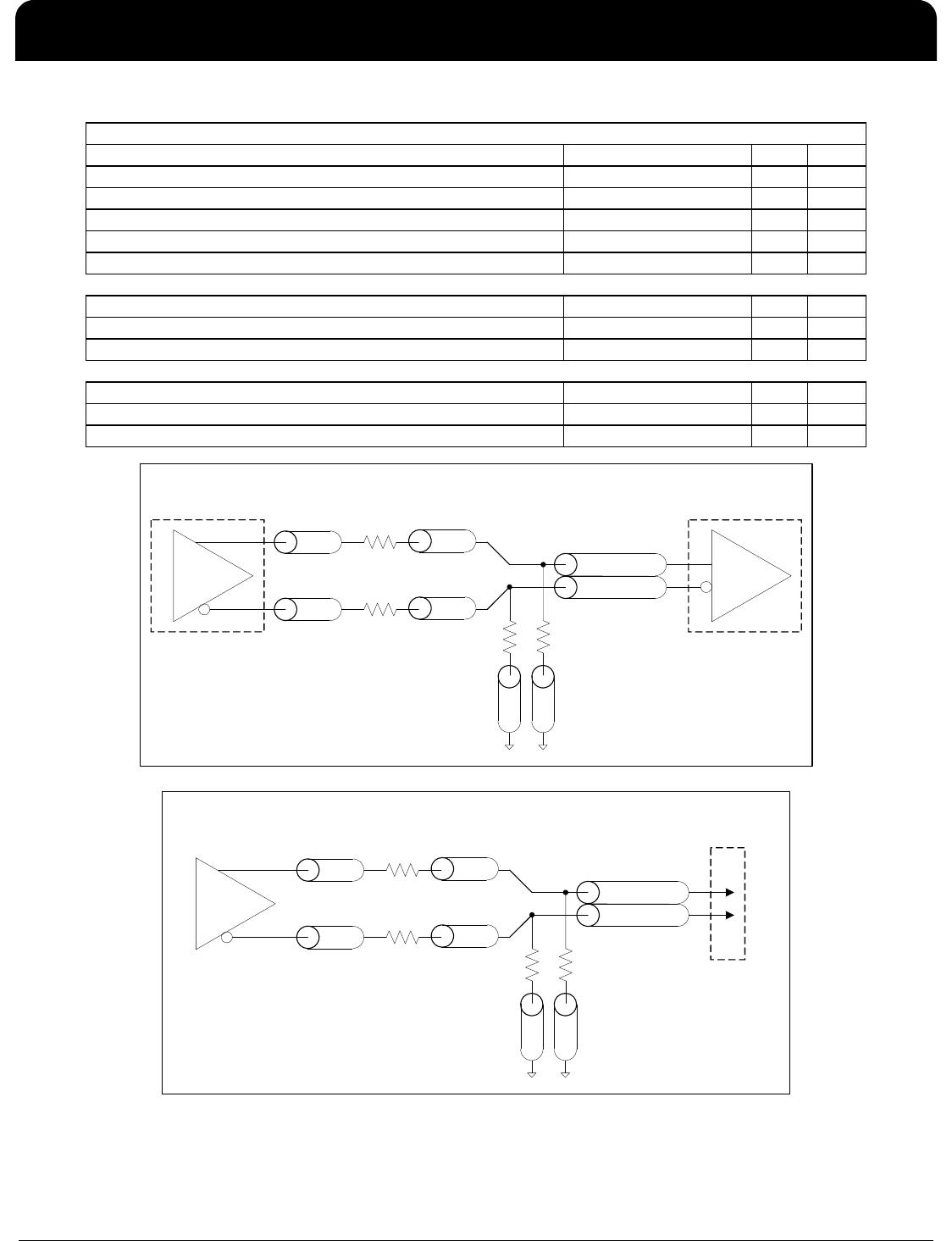

Differential Routing to PCI Express Connector

L4 length, route as coupled microstrip 100ohm differential trace 0.25 to 14 max inch 2

L4 length, route as coupled stripline 100ohm differential trace 0.225 min to 12.6 max inch 2

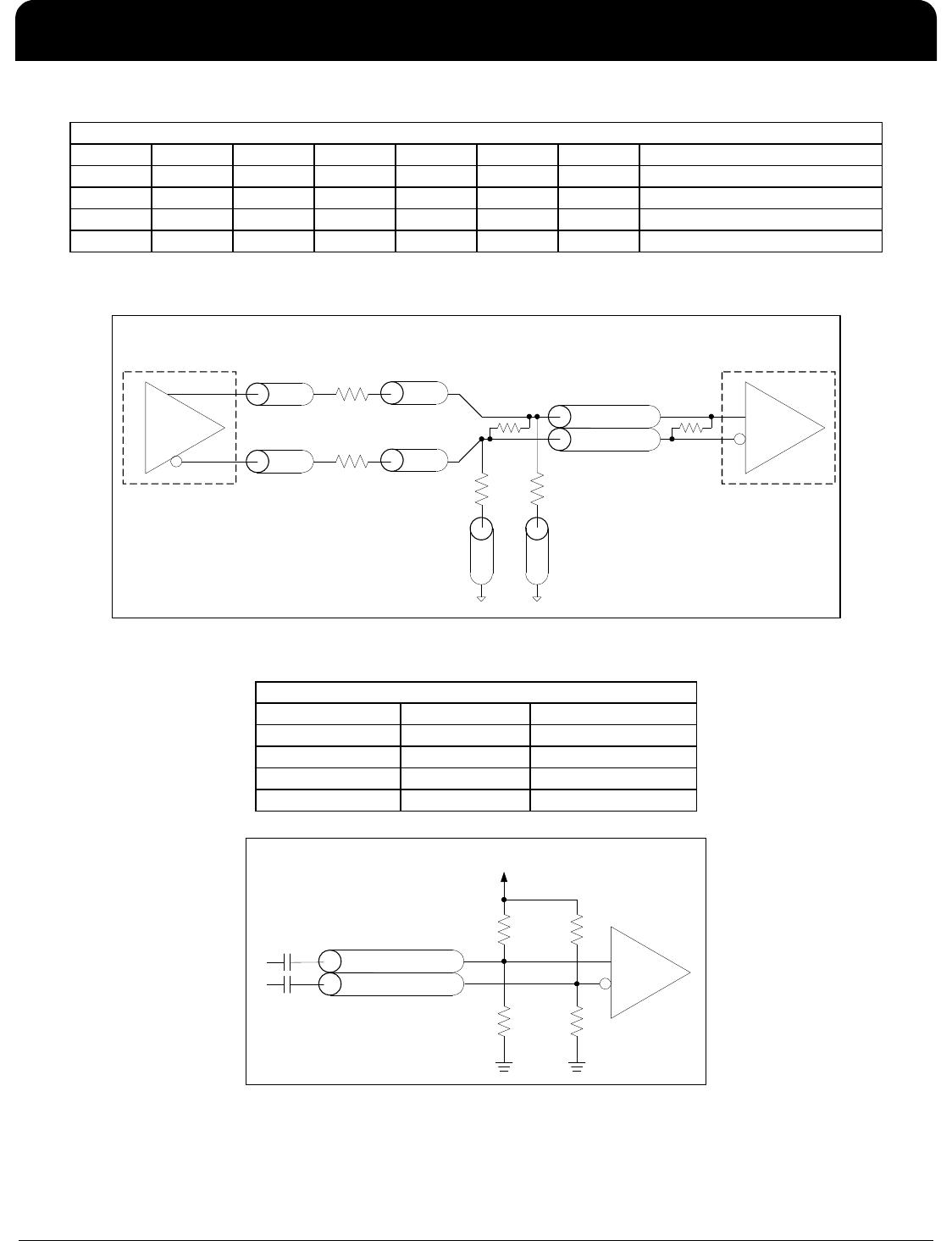

SRC Reference Clock