NCP1082

http://onsemi.com

5

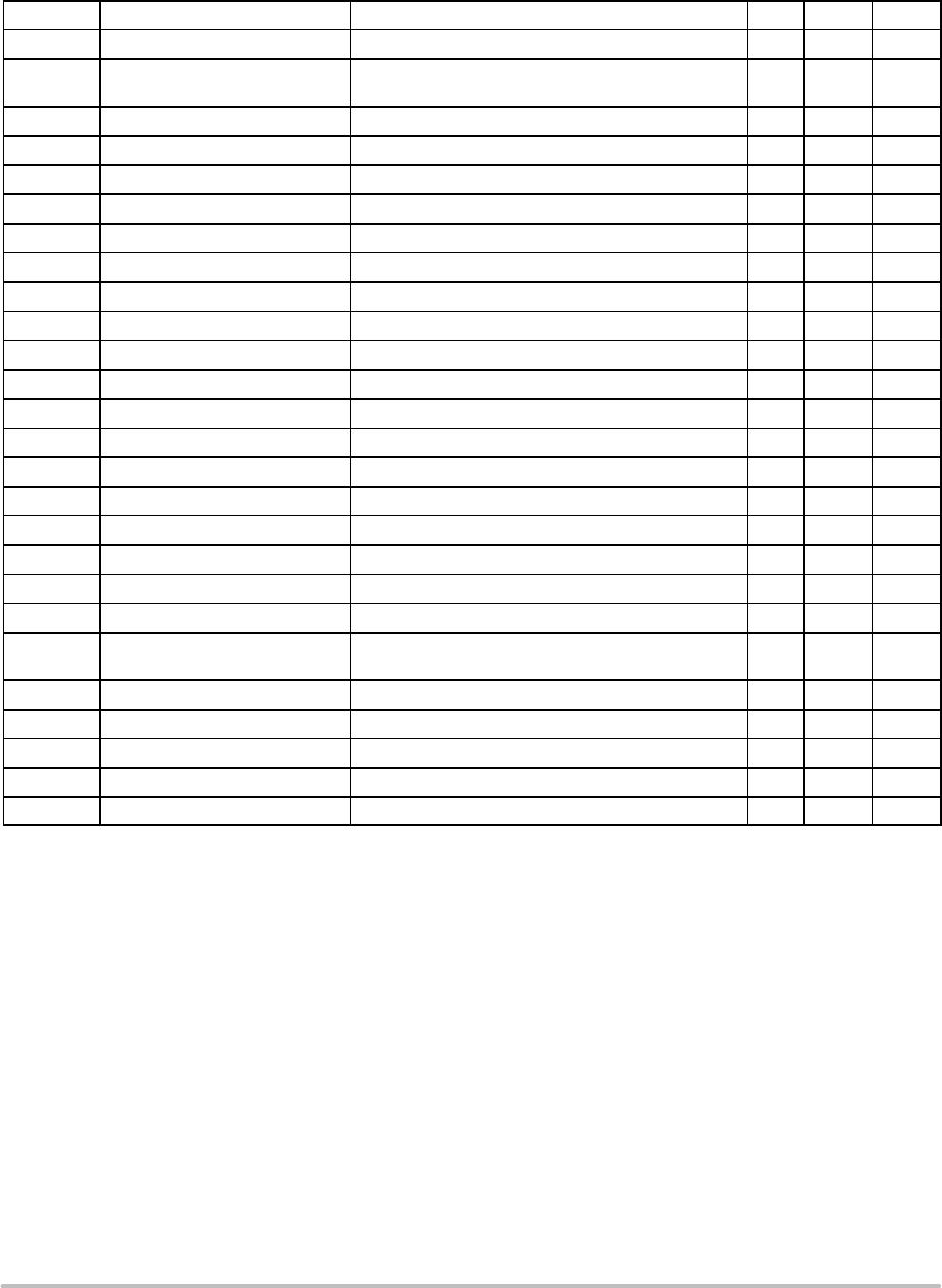

Table 1. PIN DESCRIPTIONS

Name Pin No. Type Description

VPORTP 1 Supply Positive input power. Voltage with respect to VPORTN

1,2

VPORTN1

VPORTN2

6,8 Ground Negative input power. Connected to the source of the internal pass−switch.

RTN 7 Ground DC−DC controller power return. Connected to the drain of the internal pass−switch. It must

be connected to ARTN. This pin is also the drain of the internal pass−switch.

ARTN 14 Ground DC−DC controller ground pin. Must be connected to RTN as a single point ground connection

for improved noise immunity.

VDDH 16 Supply Output of the 9 V LDO internal regulator. Voltage with respect to ARTN. Supplies the internal

gate driver. VDDH must be bypassed to ARTN with a 1 mF or 2.2 mF ceramic capacitor with

low ESR.

VDDL 17 Supply Output of the 3.3 V LDO internal regulator. Voltage with respect to ARTN. This pin can be

used to bias an external low−power LED (1 mA max.) connected to ARTN, and can also be

used to add extra biasing current in the external opto−coupler. VDDL must be bypassed to

ARTN with a 330 nF or 470 nF ceramic capacitor with low ESR.

CLASS 2 Input Classification current programming pin. Connect a resistor between CLASS and VPORTN

1,2

.

INRUSH 4 Input Inrush current limit programming pin. Connect a resistor between INRUSH and VPORTN

1,2

.

ILIM1 5 Input Operational current limit programming pin. Connect a resistor between ILIM1 and

VPORTN

1,2

.

UVLO 3 Input DC−DC controller under−voltage lockout input. Voltage with respect to VPORTN

1,2

. Connect

a resistor−divider from VPORTP to UVLO to VPORTN

1,2

to set an external UVLO threshold.

GATE 15 Output DC−DC controller gate driver output pin.

OSC 11 Input Internal oscillator frequency programming pin. Connect a resistor between OSC and ARTN.

NC 13 No connect pin, must not be connected.

COMP 18 I/O Output of the internal error amplifier of the DC−DC controller. COMP is pulled−up internally to

VDDL with a 5 kW resistor. In isolated applications, COMP is connected to the collector of the

opto−coupler. Voltage with respect to ARTN.

FB 19 Input DC−DC controller inverting input of the internal error amplifier. In isolated applications, the pin

should be strapped to ARTN to disable the internal error amplifier.

CS 12 Input Current−sense input for the DC−DC controller. Voltage with respect to ARTN.

SS 20 Input Soft−start input for the DC−DC controller. A capacitor between SS and ARTN determines the

soft−start timing.

AUX 9 Input When the pin is pulled up, the IEEE detection mode is disabled and the device can be sup-

plied by an auxiliary supply. Voltage with respect to VPORTN

1,2

. Connect the pin to the auxili-

ary supply through a resistor divider.

TEST 10 Input Digital test pin must always be connected to VPORTN

1,2

.

EP Exposed pad. Connected to VPORTN

1,2

ground.