9

LTC1416

APPLICATIONS INFORMATION

WUU

U

difference frequencies of mfa ± nfb, where m and n = 0, 1,

2, 3, etc. For example, the 2nd order IMD terms include (fa

+ fb). If the two input sine waves are equal in magnitude,

the value (in decibels) of the 2nd order IMD products can

be expressed by the following formula:

IMD fa fb+

()

=

()

20 log

Amplitude at fa+ fb

Amplitude at fa

Total Harmonic Distortion

Total Harmonic Distortion (THD) is the ratio of the RMS

sum of all harmonics of the input signal to the fundamental

itself. The out-of-band harmonics alias into the frequency

band between DC and half the sampling frequency. THD is

expressed as:

THD

VV Vn

V

=

+++

20 log

V2

2

34

1

22 2

...

where V1 is the RMS amplitude of the fundamental fre-

quency and V2 through Vn are the amplitudes of the

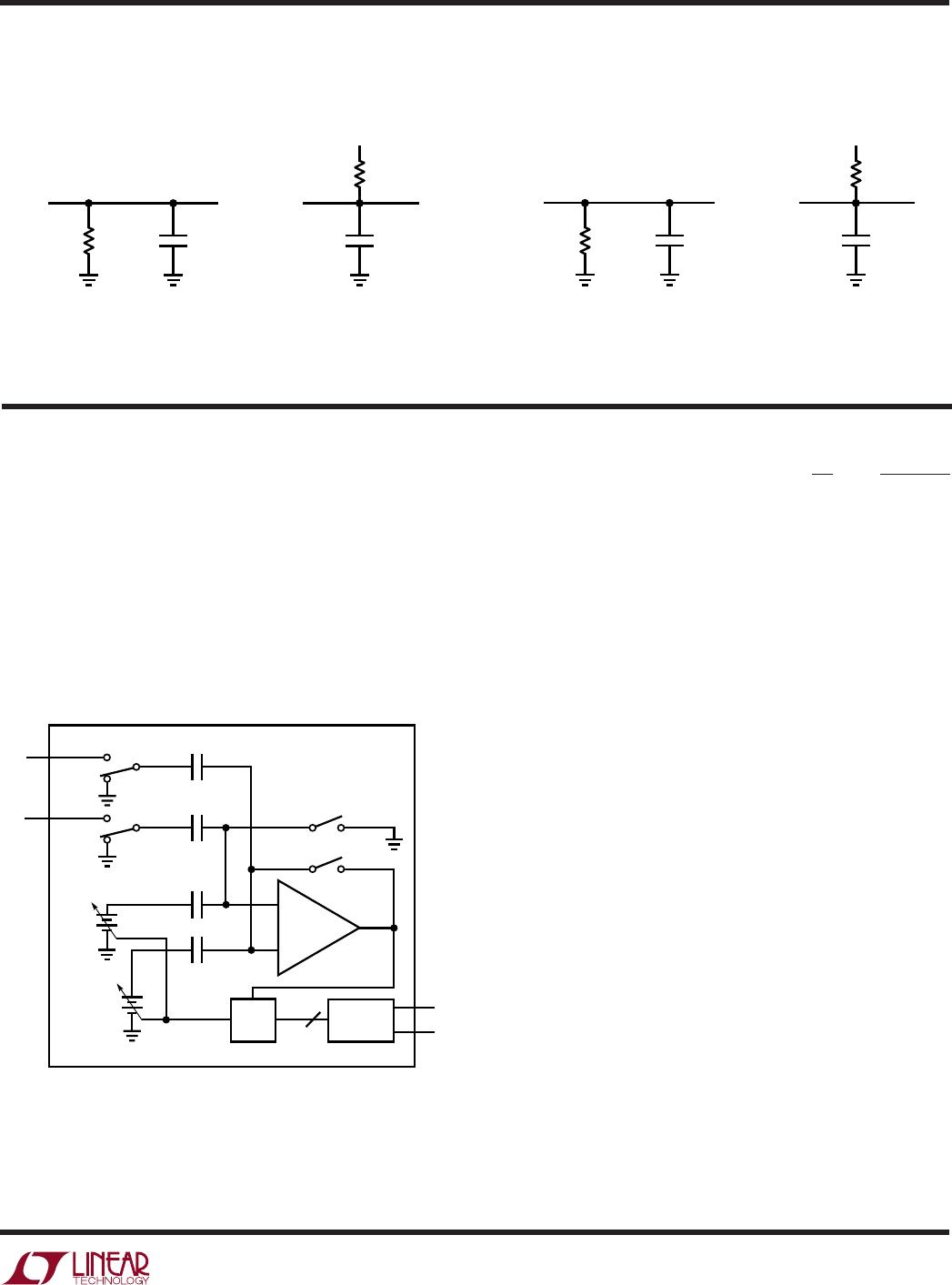

second through Nth harmonics. THD versus input fre-

quency is shown in Figure 4. The LTC1416 has good

distortion performance up to the Nyquist frequency and

beyond.

INPUT FREQUENCY (Hz)

1k

AMPLITUDE (dB BELOW THE FUNDAMENTAL)

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

10k 100k

1416 G03

1M 2M

THD

2ND

3RD

Figure 4. Distortion vs Input Frequency

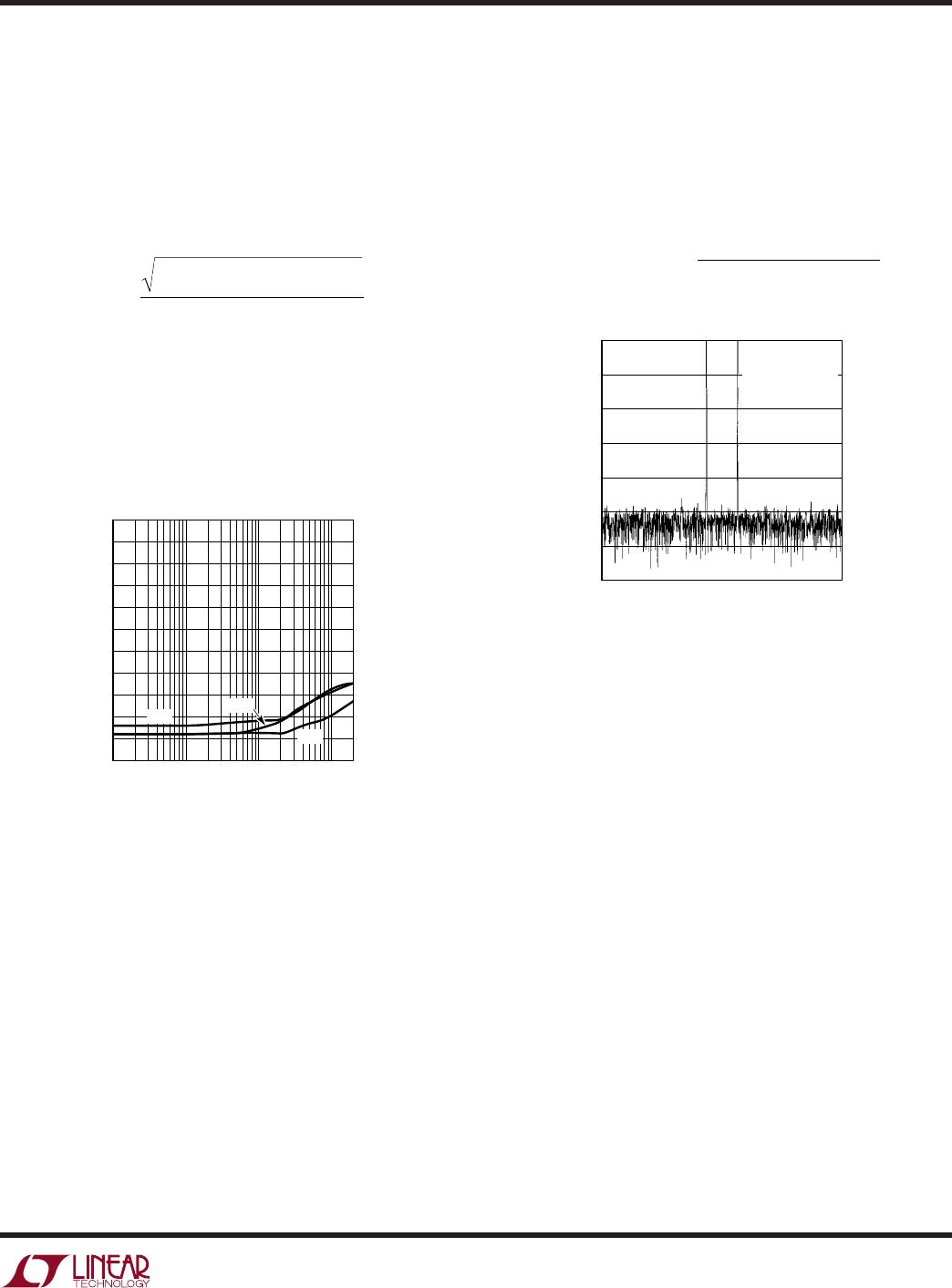

Intermodulation Distortion

If the ADC input signal consists of more than one spectral

component, the ADC transfer function nonlinearity can

produce intermodulation distortion (IMD) in addition to

THD. IMD is the change in one sinusoidal input caused by

the presence of another sinusoidal input at a different

frequency.

If two pure sine waves of frequencies fa and fb are applied

to the ADC input, nonlinearities in the ADC transfer

function can create distortion products at the sum and

FREQUENCY (Hz)

0

AMPLITUDE (dB)

0

–20

–40

–60

–80

–100

–120

–140

20

100

140

1416 G05

80

180

200

40

60

120 160

f

SAMPLE

= 400kHz

f

a

=87.01171876kHz

f

b

=113.1835938kHz

Figure 5. Intermodulation Distortion Plot

Peak Harmonic or Spurious Noise

The peak harmonic or spurious noise is the largest spec-

tral component excluding the input signal and DC. This

value is expressed in decibels relative to the RMS value of

a full-scale input signal.

Full-Power and Full-Linear Bandwidth

The full-power bandwidth is that input frequency at which

the amplitude of the reconstructed fundamental is

reduced by 3dB for a full-scale input signal. The full-linear

bandwidth is the input frequency at which the S/(N + D)

has dropped to 77dB (12.5 effective bits). The LTC1416

has been designed to optimize input bandwidth, allowing

the ADC to undersample input signals with frequencies

above the converter’s Nyquist frequency. The noise floor

stays very low at high frequencies; S/(N + D) becomes

dominated by distortion at frequencies far beyond Nyquist.