LTC6820

8

6820fb

For more information www.linear.com/LTC6820

PIN FUNCTIONS

(QFN/MSOP)

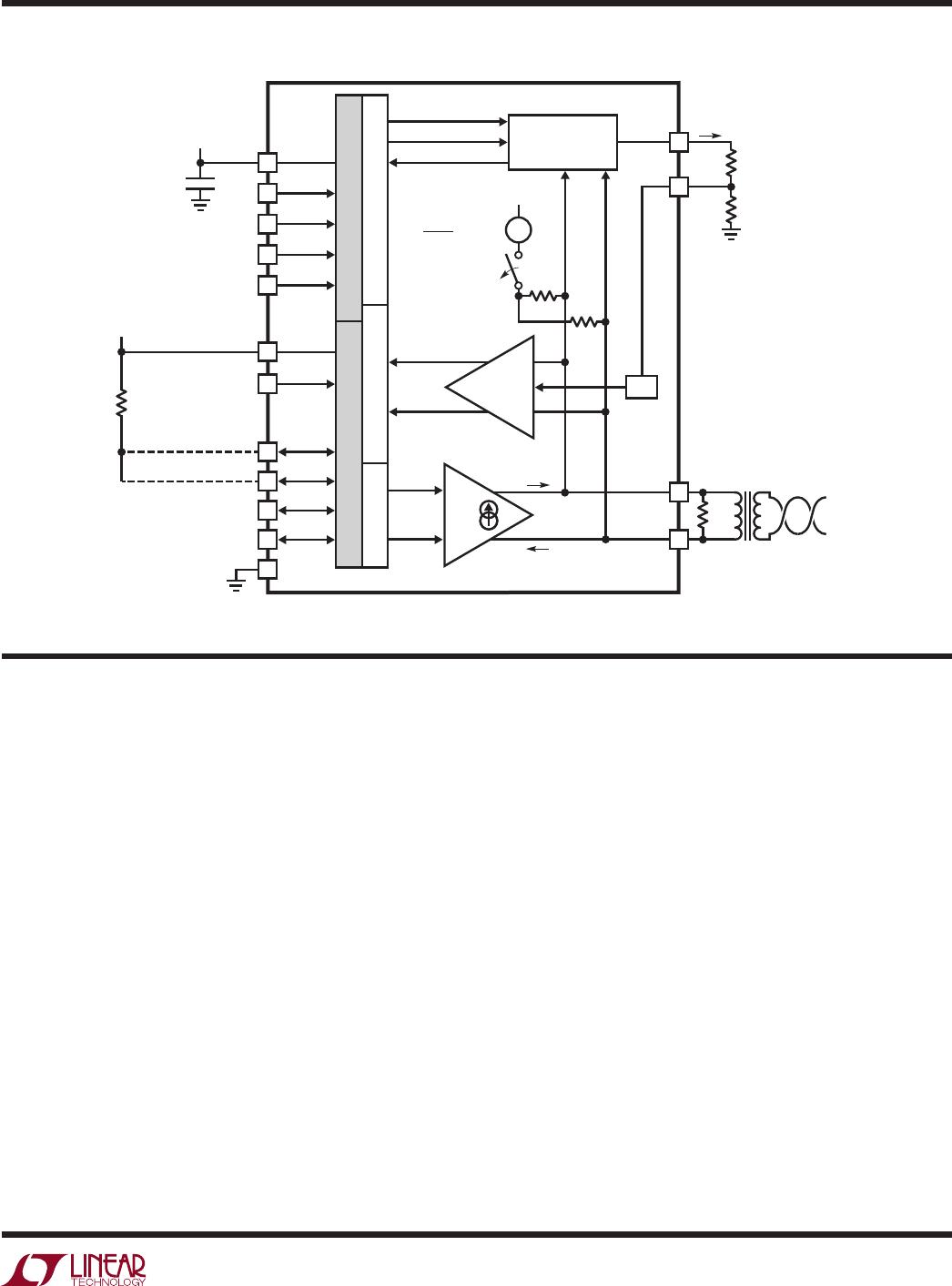

MOSI (Pin 1/Pin 2): SPI Master Out/Slave In Data. If

connected on the master side of a SPI interface (MSTR

pin high), this pin receives the data signal output from

the master SPI controller. If connected on the slave side

of the interface (MSTR pin low), this pin drives the data

signal input to the slave SPI device. The output is open

drain, so an external pull-up resistor to V

DDS

is required.

MISO (Pin 2/Pin 3): SPI Master In/Slave Out Data. If con-

nected on the master side of a SPI interface (MSTR pin

high), this pin drives the data signal input to the master SPI

controller

. If

connected on the slave side of the interface

(MSTR pin low), this pin receives the data signal output

from the slave SPI device. The output is open drain, so

an external pull-up resistor to V

DDS

is required.

SCK (Pin 3/Pin 4): SPI Clock Input/Output. If connected on

the master side of the interface (MSTR pin high), this pin

receives the clock signal from the master SPI controller.

This input should not be pulled above V

DDS

. If connected

on the slave side of the interface (MSTR pin low), this pin

outputs the clock signal to the slave device. The output

driver is push-pull; no external pull-up resistor is needed.

CS (Pin 4/Pin 5): SPI Chip Select Input/Output. If connected

on the master side of the interface (MSTR pin high), this

pin receives the chip select signal from the master SPI

controller. This input should not be pulled above V

DDS

. If

connected on the slave side of the interface (MSTR pin

low), this pin outputs the chip select signal to the slave

device. The output driver is push-pull; no external pull-up

resistor is needed.

V

DDS

(Pin 5/Pin 6): SPI Input/Output Power Supply Input.

The output drivers for the SCK and CS pins use the V

DDS

input as their positive power supply. The input threshold

voltages of SCK, CS, MOSI, MISO and EN are determined

by V

DDS

. May be tied to V

DD

or to a supply above or below

V

DD

to level shift the SPI I/O. If separate from V

DD

, con-

nect a bypass capacitor of at least 0.01μF directly between

V

DDS

and GND.

POL (Pin 6/Pin 7): SPI Clock Polarity Input. Tie to V

DD

or

GND. See Operation section for details.

PHA (Pin 7/Pin 8): SPI Clock Phase Input. Tie to V

DD

or

GND. See Operation section for details.

V

DD

(Pin 8/Pin 9): Device Power Supply Input. Connect

a bypass capacitor of at least 0.01μF directly between

V

DD

and GND.

IM (Pin 9/Pin 10): Isolated Interface Minus Input/Output.

IP (Pin 10/Pin 11): Isolated Interface Plus Input/Output.

MSTR (Pin 11/Pin 12): Serial Interface Master/Slave

Selector Input. Tie this pin to V

DD

if the device is on the

master side of the isolated interface. Tie this pin to GND

if the device is on the slave side of the isolated interface.

SLOW (Pin 12/Pin 13): Slow Interface Selection Input. For

clock frequencies at or below 200kHz, or if slave devices

cannot meet timing requirements, this pin should be tied

to V

DD

. For clock frequencies above 200kHz, this pin

should be tied to GND.

GND (Pin 13/Pin 14): Device Ground.

ICMP (Pin 14/Pin 15): Isolated Interface Comparator

Voltage Threshold Set. Tie this pin to the resistor divider

between IBIAS and GND to set the voltage threshold of the

interface receiver comparators. The comparator thresholds

are set to 1/2 the voltage on the ICMP pin.

IBIAS (Pin 15/Pin 16): Isolated Interface Current Bias.

Tie IBIAS to GND through a resistor divider to set the

interface output current level. When the device is enabled,

this pin is approximately 2V. When transmitting pulses,

the sink current on each of the IP and IM pins is set to

20 times the current sourced from pin IBIAS to GND.

Limit the capacitance on the IBIAS pin to less than 50pF

to maintain the stability of the feedback circuit regulating

the IBIAS voltage.

EN (Pin 16/Pin 1): Device Enable Input. If high, this pin

forces the LTC6820 to stay enabled, overriding the internal

IDLE mode function. If low, the LTC6820 will go into IDLE

mode after the CS pin has been high for 5.7ms (when

MSTR pin is high) or after no signal on the IP/IM pins for

5.7ms (when MSTR pin is low). The LTC6820 will wake-up

less than 8µs after CS falls (MSTR high) or after a signal

is detected on IP/IM (MSTR low).

Exposed Pad (Pin 17, QFN Package Only): Exposed pad

may be left open or connected to device GND.