REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

a

AD7741/AD7742

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

Single and Multichannel, Synchronous

Voltage-to-Frequency Converters

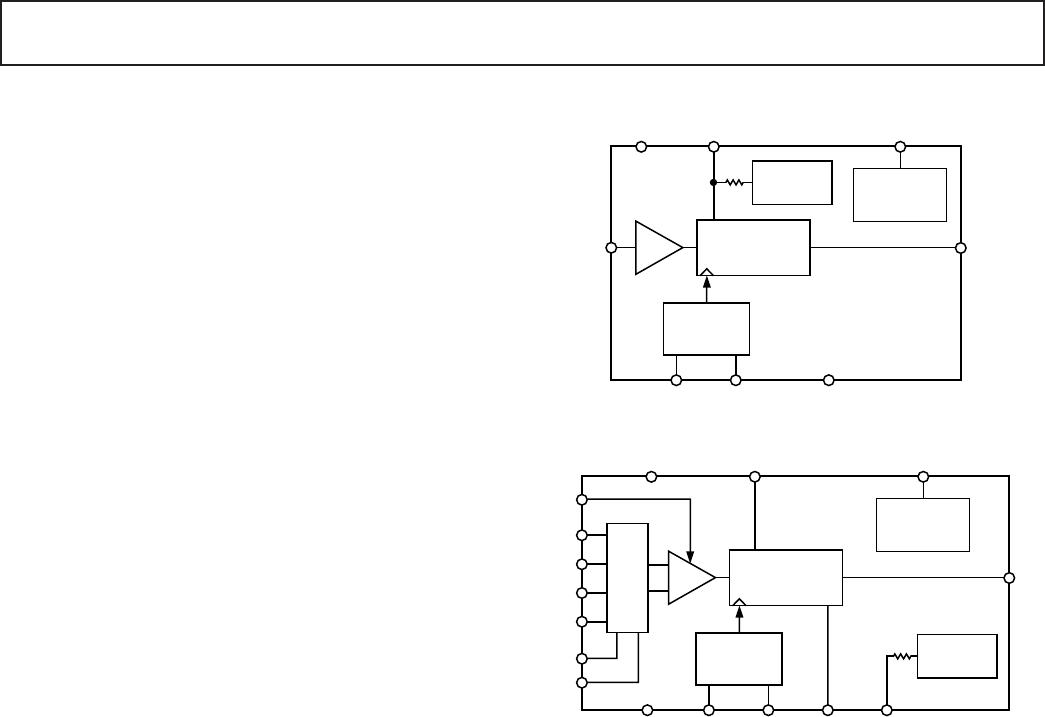

FUNCTIONAL BLOCK DIAGRAMS

X1

VOLTAGE-TO-

FREQUENCY

MODULATOR

CLOCK

GENERATION

CLKIN CLKOUT

GND

V

IN

POWER-DOWN

LOGIC

PDREFIN/OUT

V

DD

f

OUT

AD7741

+2.5V

REFERENCE

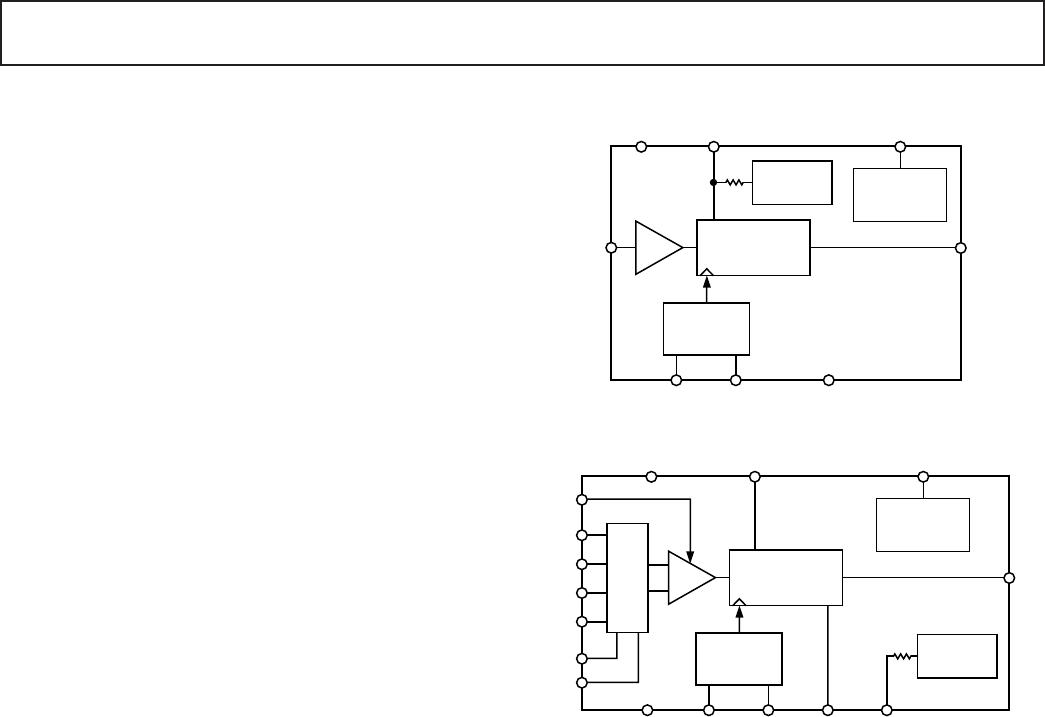

X1/X2

INPUT

MUX

VOLTAGE-TO-

FREQUENCY

MODULATOR

REFIN

+2.5V

REFERENCE

REFOUT

CLOCK

GENERATION

CLKIN CLKOUT

GND

GAIN

V

IN

1

A1

A0

V

IN

2

V

IN

3

V

IN

4

POWER-DOWN

LOGIC

PDUNI/BIP

V

DD

f

OUT

AD7742

FEATURES

AD7741: One Single-Ended Input Channel

AD7742: Two Differential or Three Pseudo-Differential

Input Channels

Integral Nonlinearity of 0.012% at f

OUT

(Max) = 2.75 MHz

(AD7742) and at f

OUT

(Max) = 1.35 MHz (AD7741)

Single +5 V Supply Operation

Buffered Inputs

Programmable Gain Analog Front-End

On-Chip +2.5 V Reference

Internal/External Reference Option

Power Down to 35 A Max

Minimal External Components Required

8-Lead and 16-Lead DIP and SOIC Packages

APPLICATIONS

Low Cost Analog-to-Digital Conversion

Signal Isolation

GENERAL DESCRIPTION

The AD7741/AD7742 are a new generation of synchronous

voltage-to-frequency converters (VFCs). The AD7741 is a

single-channel version in an 8-lead package (SOIC/DIP) and the

AD7742 is a multichannel version in a 16-lead package (SOIC/

DIP). No user trimming is required to achieve the specified

performance.

The AD7741 has a single buffered input whereas the AD7742

has four buffered inputs that may be configured as two fully-

differential inputs or three pseudo-differential inputs. Both parts

include an on-chip +2.5 V bandgap reference that provides the

user with the option of using this internal reference or an exter-

nal reference.

The AD7741 has a single-ended voltage input range from 0 V

to REFIN. The AD7742 has a differential voltage input range

from –V

REF

to +V

REF

. Both parts operate from a single +5 V

supply consuming typically 6 mA, and also contain a power-

down feature that reduces the current consumption to less than

35 µA.