REV. 0

AD7741/AD7742

–4–

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although the AD7741/AD7742 features proprietary ESD protection circuitry, permanent dam-

age may occur on devices subjected to high energy electrostatic discharges. Therefore, proper

ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

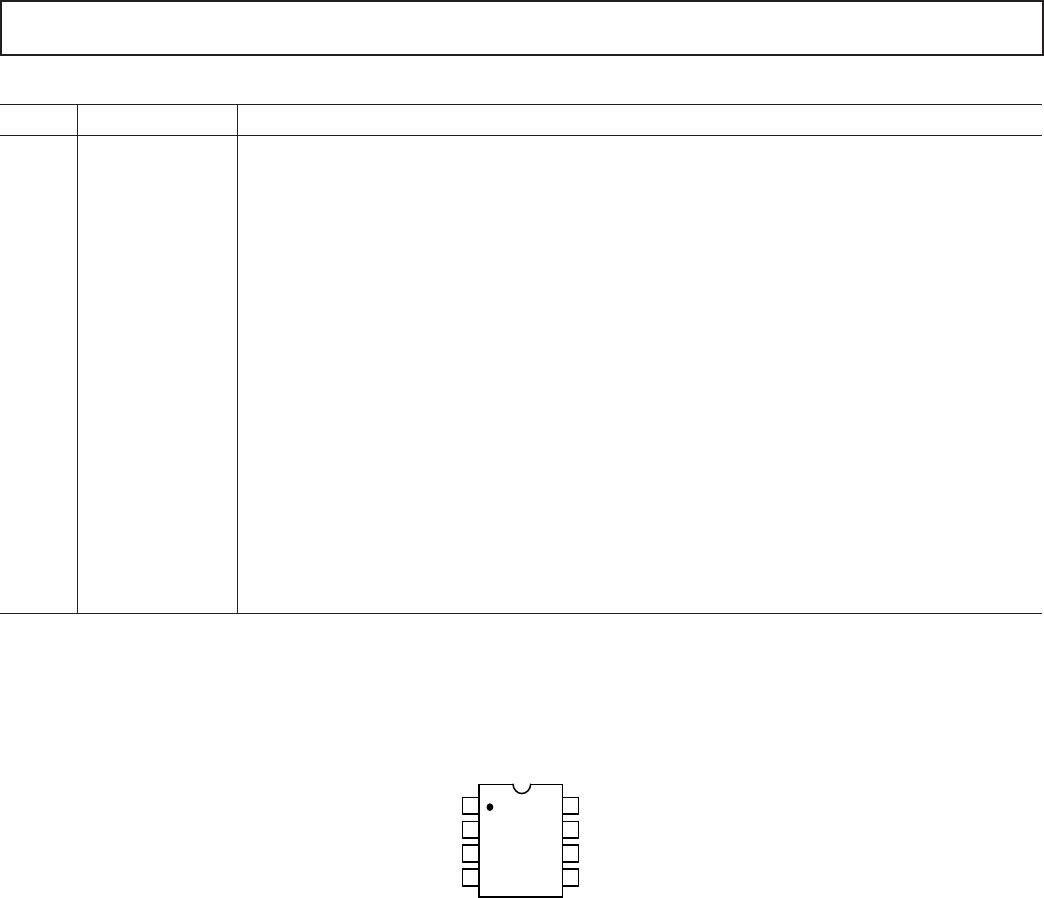

TIMING CHARACTERISTICS

1, 2, 3

Limit at T

MIN

, T

MAX

Parameter (B and Y Version) Units Conditions/Comments

f

CLKIN

6.144 MHz max

t

HIGH

/t

LOW

55/45 max Input Clock Mark/Space Ratio

45/55 min

t

1

9 ns typ f

CLOCK

Rising Edge to f

OUT

Rising Edge

t

2

4 ns typ f

OUT

Rise Time

t

3

4 ns typ f

OUT

Fall Time

t

4

t

HIGH

± 5 ns typ f

OUT

Pulsewidth

NOTES

1

Guaranteed by design and characterization, not production tested.

2

All input signals are specified with tr = tf = 5 ns (10% to 90% of V

DD

) and timed from a voltage level of (V

IL

+ V

IH

)/2.

3

See Figure 1.

Specifications subject to change without notice.

(V

DD

= +4.75 V to +5.25 V; V

REF

= +2.5 V. All specifications T

MIN

to T

MAX

unless otherwise noted.)

ABSOLUTE MAXIMUM RATINGS

1, 2

(T

A

= +25°C unless otherwise noted)

V

DD

to GND . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3␣ V to +7 V

Analog Input Voltage to GND . . . . . . . . –5␣ V to V

DD

+ 0.3 V

Digital Input Voltage to GND . . . . . . . –0.3␣ V to V

DD

+ 0.3 V

Reference Input Voltage to GND . . . . –0.3 V to V

DD

+ 0.3 V

f

OUT

to GND . . . . . . . . . . . . . . . . . . . . –0.3 V to V

DD

+ 0.3 V

Operating Temperature Range

Automotive (Y Version) . . . . . . . . . . . . . . –40°C to +105°C

Industrial (B Version) . . . . . . . . . . . . . . . . –40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Plastic DIP Package

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . 450 mW

θ

JA

Thermal Impedance (8 Lead) . . . . . . . . . . . . . 125°C/W

θ

JA

Thermal Impedance (16 Lead) . . . . . . . . . . . . 117°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

SOIC Package

Power Dissipation . . . . . . . . . . . . . . . . . . . . . . . . . 450 mW

θ

JA

Thermal Impedance (8 Lead) . . . . . . . . . . . . . 157°C/W

θ

JA

Thermal Impedance (16 Lead) . . . . . . . . . . . . 125°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Transient currents of up to 100 mA will not cause SCR latch-up.

ORDERING GUIDE

Temperature Package Package

Models Ranges Descriptions Options

AD7741BN –40°C to +85°C Plastic DIP N-8

AD7741BR –40°C to +85°C Small Outline R-8

AD7741YR –40°C to +105°C Small Outline R-8

AD7742BN –40°C to +85°C Plastic DIP N-16

AD7742BR –40°C to +85°C Small Outline R-16A

AD7742YR –40°C to +105°C Small Outline R-16A

CLKIN

f

OUT

t

HIGH

t

4

t

1

t

2

t

3

Figure 1. Timing Diagram