2

FN8222.3

July 20, 2009

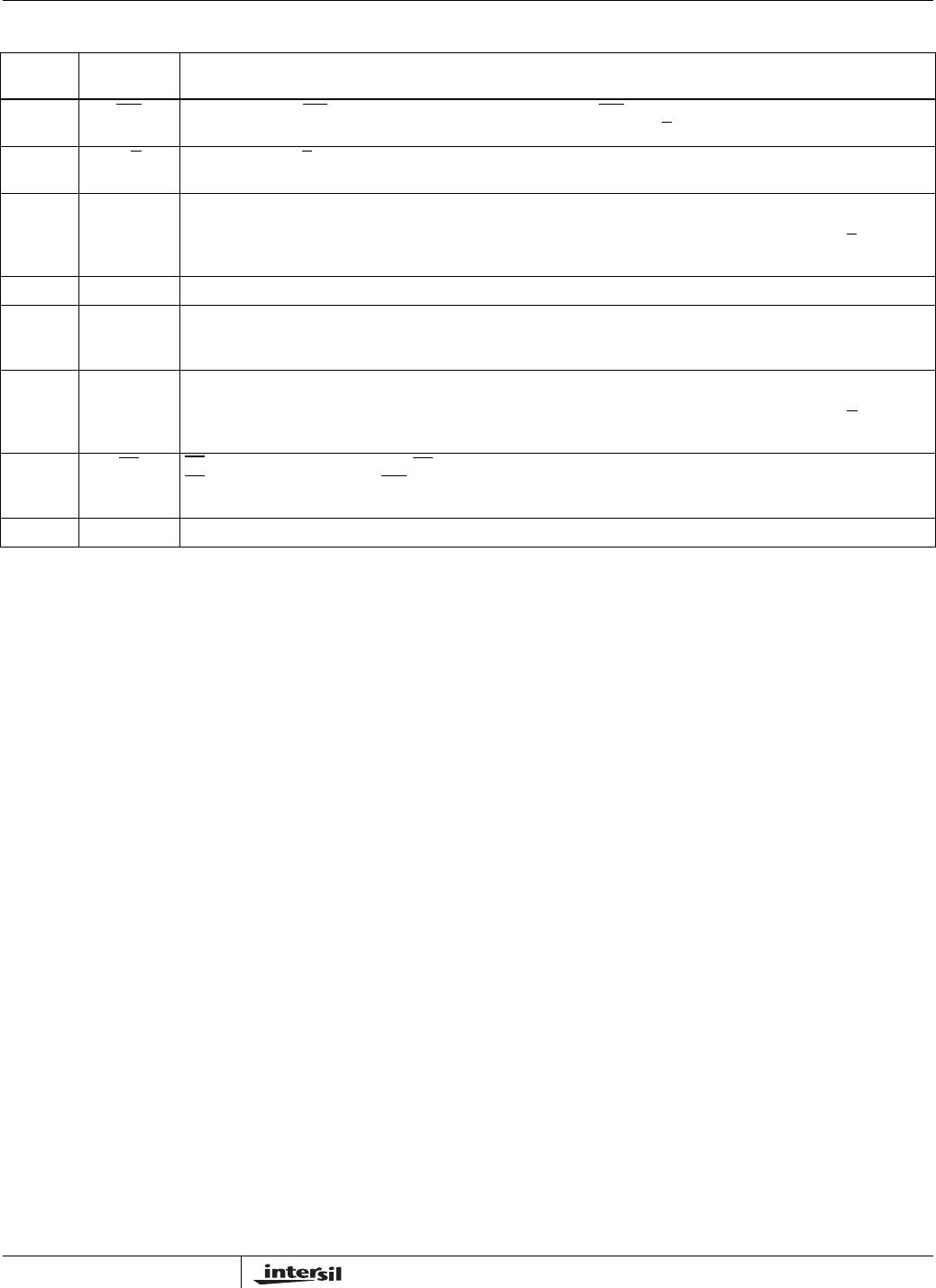

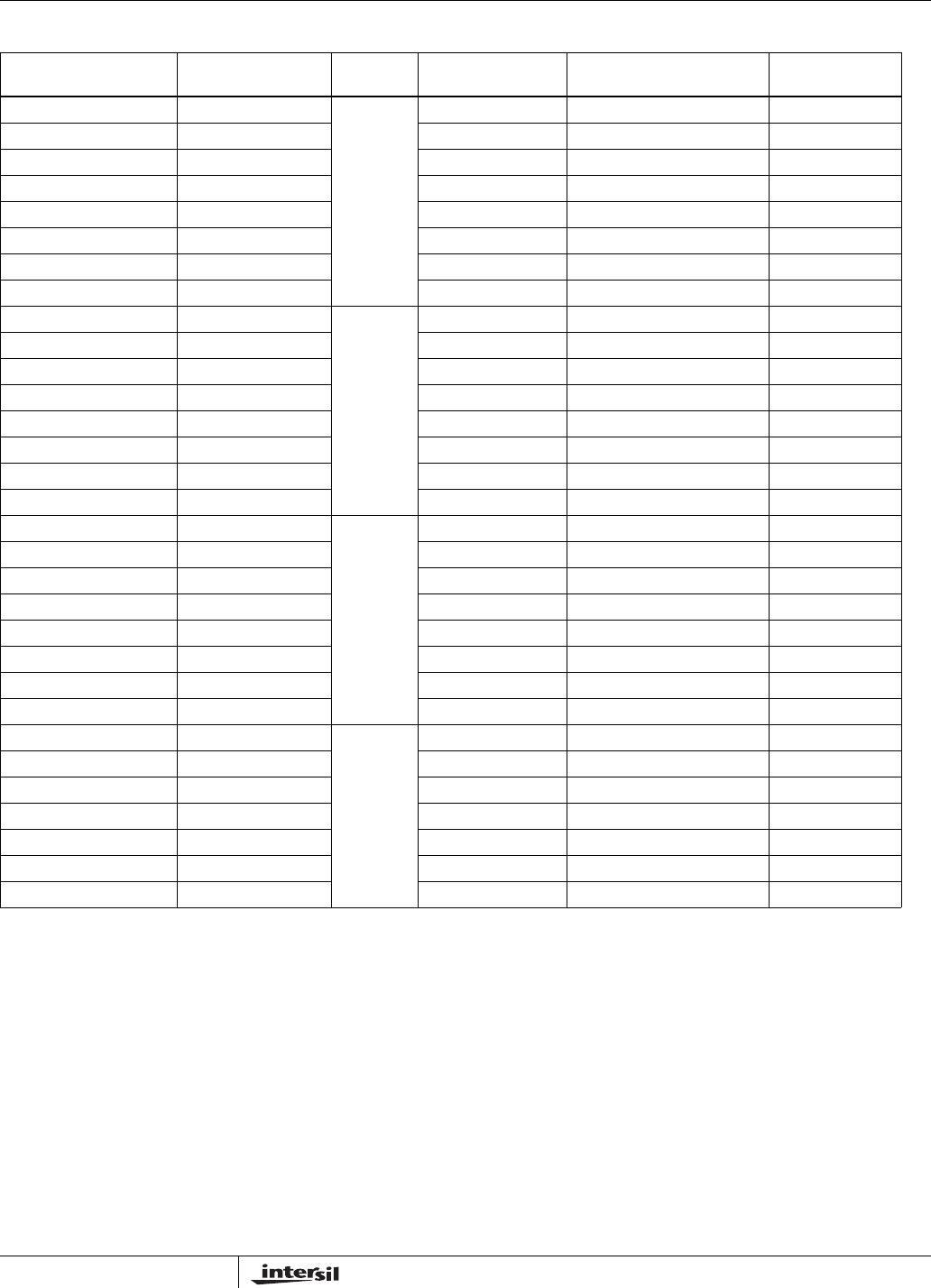

Ordering Information

PART

NUMBER

PART

MARKING

R

TOTAL

(kΩ)

TEMP RANGE

(°C) PACKAGE

PACKAGE

DWG. #

X9C102P X9C102P 1 0 to +70 8 Ld PDIP MDP0031

X9C102PZ (Notes 1, 2) X9C102P Z 0 to +70 8 Ld PDIP (Pb-free) MDP0031

X9C102PI X9C102P I -40 to +85 8 Ld PDIP MDP0031

X9C102PIZ (Notes 1, 2) X9C102P ZI -40 to +85 8 Ld PDIP (Pb-free) MDP0031

X9C102S*

,

** X9C102S 0 to +70 8 Ld SOIC MDP0027

X9C102SZ* (Note 1) X9C102S Z 0 to +70 8 Ld SOIC (Pb-free) MDP0027

X9C102SI*

,

** X9C102S I -40 to +85 8 Ld SOIC MDP0027

X9C102SIZ*

,

** (Note 1) X9C102S ZI -40 to +85 8 Ld SOIC (Pb-free) MDP0027

X9C103P X9C103P 10 0 to +70 8 Ld PDIP MDP0031

X9C103PZ (Notes 1, 2) X9C103P Z 0 to +70 8 Ld PDIP (Pb-free) MDP0031

X9C103PI X9C103P I -40 to +85 8 Ld PDIP MDP0031

X9C103PIZ (Note 1) X9C103P ZI -40 to +85 8 Ld PDIP (Pb-free) MDP0031

X9C103S*

,

** X9C103S 0 to +70 8 Ld SOIC MDP0027

X9C103SZ*

,

** (Note 1) X9C103S Z 0 to +70 8 Ld SOIC (Pb-free) MDP0027

X9C103SI*

,

** X9C103S I -40 to +85 8 Ld SOIC MDP0027

X9C103SIZ*

,

** (Note 1) X9C103S ZI -40 to +85 8 Ld SOIC (Pb-free) MDP0027

X9C503P X9C503P 50 0 to +70 8 Ld PDIP MDP0031

X9C503PZ (Notes 1, 2) X9C503P Z 0 to +70 8 Ld PDIP (Pb-free) MDP0031

X9C503PI X9C503P I -40 to +85 8 Ld PDIP MDP0031

X9C503PIZ (Notes 1, 2) X9C503P ZI -40 to +85 8 Ld PDIP (Pb-free) MDP0031

X9C503S* X9C503S 0 to +70 8 Ld SOIC MDP0027

X9C503SZ* (Note 1) X9C503S Z 0 to +70 8 Ld SOIC (Pb-free) MDP0027

X9C503SI*

,

** X9C503S I -40 to +85 8 Ld SOIC MDP0027

X9C503SIZ*

,

** (Note 1) X9C503S ZI -40 to +85 8 Ld SOIC (Pb-free) MDP0027

X9C104P X9C104P 100 0 to +70 8 Ld PDIP MDP0031

X9C104PI X9C104P I -40 to +85 8 Ld PDIP MDP0031

X9C104PIZ (Notes 1, 2) X9C104P ZI -40 to +85 8 Ld PDIP (Pb-free) MDP0031

X9C104S*

,

** X9C104S 0 to +70 8 Ld SOIC MDP0027

X9C104SZ*

,

** (Note 1) X9C104S Z 0 to +70 8 Ld SOIC (Pb-free) MDP0027

X9C104SI*

,

** X9C104S I -40 to +85 8 Ld SOIC MDP0027

X9C104SIZ*

,

** (Note 1) X9C104S ZI -40 to +85 8 Ld SOIC (Pb-free) MDP0027

*Add “T1” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

**Add “T2” suffix for tape and reel. Please refer to TB347 for details on reel specifications.

NOTES:

1. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100%

matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering

operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free

requirements of IPC/JEDEC J STD-020.

2. Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

X9C102, X9C103, X9C104, X9C503