ADF4106 Data Sheet

Charge Pump Currents

CPI3, CPI2, and CPI1 program Current Setting 1 for the charge

pump. CPI6, CPI5, and CPI4 program Current Setting 2 for the

charge pump. The truth table is given in Table 9.

Prescaler Value

P2 and P1 in the function latch set the prescaler values. The

prescaler value should be chosen so that the prescaler output

frequency is always less than or equal to 325 MHz. Therefore,

with an RF frequency of 4 GHz, a prescaler value of 16/17 is

valid, but a value of 8/9 is not valid.

PD Polarity

This bit sets the phase detector polarity bit. See Table 9.

CP Three-State

This bit controls the CP output pin. With the bit set high, the

CP output is put into three-state. With the bit set low, the CP

output is enabled.

THE INITIALIZATION LATCH

When C2 and C1 = 1 and 1, respectively, the initialization latch

is programmed. This is essentially the same as the function

latch (programmed when C2 and C1 = 1 and 0, respectively).

However, when the initialization latch is programmed, there is

an additional internal reset pulse applied to the R and N (A, B)

counters. This pulse ensures that the N (A, B) counter is at the

load point when the N (A, B) counter data is latched and the

device begins counting in close phase alignment.

If the latch is programmed for synchronous power-down (CE

pin is high, PD1 bit is high, and PD2 bit is low), the internal

pulse also triggers this power-down. The prescaler reference

and the oscillator input buffer are unaffected by the internal

reset pulse; therefore, close phase alignment is maintained when

counting resumes.

When the first N (A, B) counter data is latched after

initialization, the internal reset pulse is again activated.

However, successive N (A, B) counter loads after this will not

trigger the internal reset pulse.

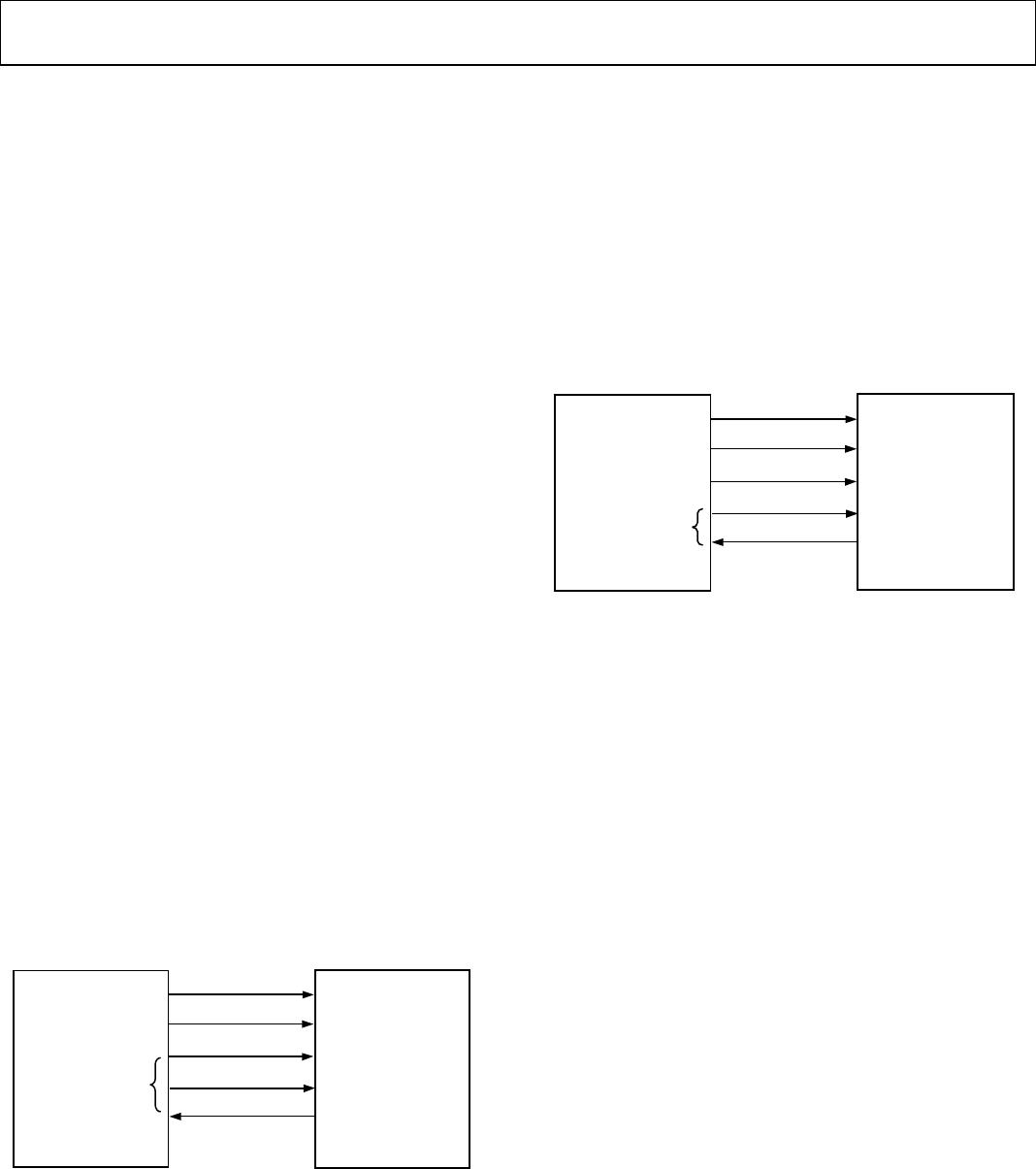

Device Programming After Initial Power-Up

After initial power up of the device, there are three methods for

programming the device: initialization latch, CE pin, and

counter reset.

Initialization Latch Method

• Apply V

DD

.

• Program the initialization latch (11 in two LSBs of input

word). Make sure that the F1 bit is programmed to 0.

• Do a function latch load (10 in two LSBs of the control

word), making sure that the F1 bit is programmed to a 0.

• Do an R load (00 in two LSBs).

• Do an N (A, B) load (01 in two LSBs).

When the initialization latch is loaded, the following occurs:

• The function latch contents are loaded.

• An internal pulse resets the R, N (A, B), and timeout counters

to load-state conditions and also three-states the charge

pump. Note that the prescaler band gap reference and the

oscillator input buffer are unaffected by the internal reset

pulse, allowing close phase alignment when counting

resumes.

• Latching the first N (A, B) counter data after the initialization

word activates the same internal reset pulse. Successive N (A,

B) loads will not trigger the internal reset pulse, unless there

is another initialization.

CE PIN METHOD

• Apply V

DD

.

• Bring CE low to put the device into power-down. This is an

asychronous power-down in that it happens immediately.

• Program the function latch (10).

• Program the R counter latch (00).

• Program the N (A, B) counter latch (01).

• Bring CE high to take the device out of power-down. The R

and N (A, B) counters now resume counting in close

alignment.

Note that after CE goes high, a 1 µs duration may be required

for the prescaler band gap voltage and oscillator input buffer

bias to reach steady state.

CE can be used to power the device up and down to check for

channel activity. The input register does not need to be

reprogrammed each time the device is disabled and enabled as

long as it is programmed at least once after V

DD

is initially

applied.

COUNTER RESET METHOD

• Apply V

DD

.

• Do a function latch load (10 in two LSBs). As part of this,

load 1 to the F1 bit. This enables the counter reset.

• Do an R counter load (00 in two LSBs).

• Do an N (A, B) counter load (01 in two LSBs).

• Do a function latch load (10 in two LSBs). As part of this,

load 0 to the F1 bit. This disables the counter reset.

This sequence provides the same close alignment as the

initialization method. It offers direct control over the internal

reset. Note that counter reset holds the counters at load point

and three-states the charge pump but does not trigger

synchronous power-down.

Rev. F | Page 18 of 24