PCA9541A All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2014. All rights reserved.

Product data sheet Rev. 5 — 24 April 2014 11 of 45

NXP Semiconductors

PCA9541A

2-to-1 I

2

C-bus master selector with interrupt logic and reset

7.3.2 Register 1: Control Register (B1:B0 = 01b)

The Control Register described below is identical for both the masters. Nevertheless,

there are physically 2 internal Control Registers, one for each upstream channel.

When master 0 reads/writes in this register, the internal Control Register 0 is accessed.

When master 1 reads/writes in this register, the internal Control Register 1 is accessed.

[1] Default values are the same for PCA9541A/01, PCA9541A/03.

[1] MYBUS and NMYBUS is an exclusive-OR type function where:

Equal values (00b or 11b) means that the master reading its Control Register has control of the bus.

Different values (01b or 10b) means that the master reading its Control Register does not have control of

the bus.

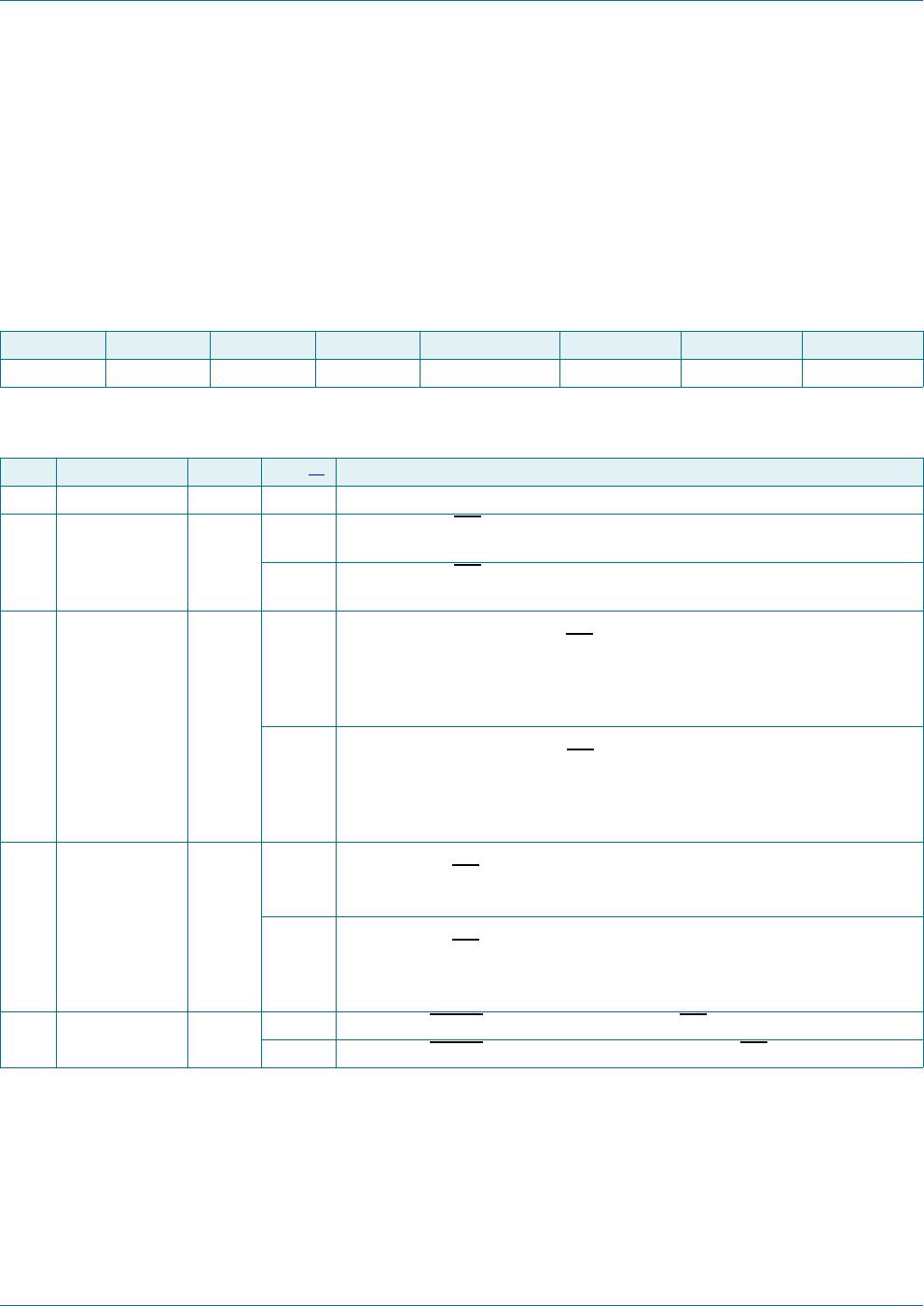

Table 7. Register 1 - Control Register (B1:B0 = 01b) bit allocation

7 6 5 4 3 2 1 0

NTESTON TESTON 0 BUSINIT NBUSON BUSON NMYBUS MYBUS

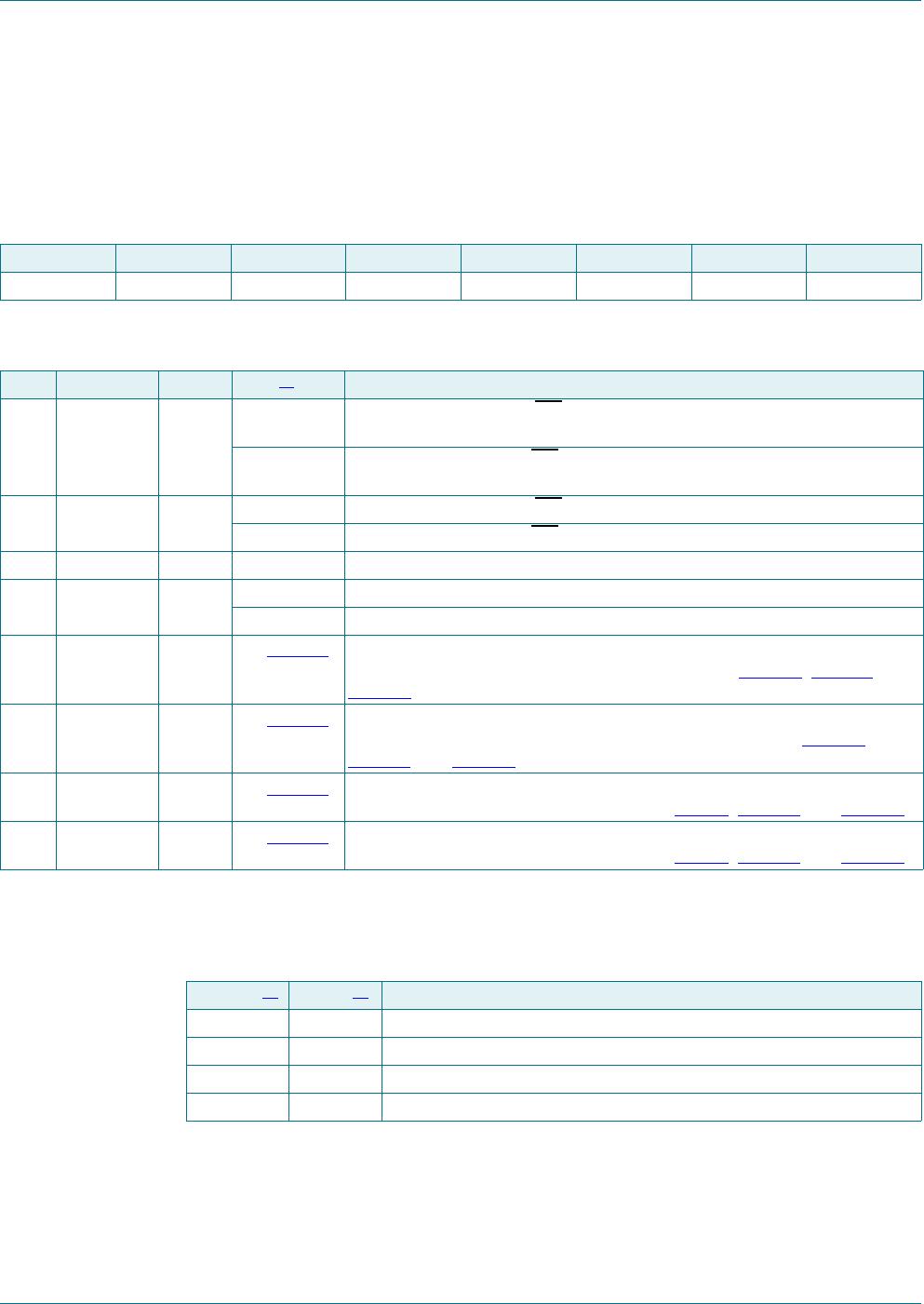

Table 8. Register 1 - Control Register (B1:B0 = 01b) bit description

Legend: * default value

Bit Symbol Access Value

[1]

Description

7 NTESTON R/W 0* A logic level HIGH to the INT

line of the other channel is sent (interrupt

cleared).

1 A logic level LOW to the INT

line of the other channel is sent (interrupt

generated).

6 TESTON R/W 0* A logic level HIGH to the INT

line is sent (interrupt cleared).

1 A logic level LOW to the INT

line is sent (interrupt generated).

5 - R only 0* not used

4 BUSINIT R/W 0* Bus initialization is not requested.

1 Bus initialization is requested.

3 NBUSON R only see Table 11

NBUSON bit along with BUSON bit decides whether any upstream channel

is connected to the downstream channel or not. See Table 10, Tab le 11, and

Table 12

.

2 BUSON R/W see Table 11

BUSON bit along with the NBUSON bit decides whether any upstream

channel is connected to the downstream channel or not. See Table 10,

Table 11, and Table 12.

1 NMYBUS R only see Table 11

NMYBUS bit along with MYBUS bit decides which upstream channel is

connected to the downstream channel. See Tab le 9

, Table 11, and Table 12.

0 MYBUS R/W see Table 11

MYBUS bit along with the NMYBUS bit decides which upstream channel is

connected to the downstream channel. See Tab le 9, Table 11, and Table 12.

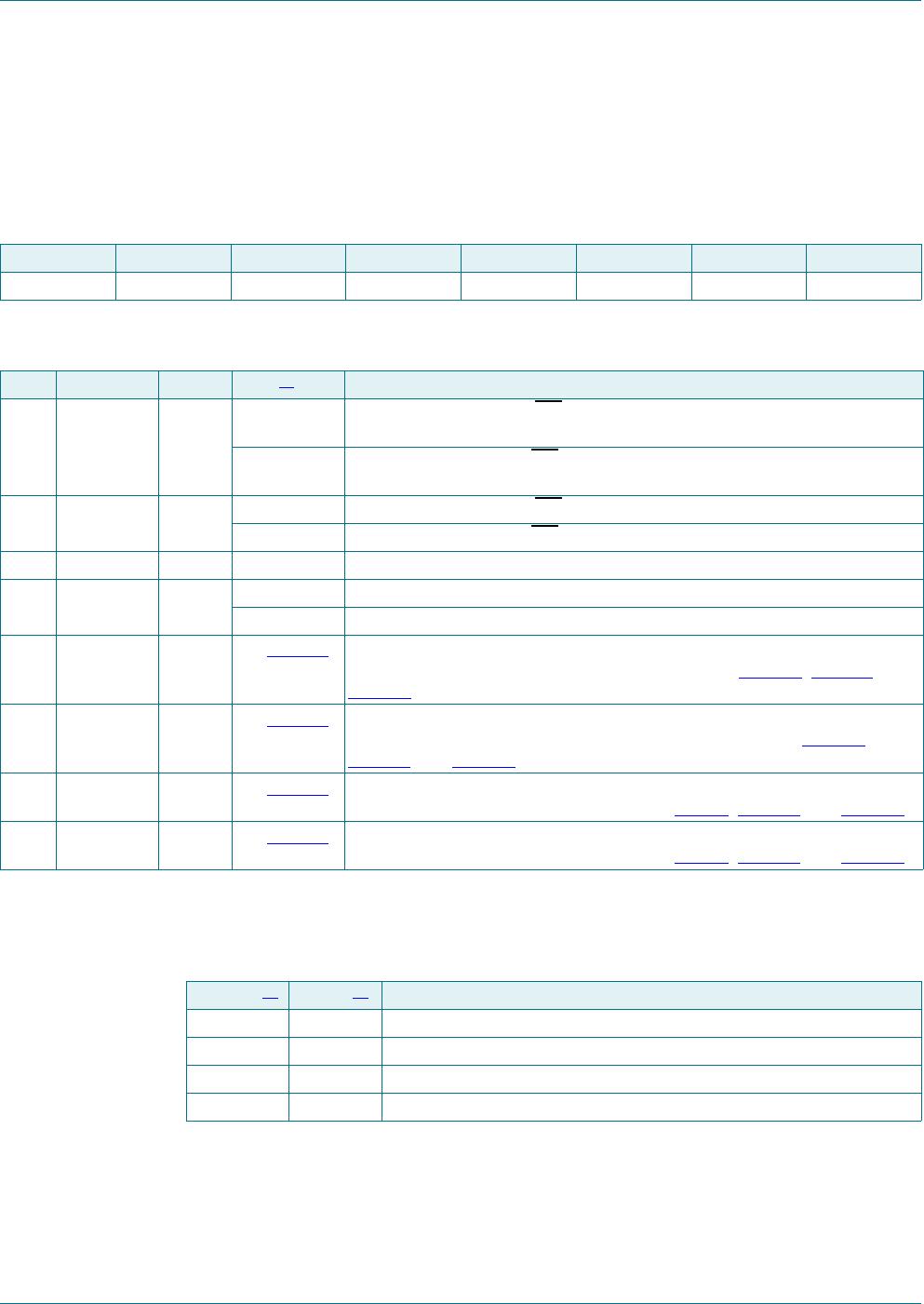

Table 9. MYBUS and NMYBUS truth table

As a master reads its Control Register

NMYBUS

[1]

MYBUS

[1]

Slave channel

0 0 The master reading this combination has control of the bus.

1 0 The master reading this combination does not have control of the bus.

0 1 The master reading this combination does not have control of the bus.

1 1 The master reading this combination has control of the bus.