Data Sheet AD797

Rev. K | Page 11 of 19

THEORY OF OPERATION

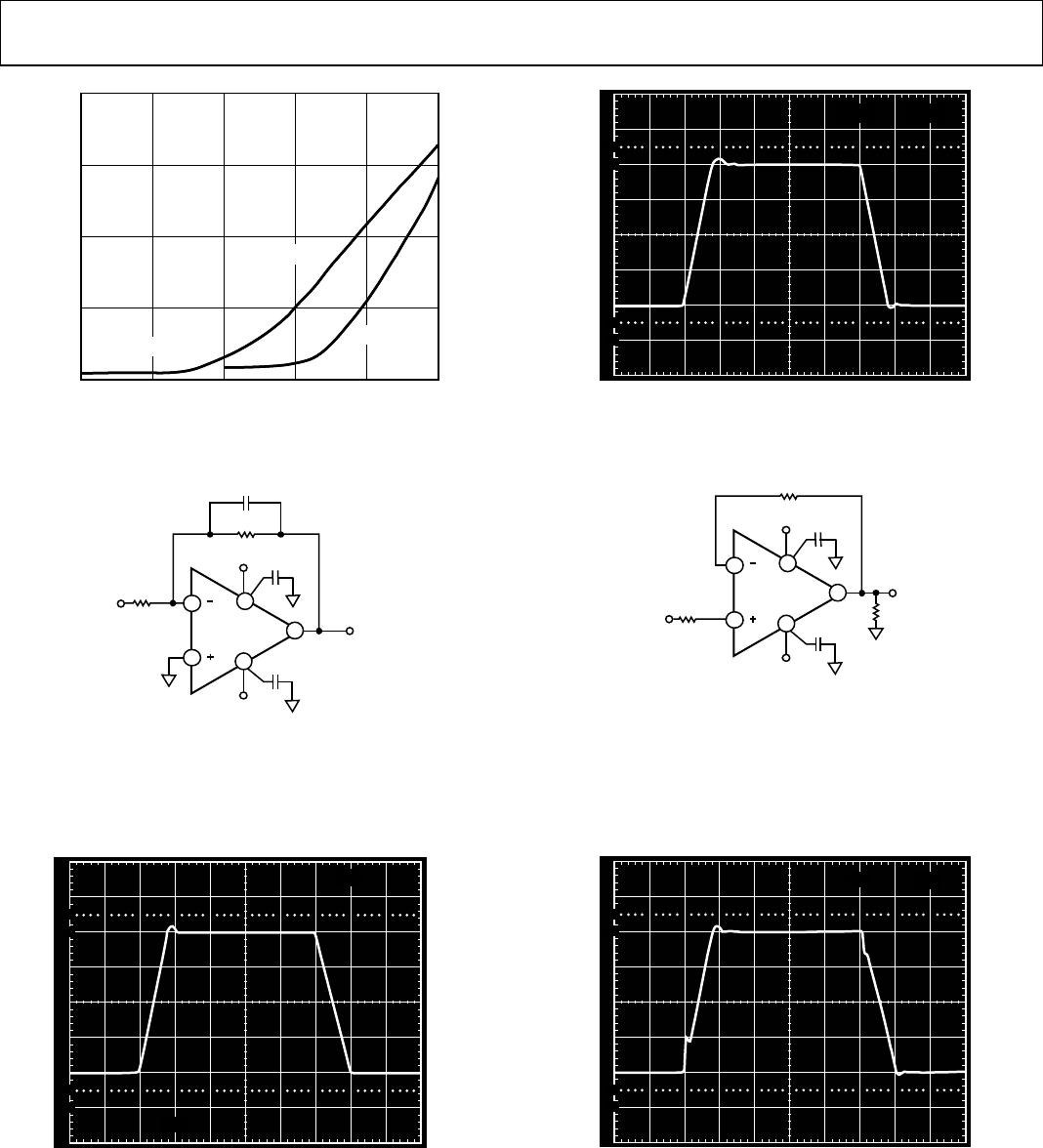

The architecture of the AD797 was developed to overcome

inherent limitations in previous amplifier designs. Previous

precision amplifiers used three stages to ensure high open-loop

gain (see Figure 31) at the expense of additional frequency com-

pensation components. Slew rate and settling performance are

usually compromised, and dynamic performance is not adequate

beyond audio frequencies. As can be seen in Figure 31, the first

stage gain is rolled off at high frequencies by the compensation

network. Second stage noise and distortion then appears at the

input and degrade performance. The AD797, on the other hand,

uses a single ultrahigh gain stage to achieve dc as well as dynamic

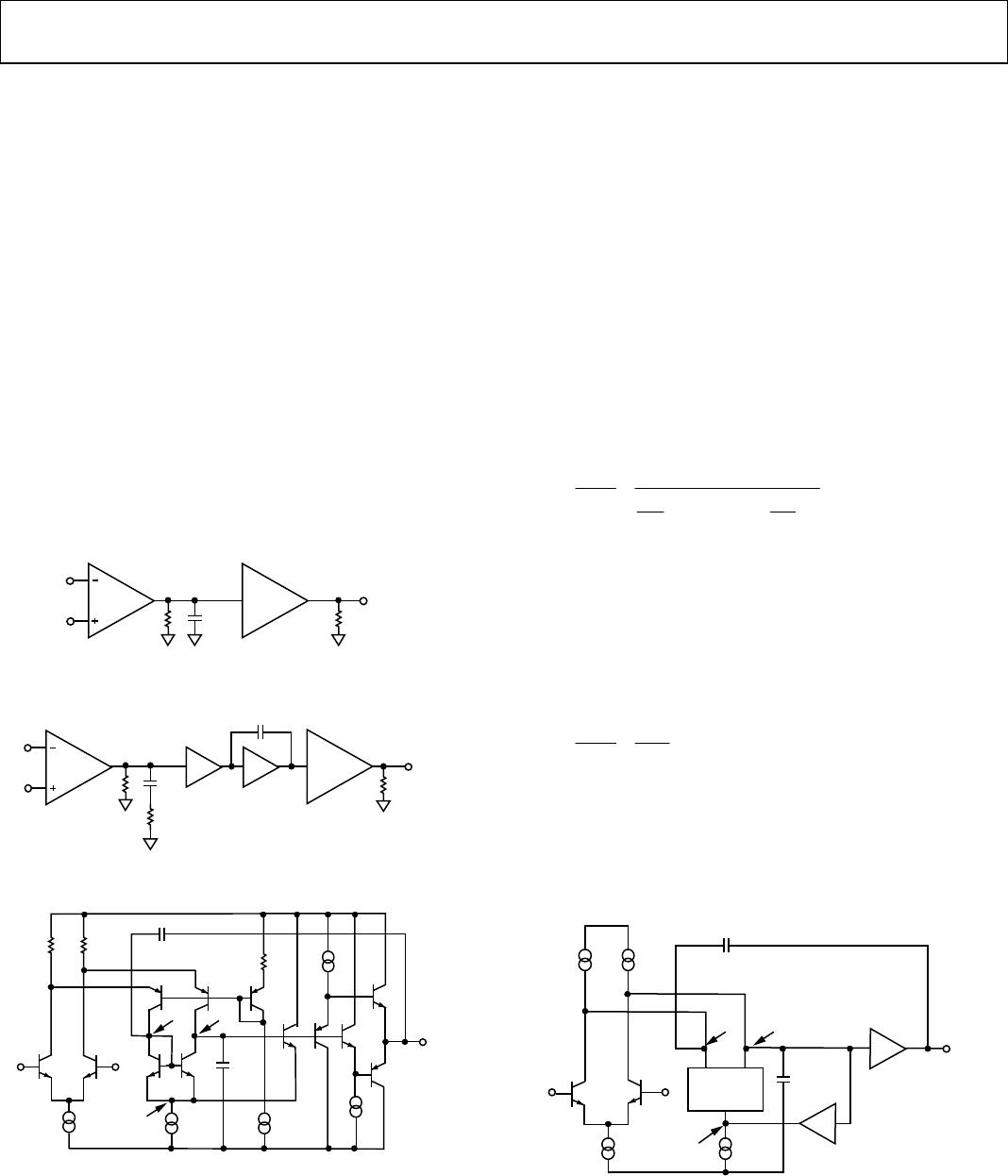

precision. As shown in the simplified schematic (Figure 32),

Node A, Node B, and Node C track the input voltage, forcing

the operating points of all pairs of devices in the signal path to

match. By exploiting the inherent matching of devices fabricated on

the same IC chip, high open-loop gain, CMRR, PSRR, and low

V

OS

are guaranteed by pairwise device matching (that is, NPN

to NPN and PNP to PNP), not by an absolute parameter such as

beta and the early voltage.

R1

R1

C1

g

m

g

m

GAIN = g

m

× R1 × 5 × 10

6

GAIN = g

m

× R1 × A2 × A3

C1

R2

BUFFER

BUFFER

R

L

R

L

V

OUT

V

OUT

a.

b.

A2 A3

C2

00846-030

Figure 31. Model of AD797 vs. That of a Typical Three-Stage Amplifier

R2

R1 I5

V

OUT

Q1 Q2

+IN

–IN

R3

Q5

C

Q6

I7I1 I4

I6

Q12 Q8

Q9

Q11

Q10

Q3

Q7

Q4

AB

C

N

C

C

V

SS

CC

00846-031

Figure 32. AD797 Simplified Schematic

This matching benefits not just dc precision, but, because it holds

up dynamically, both distortion and settling time are also reduced.

This single stage has a voltage gain of >5 × 10

6

and V

OS

< 80 μV,

while at the same time providing a THD + noise of less than

−120 dB and true 16-bit settling in less than 800 ns.

The elimination of second-stage noise effects has the additional

benefit of making the low noise of the AD797 (<0.9 nV/√Hz)

extend to beyond 1 MHz. This means new levels of perform-

ance for sampled data and imaging systems. All of this

performance as well as load drive in excess of 30 mA are made

possible by the Analog Devices, Inc., advanced complementary

bipolar (CB) process.

Another unique feature of this circuit is that the addition of a

single capacitor, C

N

(see Figure 32), enables cancellation of

distortion due to the output stage. This can best be explained by

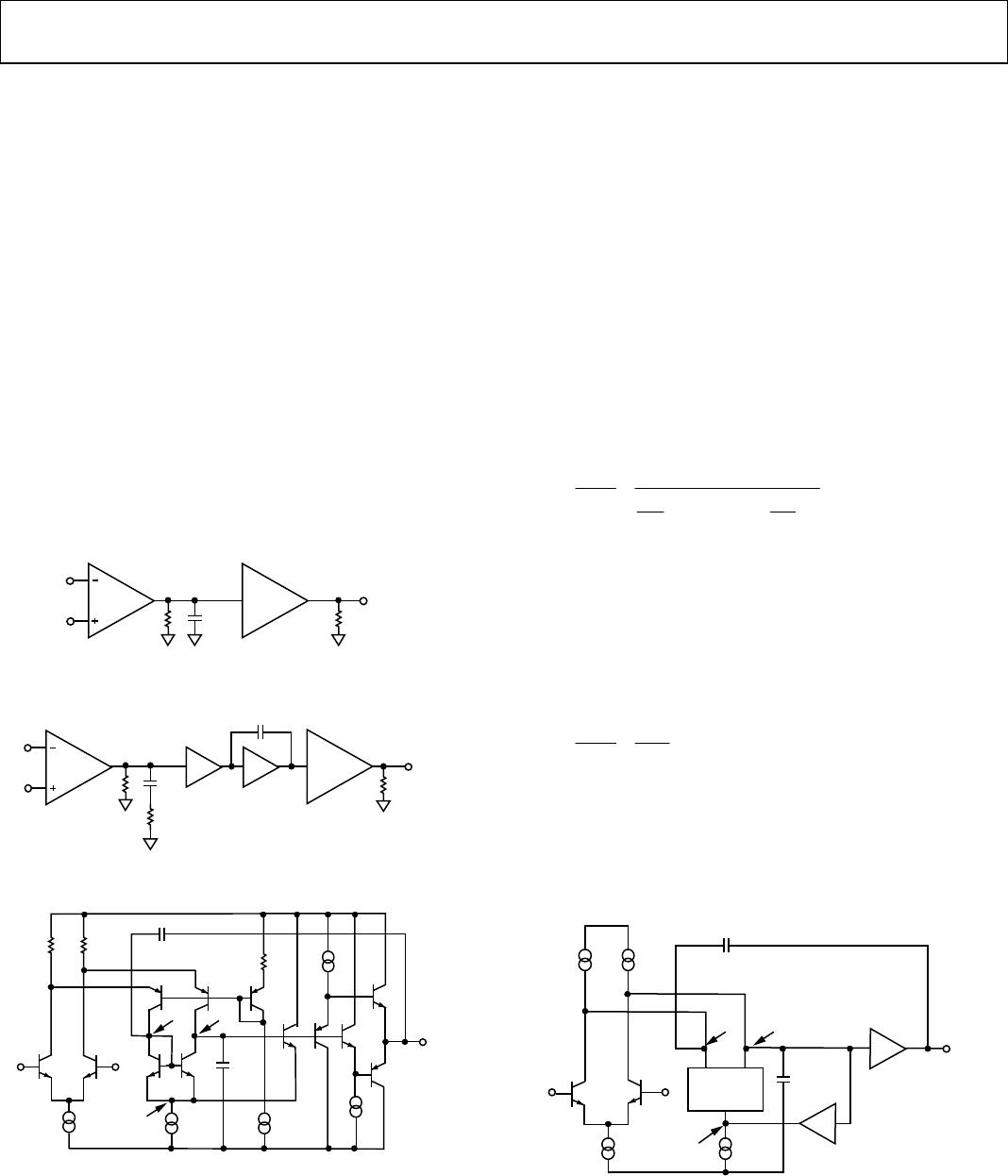

referring to a simplified representation of the AD797 using

idealized blocks for the different circuit elements (Figure 33).

A single equation yields the open-loop transfer function of this

amplifier; solving it at Node B yields

j

A

C

jCj

A

C

g

V

V

C

N

N

m

IN

OUT

where:

g

m

is the transconductance of Q1 and Q2.

A is the gain of the output stage (~1).

V

OUT

is voltage at the output.

V

IN

is differential input voltage.

When C

N

is equal to C

C

, the ideal single-pole op amp response

is attained:

Cj

g

V

V

m

IN

OUT

In Figure 33, the terms of Node A, which include the properties of

the output stage, such as output impedance and distortion, cancel

by simple subtraction. Therefore, the distortion cancellation does

not affect the stability or frequency response of the amplifier. With

only 500 μA of output stage bias, the AD797 delivers a 1 kHz

sine wave into 60 Ω at 7 V rms with only 1 ppm of distortion.

–IN+IN

Q1 Q2

I1 I2

V

OUT

I3 C

A

I4

C

N

C

C

B

00846-032

CURRENT

MIRROR

A

1

Figure 33. AD797 Block Diagram