PowerPAK

®

SO-8 Mounting and Thermal Considerations

APPLICATION NOTE

Application Note AN821

www.vishay.com

Vishay Siliconix

Revision: 16-Mai-13

3

Document Number: 71622

For technical questions, contact: powermosfettechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT

ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

THERMAL PERFORMANCE

Introduction

A basic measure of a device’s thermal performance

is the junction-to-case thermal resistance, R

thJC

, or the

junction-to-foot thermal resistance, R

thJF

This parameter is

measured for the device mounted to an infinite heat sink and

is therefore a characterization of the device only, in other

words, independent of the properties of the object to which

the device is mounted. Table 1 shows a comparison of

the DPAK, PowerPAK SO-8, and standard SO-8. The

PowerPAK has thermal performance equivalent to the

DPAK, while having an order of magnitude better thermal

performance over the SO-8.

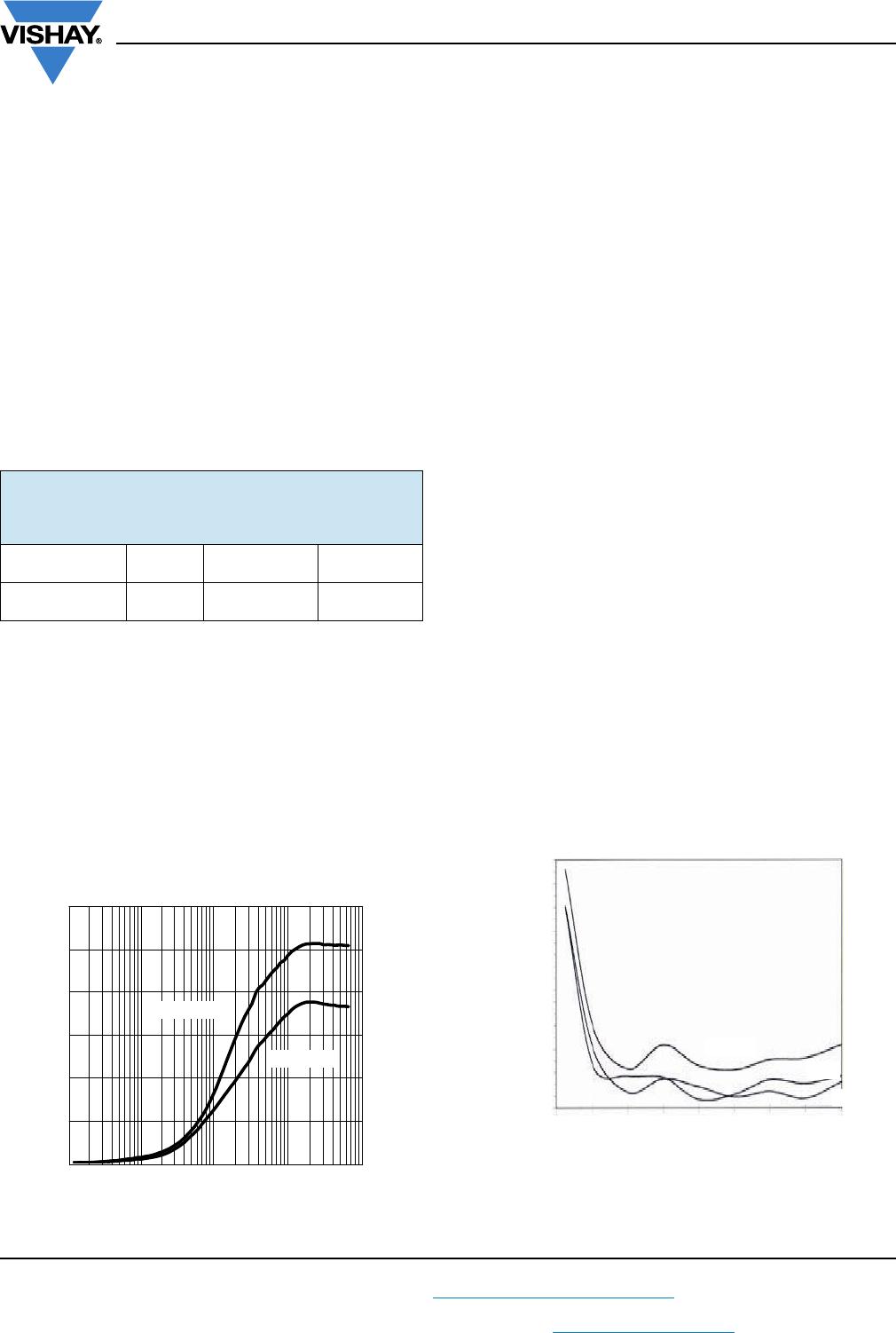

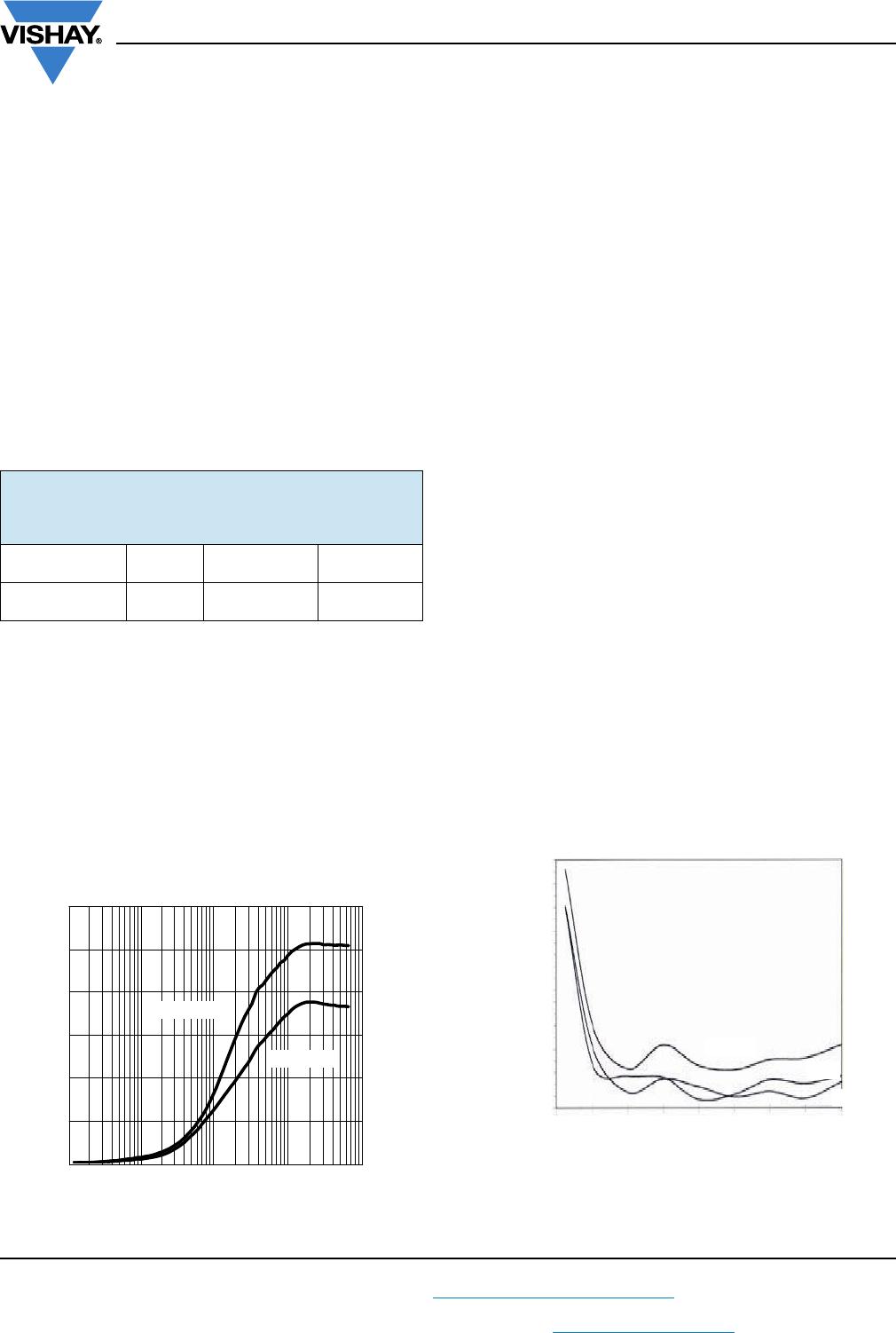

Thermal Performance on Standard SO-8 Pad Pattern

Because of the common footprint, a PowerPAK SO-8

can be mounted on an existing standard SO-8 pad pattern.

The question then arises as to the thermal performance

of the PowerPAK device under these conditions. A

characterization was made comparing a standard SO-8 and

a PowerPAK device on a board with a trough cut out

underneath the PowerPAK drain pad. This configuration

restricted the heat flow to the SO-8 land pads. The results

are shown in figure 5.

Fig. 5 PowerPAK SO-8 and Standard SO-0 Land Pad Thermal

Path

Because of the presence of the trough, this result suggests

a minimum performance improvement of 10 °C/W by using

a PowerPAK SO-8 in a standard SO-8 PC board mount.

The only concern when mounting a PowerPAK on a

standard SO-8 pad pattern is that there should be no traces

running between the body of the MOSFET. Where the

standard SO-8 body is spaced away from the pc board,

allowing traces to run underneath, the PowerPAK sits

directly on the pc board.

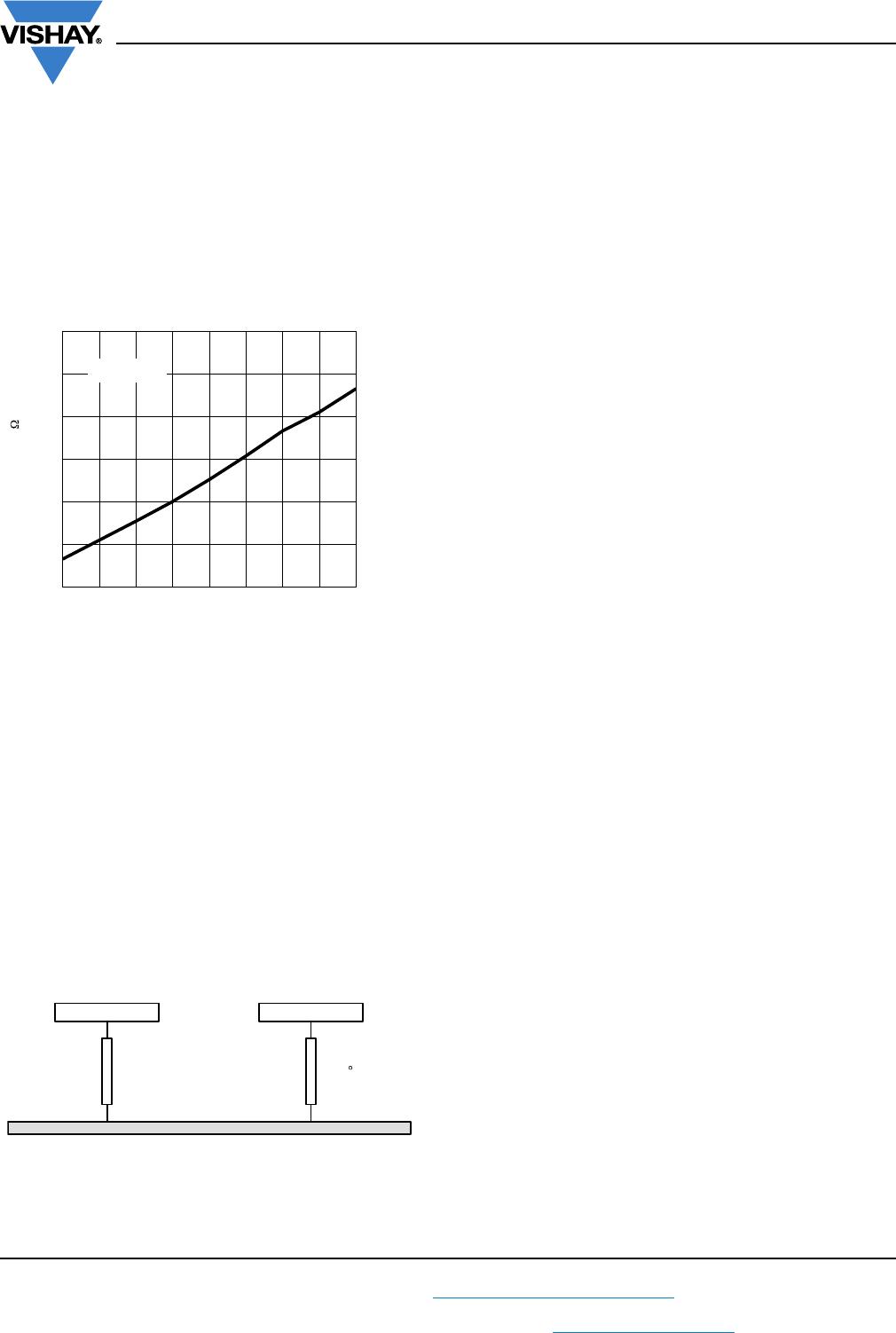

Thermal Performance - Spreading Copper

Designers may add additional copper, spreading copper, to

the drain pad to aid in conducting heat from a device. It is

helpful to have some information about the thermal

performance for a given area of spreading copper.

Figure 6 shows the thermal resistance of a PowerPAK SO-8

device mounted on a 2-in. 2-in., four-layer FR-4 PC board.

The two internal layers and the backside layer are solid

copper. The internal layers were chosen as solid copper to

model the large power and ground planes common in many

applications. The top layer was cut back to a smaller area

and at each step junction-to-ambient thermal resistance

measurements were taken. The results indicate that an area

above 0.3 to 0.4 square inches of spreading copper gives no

additional thermal performance improvement. A

subsequent experiment was run where the copper on the

back-side was reduced, first to 50 % in stripes to mimic

circuit traces, and then totally removed. No significant effect

was observed.

Fig. 6 Spreading Copper Junction-to-Ambient Performance

TABLE 1 - DPAK AND POWERPAK SO-8

EQUIVALENT STEADY STATE

PERFORMANCE

DPAK

PowerPAK

SO-8

Standard

SO-8

Thermal

Resistance R

thJC

1.2 °C/W 1 °C/W 16 °C/W

Si4874DY vs. Si7446DP PPAK on a 4-Layer Board

SO-8 Pattern, Trough Under Drain

Pulse Duration (sec)

)

s

ttaw/

C

( e

cn

adep

m

I

0.0001

0

1

50

60

10

100000.01

40

20

Si4874DY

Si7446DP

100

30

R

th

vs. Spreading Copper

(0 %, 50 %, 100 % Back Copper)

Spreading Copper (sq in)

)sttaw/C(

ecn

adep

m

I

0.00

56

51

46

41

36

0.25 0.50 0.75 1.00 1.25 1.50 1.75 2.00

0 %

50 %

100 %