6

LTC1564

1564fa

UU

U

PI FU CTIO S

passes the bits directly when the CS/HOLD input is at logic

0. When CS/HOLD changes to logic 1, the F pins cease to

have effect and the latch holds the previous values. The F

code controls the filter’s cutoff frequency f

C

in 10kHz steps

up to 150kHz, as summarized in Table 1.

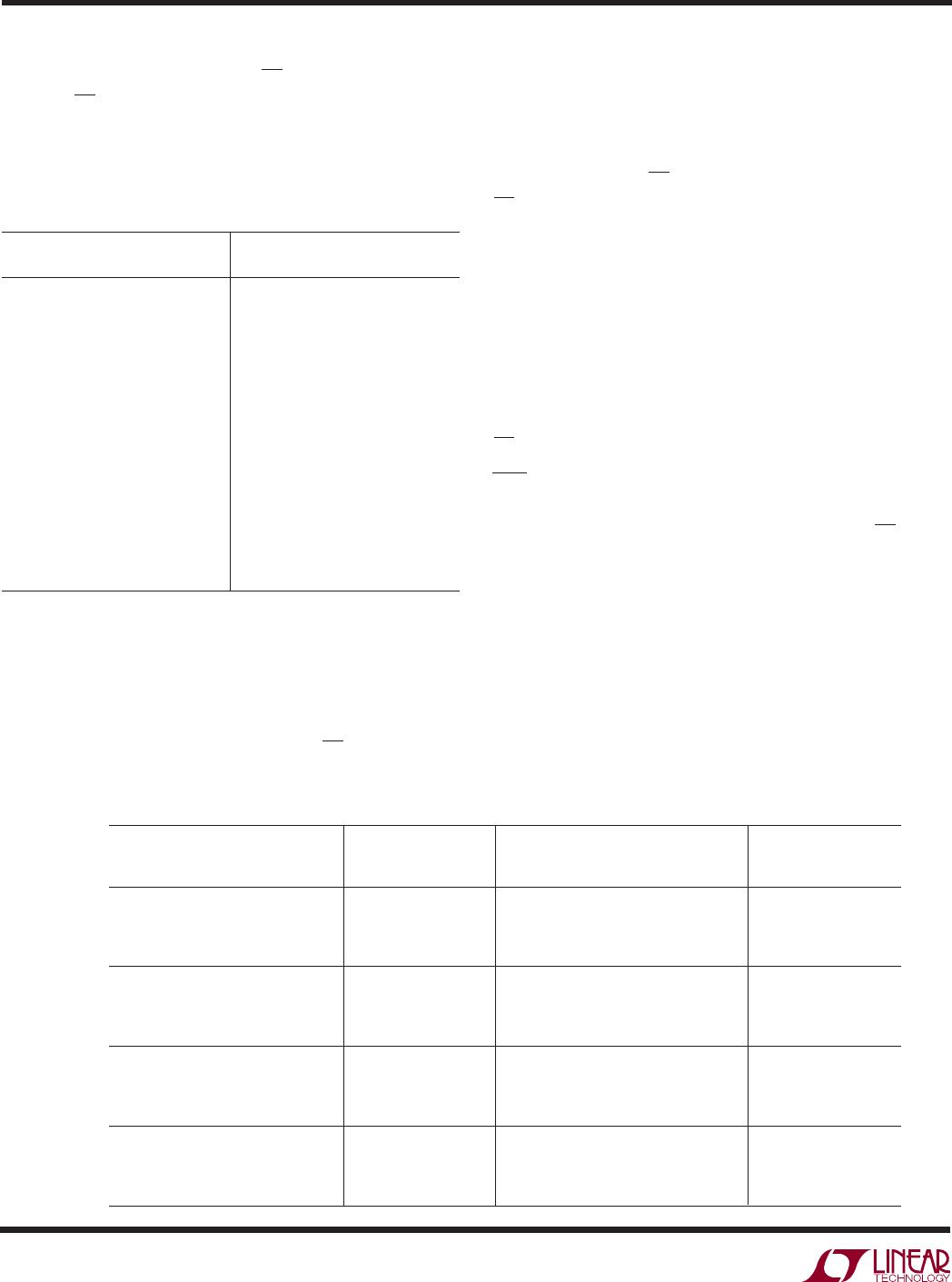

Table 1

F3 F2 F1 F0 NOMINAL F

C

(AT OUTPUT OF INTERNAL LATCH) (CUTOFF FREQUENCY)

0000 0 (Mute State: Filter Gain is Zero)

0001 10kHz

0010 20kHz

0011 30kHz

0100 40kHz

0101 50kHz

0110 60kHz

0111 70kHz

1000 80kHz

1001 90kHz

1010 100kHz

1011 110kHz

1100 120kHz

1101 130kHz

1110 140kHz

1111 150kHz

Thus f

C

is proportional to the binary value of the F code.

Note that small current sources pull F1 to V

+

and F3, F2

and F0 to V

–

when these pins are left unconnected (see

Electrical Characteristics, Note 5). This sets an F code

input of 0010 (2, in decimal form) by default, giving an f

C

of 20kHz in normal filtering operation, if CS/HOLD is logic

0 or is open circuited.

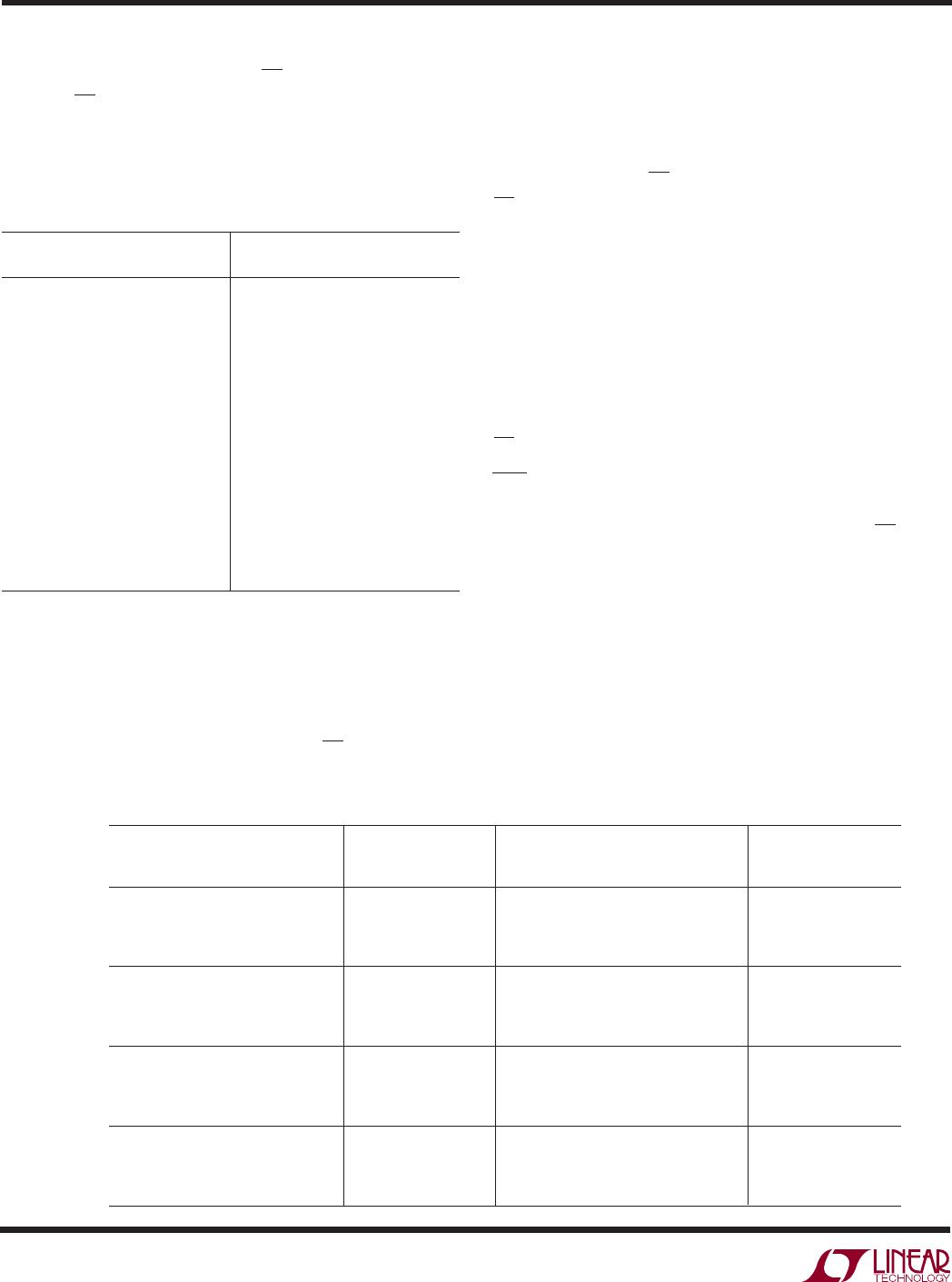

G0, G1, G2, G3 (Pins 9, 10, 11, 12): CMOS-Level Digital

Gain Control (“G Code”) Inputs. G3 is the most significant

bit (MSB). These pins program the LTC1564’s passband

gain through the internal latch, which passes the bits

directly when the CS/HOLD input is at logic 0. When

CS/HOLD changes to logic 1, the G pins cease to have

effect and the latch retains the previous input values. This

gain control is linear in amplitude: nominal passband gain

of the LTC1564 is the binary value of the G code, plus one

as shown in Table 2.

Note that small current sources pull the G pins to V

–

when

these pins are left unconnected (see Electrical Character-

istics, Note 5). This sets a G code input of 0000 by default,

giving unity passband gain in normal filtering operation, if

CS/HOLD is logic 0 or is open circuited.

RST (Pin 13): CMOS-Level Asynchronous Reset Input.

Logic 0 on this pin immediately resets the internal F and G

latch to all zeros, regardless of the state of the CS/HOLD

pin or the F or G input pins. This causes the LTC1564 to

enter a mute state (powered but with zero signal gain)

because of the resulting F = 0000 command. Logic 1

permits the other pins to control F and G. This pin floats to

logic 1 (V

+

) when open circuited because of a small

current source (see Electrical Characteristics, Note 5). A

brief internal reset (shorter than the analog settling time of

the filter) also occurs when power is first applied.

NOMINAL NOMINAL

G3 G2 G1 G0 PASSBAND GAIN (VOLTS PEAK-TO-PEAK) INPUT IMPEDANCE

(VOLT/VOLT) (dB) DUAL 5V SINGLE 5V SINGLE 3V (kΩ)

0000 1 0 10 5.0 3.0 10

0001 2 6.0 5 2.5 1.5 5

0010 3 9.5 3.33 1.67 1.0 3.33

0011 4 12 2.5 1.25 0.75 2.5

0100 5 14.0 2 1 0.6 2

0101 6 15.6 1.67 0.83 0.5 1.67

0110 7 16.9 1.43 0.71 0.43 1.43

0111 8 18.1 1.25 0.63 0.38 1.25

1000 9 19.1 1.1 0.56 0.33 1.11

1001 1020.0 1.0 0.50 0.30 1

1010 1120.8 0.91 0.45 0.27 0.91

1011 1221.6 0.83 0.42 0.25 0.83

1100 1322.3 0.77 0.38 0.23 0.77

1101 1422.9 0.71 0.36 0.21 0.71

1110 1523.5 0.67 0.33 0.20 0.66

1111 1624.1 0.63 0.31 0.19 0.63

(AT OUTPUT OF INTERNAL LATCH)

MAXIMUM INPUT SIGNAL LEVEL

Table 2