LTC2941

14

2941fb

For more information www.linear.com/LTC2941

applicaTions inFormaTion

it is sending its address, it monitors the SDA pin to see

if another device is sending an address at the same time

using standard I

2

C bus arbitration. If the LTC2941 is send-

ing a 1 and reads a 0 on the SDA pin on the rising edge of

SCL, it assumes another device with a lower address is

sending and the LTC2941 immediately aborts its transfer

and waits for the next ARA cycle to tr

y again. If transfer

is successfully completed, the LTC2941 will stop pulling

down the AL/CC pin and will not respond to further ARA

requests until a new alert event occurs.

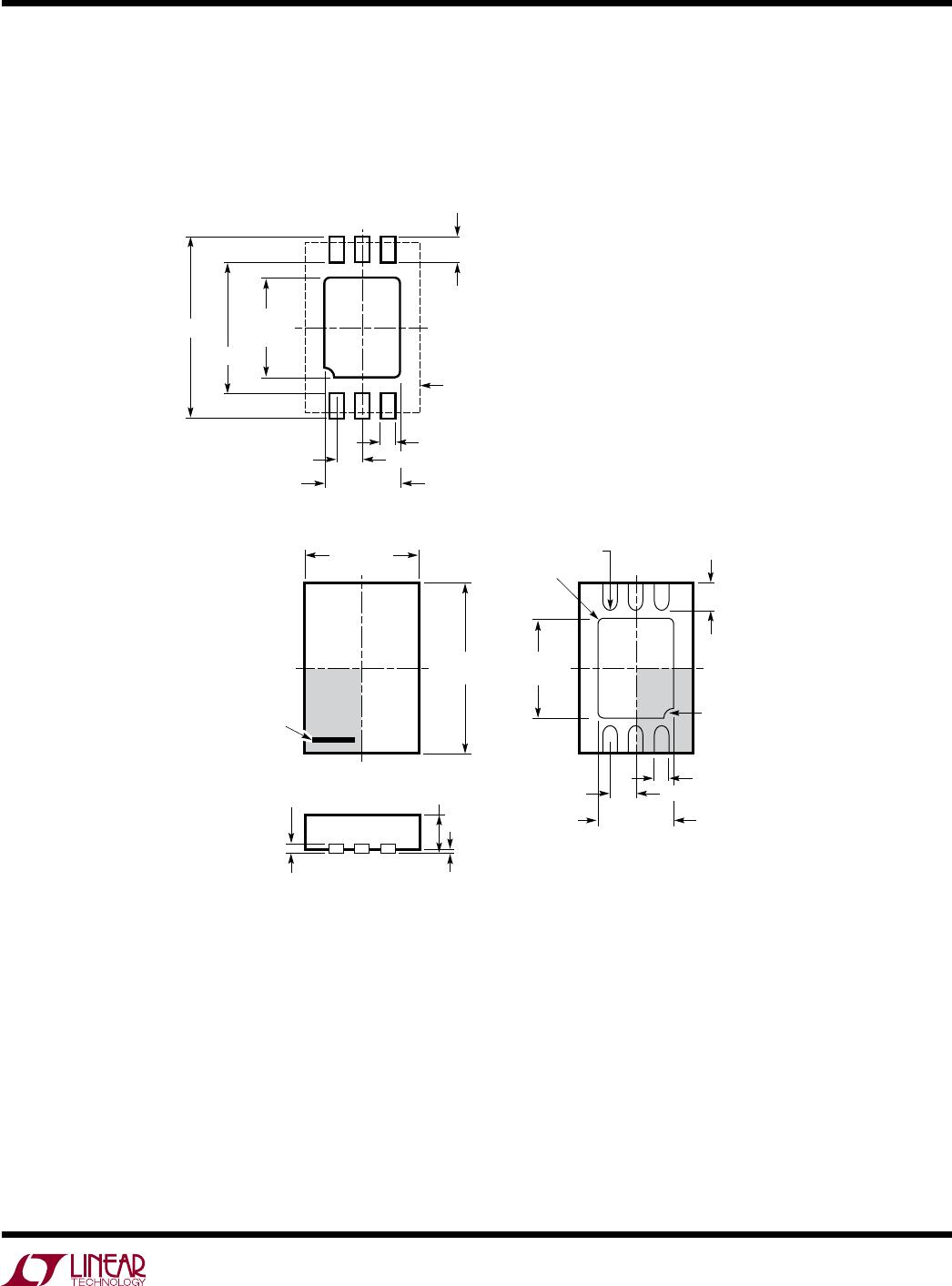

PC Board Layout Recommendations

Keep all traces as short as possible to minimize noise and

inaccuracy. Use a 4-wire Kelvin sense connection for the

sense resistor, locating the LTC2941 close to the resis

-

tor with short sense traces to SENSE

+

and SENSE

–

. Use

wider traces from the resistor to the battery, load and/or

charger (see Figure 10). Put the bypass capacitor close

to SENSE

+

and GND.

LTC2941

2941 F10

R

SENSE

TO BATTERY

TO

CHARGER/LOAD

4

5

6

3

2

C

1

Figure 10. Kelvin Connection on Sense Resistor