LTC4007

11

4007fc

OPERATION

The peak inductor current, at which I

CMP

resets the SR

latch, is controlled by the voltage on ITH. ITH is in turn

controlled by several loops, depending upon the situation

at hand. The average current control loop converts the

voltage between CSP and BAT to a representative cur-

rent. Error amp CA2 compares this current against the

desired current programmed by RPROG at the PROG pin

and adjusts ITH until:

V

R

VV Ak

k

REF

PROG

CSP BAT

=

+Ω

Ω

–.•.

.

11 67 3 01

301

μ

therefore,

I

V

R

A

k

CHARGE MAX

REF

PROG

()

–. •

.

=

⎜

⎟

Ω

11 67

301

μ

RR

SENSE

The voltage at BAT is divided down by an internal resis-

tor divider and is used by error amp EA to decrease ITH

if the divider voltage is above the 1.19V reference. When

the charging current begins to decrease, the voltage at

PROG will decrease in direct proportion. The voltage at

PROG is then given by:

VI R Ak

R

PROG CHARGE SENSE

PROG

=+Ω

()

•.•.•11 67 3 01μ

3301.kΩ

V

PROG

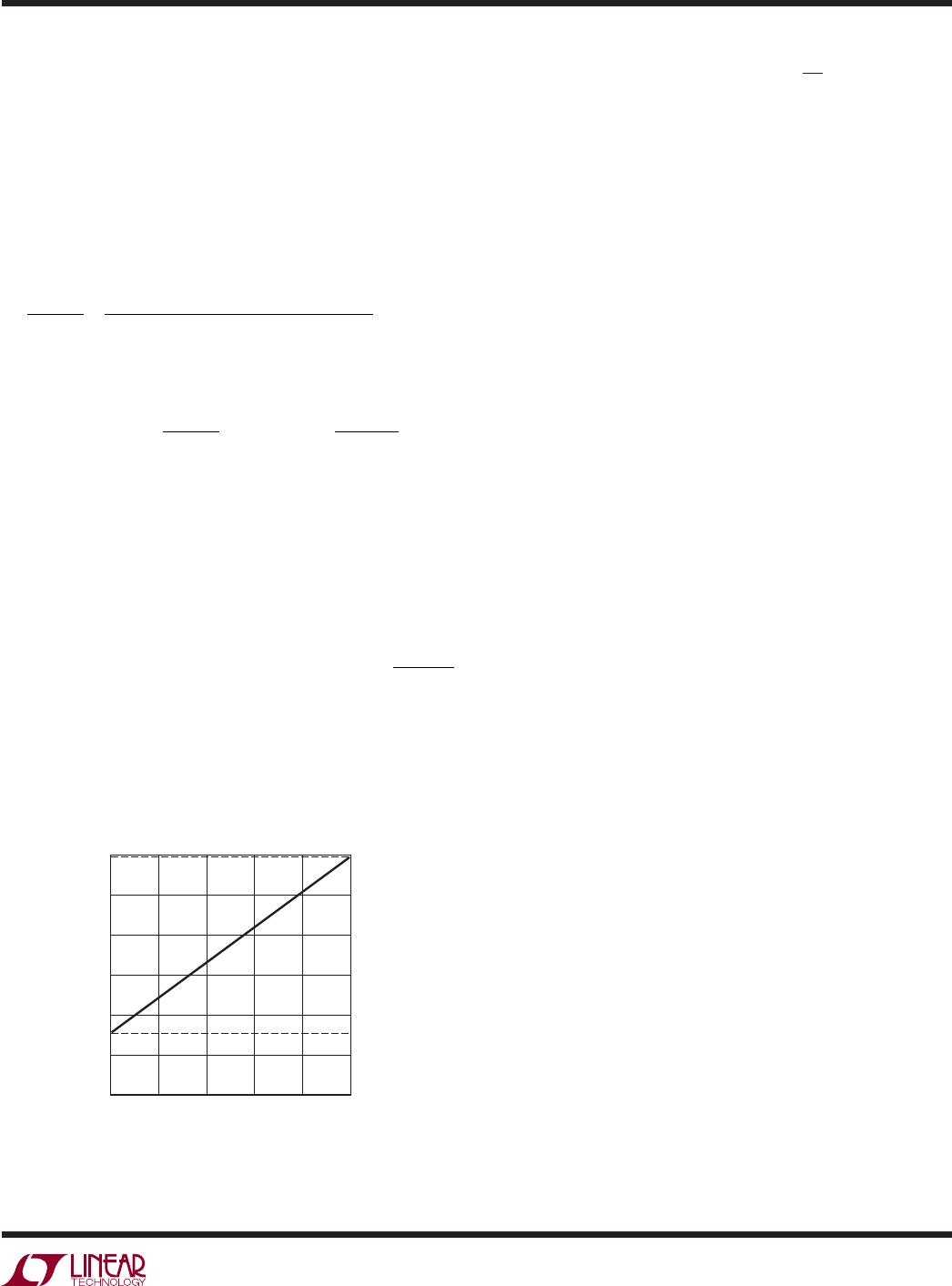

is plotted in Figure 2.

The amplifi er CL1 monitors and limits the input current,

normally from the AC adapter to a preset level (100mV/R

CL

).

At input current limit, CL1 will decrease the ITH voltage,

I

CHARGE

(% OF MAXIMUM CURRENT)

0

0

V

PROG

(V)

0.2

0.4

0.6

0.8

20 40

60 80

100

4007 F02

1.0

1.2 1.19V

0.309V

Figure 2. V

PROG

vs I

CHARGE

thereby reducing charging current. The I

CL

indicator output

will go low when this condition is detected and the FLAG

indicator will be inhibited if it is not already LOW.

If the charging current decreases below 10% to 15%

of programmed current while engaged in input current

limiting, BGATE will be forced low to prevent the charger

from discharging the battery. Audible noise can occur in

this mode of operation.

An overvoltage comparator guards against voltage tran-

sient overshoots (>7% of programmed value). In this

case, both MOSFETs are turned off until the overvoltage

condition is cleared. This feature is useful for batteries

which “load dump” themselves by opening their protection

switch to perform functions such as calibration or pulse

mode charging.

PWM Watchdog Timer

There is a watchdog timer that observes the activity on

the BGATE and TGATE pins. If TGATE stops switching for

more than 40μs, the watchdog activates and turns off the

top MOSFET for about 400ns. The watchdog engages to

prevent very low frequency operation in dropout—a po-

tential source of audible noise when using ceramic input

and output capacitors.

Charger Start-Up

When the charger is enabled, it will not begin switching

until the ITH voltage exceeds a threshold that assures initial

current will be positive. This threshold is 5% to 15% of the

maximum programmed current. After the charger begins

switching, the various loops will control the current at a

level that is higher or lower than the initial current. The

duration of this transient condition depends upon the loop

compensation, but is typically less than 100μs.

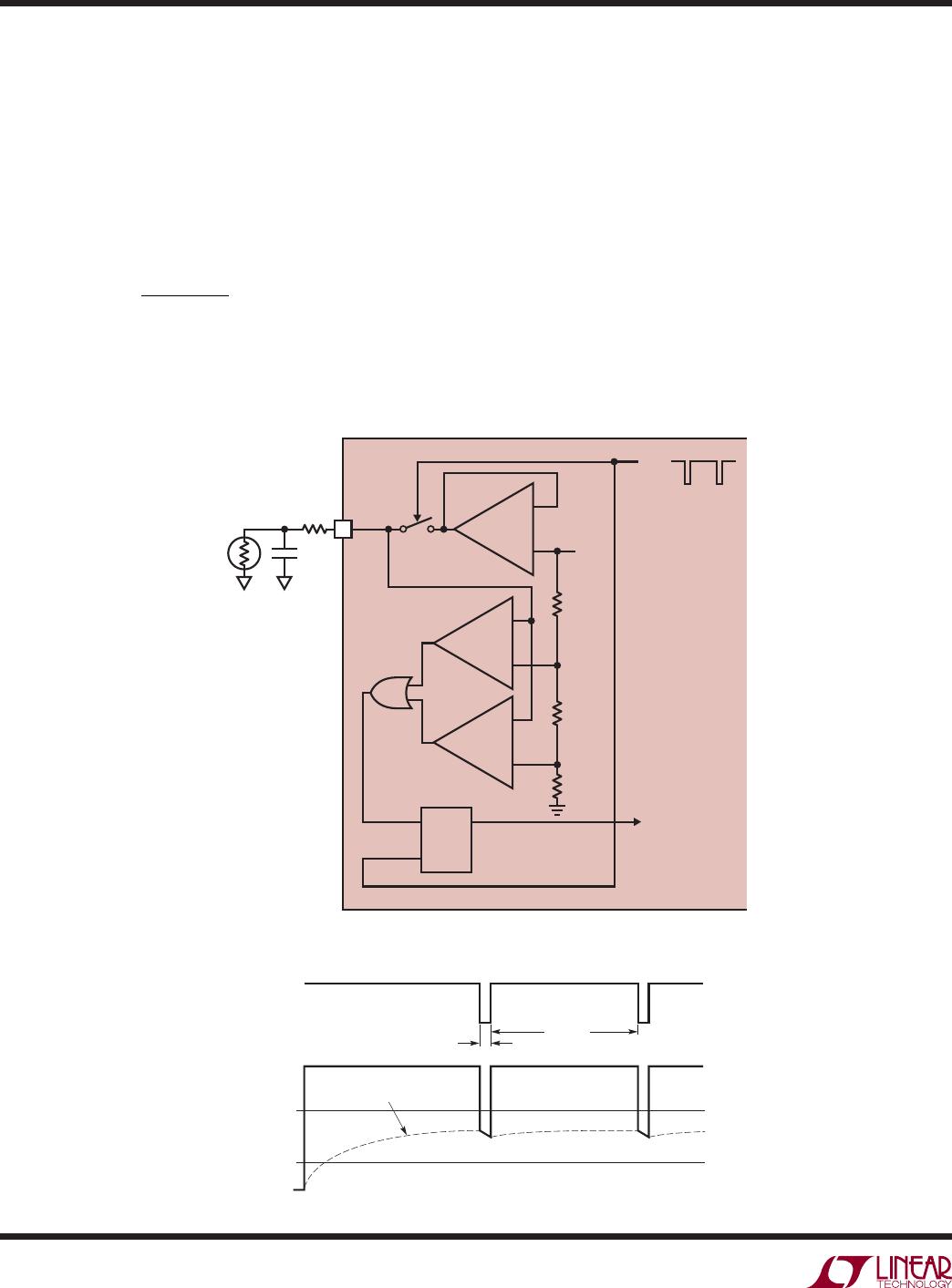

Thermistor Detection

The thermistor detection circuit is shown in Figure 3. It

requires an external resistor and capacitor in order to

function properly.

The thermistor detector performs a sample-and-hold

function. An internal clock, whose frequency is determined