Z87200

Zilog Spread-Spectrum Transceiver

4-37

When input signal MTXEN is set low, bit 1 of address 37

H

controls the activity of the transmit circuitry and, when

MTXEN is set low, bit 1 controls this function. When either

bit 1 or MTXEN (whichever is in control, as defined above)

goes low, a reset sequence occurs on the following TXIF-

CLK cycle to virtually disable all of the transmitter data

path, although the user programmable control registers

are not affected by the power down sequence.

Bit 2 — Receiver Enable

The function of this bit is to allow power consumed by the

operation of the receiver circuitry to be minimized when the

device is not receiving. With the instantaneous acquisition

properties of the PN Matched Filter, it is often desirable to

shut down the receiver circuitry to reduce power consump-

tion, resuming reception periodically until an Acquisi-

tion/Preamble symbol is acquired. Setting bit 2 low reduc-

es the power consumption substantially. When bit 2 is set

high, the receiver will automatically power up in acquisition

mode regardless of its prior state when it was powered

down. Bit 2 of address 37

H

operates independently of bits

1 and 0 of address 37

H

, where these signals have similar

control over the transmit and NCO circuitry, respectively.

Bit 2 of address 37

H

performs the same function as MRX-

EN, and these two signals are logically ORed together to

form the overall control function. When bit 2 of address 37

H

is set low, MRXEN controls the activity of the receiver cir-

cuitry and, when MRXEN is set low, bit 2 of address 37

H

controls the activity of the receiver circuitry. When either bit

2 or MRXEN (whichever is in control, as defined above)

goes low, a reset sequence begins on the following RXIF-

CLK cycle and continues through a total of six RXIFCLK

cycles to virtually disable all of the receiver data paths. The

user- programmable control registers are not affected by

the power down sequence, with the exception of

RXTEST

7-0

(address 38

H

), which is reset to 0. If the

RXTEST

7-0

bus is being used to read any function other

than the PN Matched Filter I and Q inputs, the value must

be rewritten.

Address 38

H

:

Bits 3-0 — RXTEST

7-0

Function Select

The data stored in bits 3-0 of address 38

H

selects the sig-

nal available at the RXTEST

7-0

bus (pins 41-48). These

pins provide access to 16 test points within the receiver ac-

cording to the data stored in bits 3-0 of address 38

H

and

the assignments shown in The validity of the RXTEST

7-0

outputs at RXIFCLK speeds greater than 20 MHz is de-

pendent on the output selected: outputs that change more

rapidly than once per symbol may be indeterminate.

Note that the reset sequence that occurs when the receiv-

er is disabled will also reset the contents of address 38

H

to

a value of 0. If the RXTEST7-0 bus is to be used to observe

any function other than the PN Matched Filter I and Q in-

puts, then the appropriate value must be rewritten.

Address 39

H

:

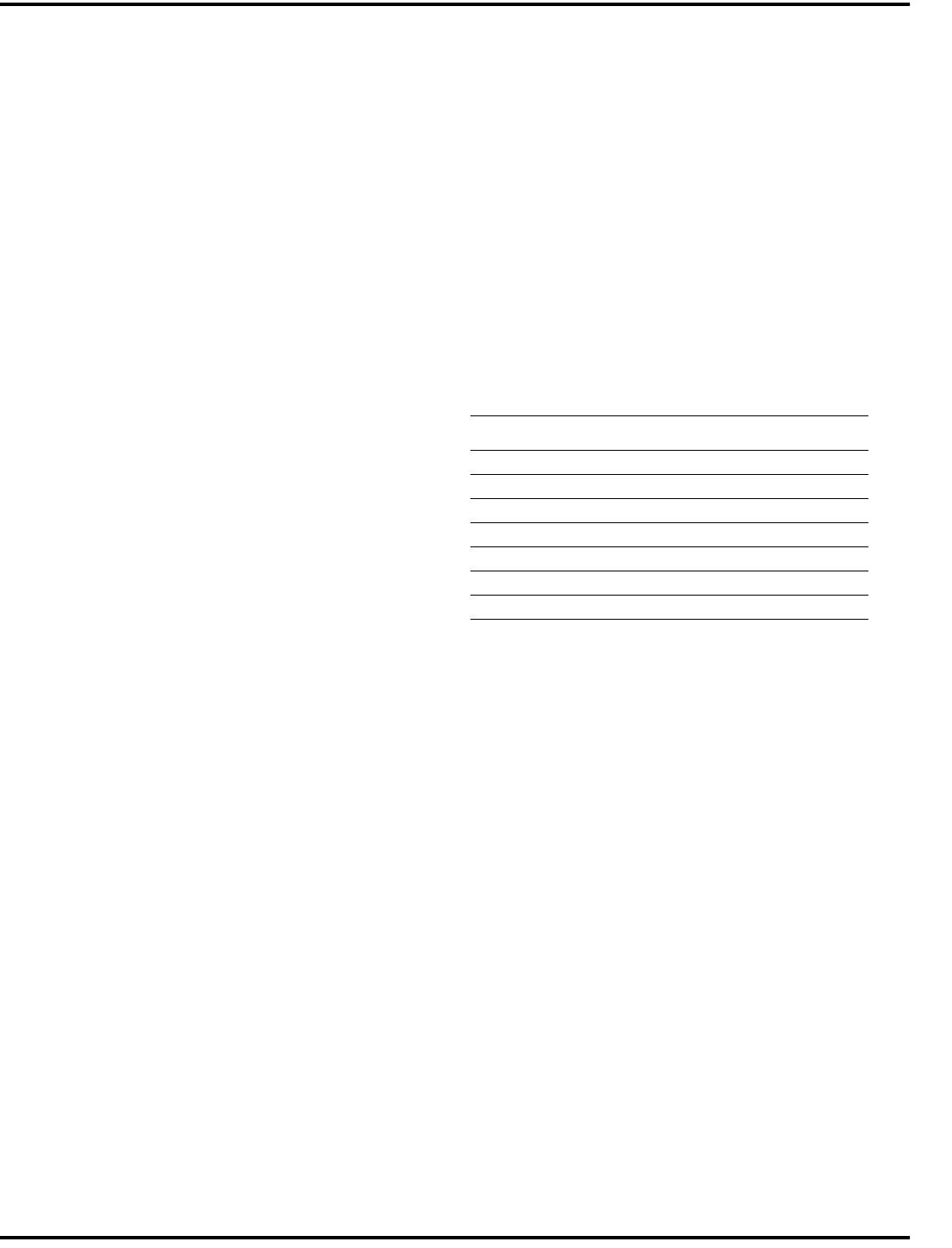

Bits 6-0 — Matched Filter Power Saver

The data stored in bits 6-0 of address 39

H

allows the un-

used sections of the PN Matched Filter to be turned off

when the PN Matched Filter is configured to be less than

64 taps long for data symbols. All taps are always fully

powered when the device is in acquisition mode.

The PN Matched Filter is split into seven 9-tap sections,

and the power to each section is controlled by the settings

of bits 6-0 of address 39

H

, as shown in Table 19.

Power control is not provided for Tap 0, the first tap of the

PN Matched Filter, since Tap 0 is always used no matter

what the PN code length. Setting a bit high in bits 6-0 of ad-

dress 39

H

turns off the power to the corresponding block

of taps of the PN Matched Filter. The power should only be

turned off to those blocks of taps for which all the tap coef-

ficients in that block have been set to zero

Address 3A

H

:

Receiver Data Symbols per Burst (bits 15-8)

The data stored as two bytes in addresses 2E

H

(LS byte)

and 3A

H

(MS byte) defines the number of data symbols per

burst. This unsigned value must range from 3 to 65,535

(0003

H

to FFFF

H

), and the number of data symbols per

burst will be this value minus 2, giving a range of 1 to

65,533. Note that the range is slightly different from that in

the transmitter. Once the number of received data symbols

processed exceeds this number, the burst is assumed to

have ended and the Z87200 immediately returns to acqui-

sition mode to await the next burst.

Table 19. Matched Filter Tap Power Control

Bit in Addr. 39

H

MF Taps Controlled

0 1-9

1 10-18

2 19-27

3 28-36

4 37-45

5 46-54

6 55-64