10©2018 Integrated Device Technology, Inc. May 30, 2018

9FGV1005 Datasheet

1

Single CMOS driver active for each output pair.

2

See Test Loads for details.

3

I

DDCORE

= I

DDA

+ I

DDD.

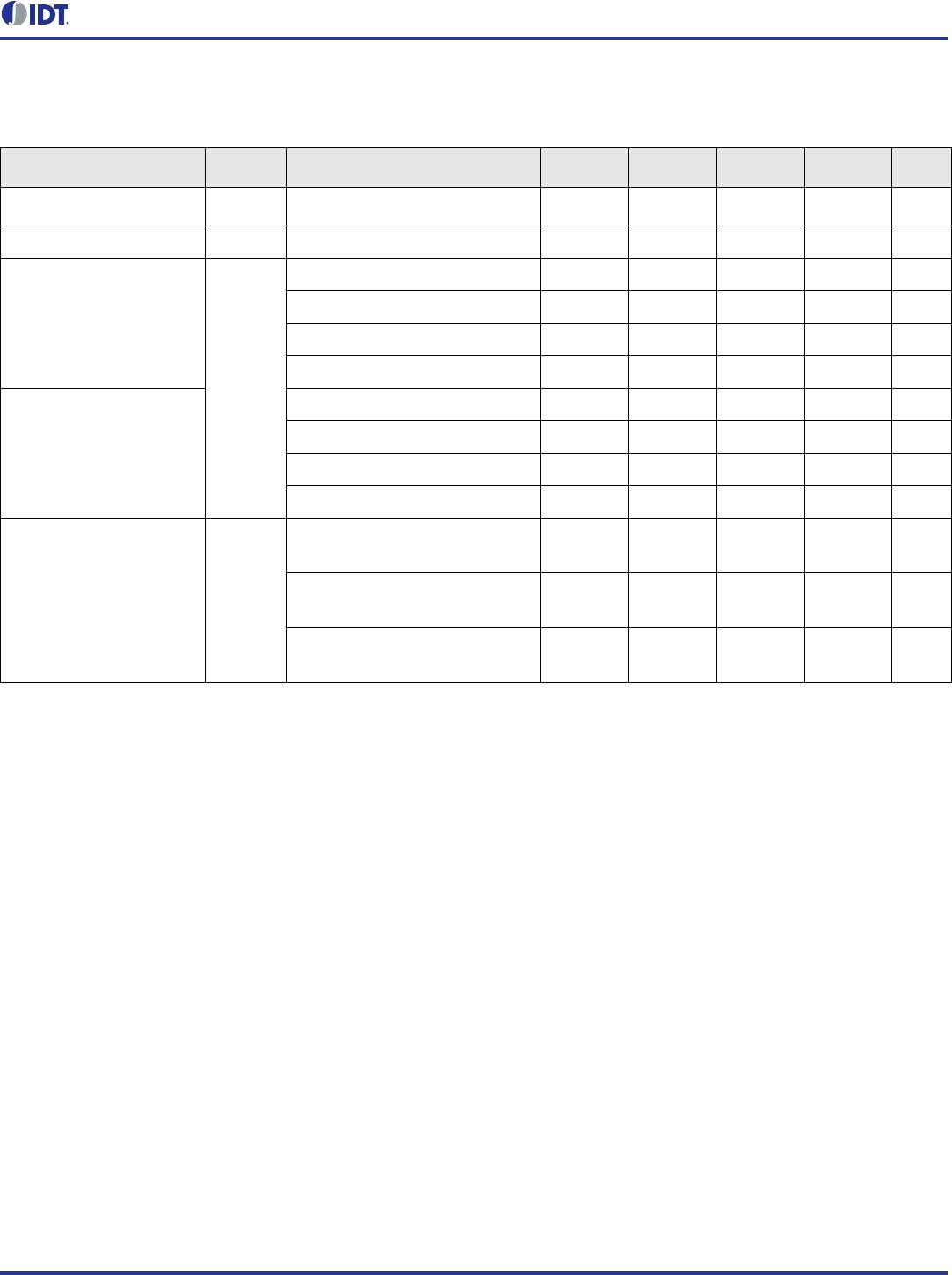

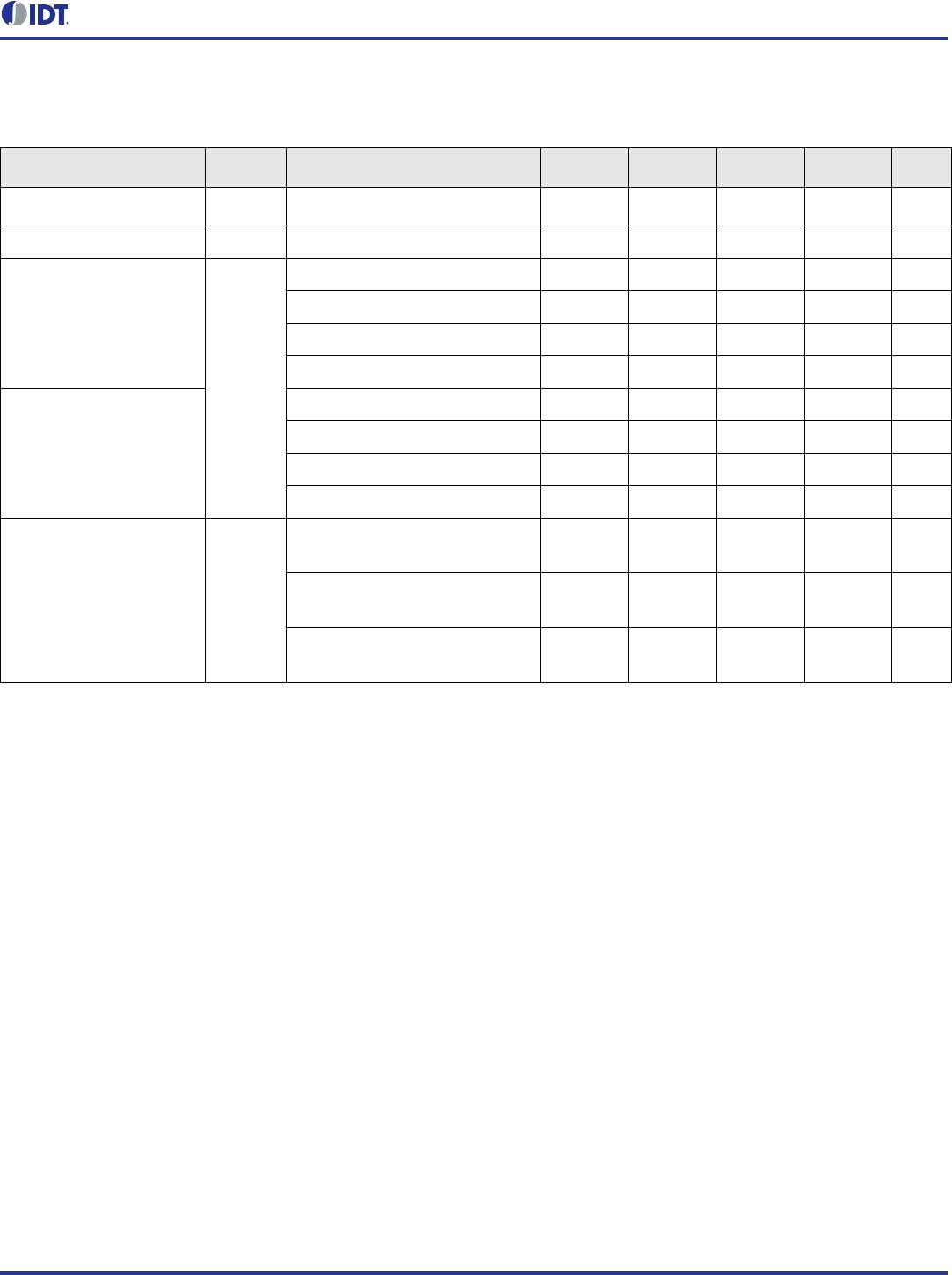

Table 12. Current Consumption

V

DDO

= 3.3V ±5%, 2.5V ±5%, 1.8V ±5%, T

A

= -40°C to +85°C unless stated otherwise.

Parameter Symbol Conditions Minimum Typical Maximum Units Notes

V

DDREF

Supply Current

I

DDREF

50MHz REFCLK. 5 8 mA

Core Supply Current I

DDCORE

2500MHz VCO, 50MHz REFCLK. 24 31 mA 3

Output Buffer Supply

Current (V

DDO1

)

I

DDO

x

LVDS, 325MHz. 22 28 mA 2

LP-HCSL, 100MHz. 17 24 mA 2

LVCMOS, 50MHz. 15 20 mA 1,2

LVCMOS, 200MHz. 25 40 mA 1,2

Output Buffer Supply

Current (V

DDO0)

LVDS, 325MHz. 8 12 mA 2

LP-HCSL. 6 10 mA 2

LVCMOS, 50MHz. 4 7 mA 1,2

LVCMOS, 200MHz. 13 26 mA 1,2

Total Power Down Current I

DDPD

Programmable outputs in HCSL

mode, B37[6,0] = 0.

710mA2

Programmable outputs in LVDS

mode, B37[6,0] = 0.

16 21 mA 2

Programmable outputs in

LVCMOS1 mode, B37[6,0] = 0.

57mA2