6©2018 Integrated Device Technology, Inc. May 30, 2018

9FGV1005 Datasheet

1

Practical lower frequency is determined by loop filter settings.

2

Includes loading the configuration bits from OTP to registers.

3

Actual PLL lock time depends on the loop configuration.

4

Actual jitter is configuration dependent. These values are representative of what the device can achieve.

5

Input doubler off. Maximum input frequency with input doubler on is 160MHz.

1

This configuration used for 12kHz–20MHz phase jitter measurement.

2

This configuration used for PCIe filtered phase jitter measurements.

3

Outputs configured as LP-HCSL or LVDS with REF output off, unless noted.

Programmable

Capacitance at XIN and

XO (XIN in parallel with

XO)

C

L

XIN/CLKIN, XO. 0 8 pF

Input Duty Cycle t2 CLKIN, measured at V

DDREF

/2. 40 50 60 %

Output Duty Cycle t3

LVCMOS, f

OUT

> 156.25MHz. 40 50 60 %

LVCMOS, f

OUT

≤ 156.25MHz. 45 50 55 %

LVDS, LP-HCSL outputs. 45 50.2 55 %

Clock Jitter t6

Cycle-to-cycle jitter (peak-to-peak),

See “Test Frequencies for Jitter

Measurements in Common Electrical

Characteristics” for configurations.

30 50 ps 4

Reference clock RMS phase jitter

(12kHz to 5MHz integration range).

See “Test Frequencies for Jitter

Measurements in Common Electrical

Characteristics” for configurations.

284

fs

rms

4

OUTx RMS phase jitter(12kHz to

20MHz integration range) differential

output. See “Test Frequencies for

Jitter Measurements in Common

Electrical Characteristics” for

configurations.

259

fs

rms

4

Output Skew t7

Skew between the same frequencies,

with outputs using the same driver

format.

37 50 ps

Lock Time t8 PLL lock time from power-up. 5 10 ms 2,3

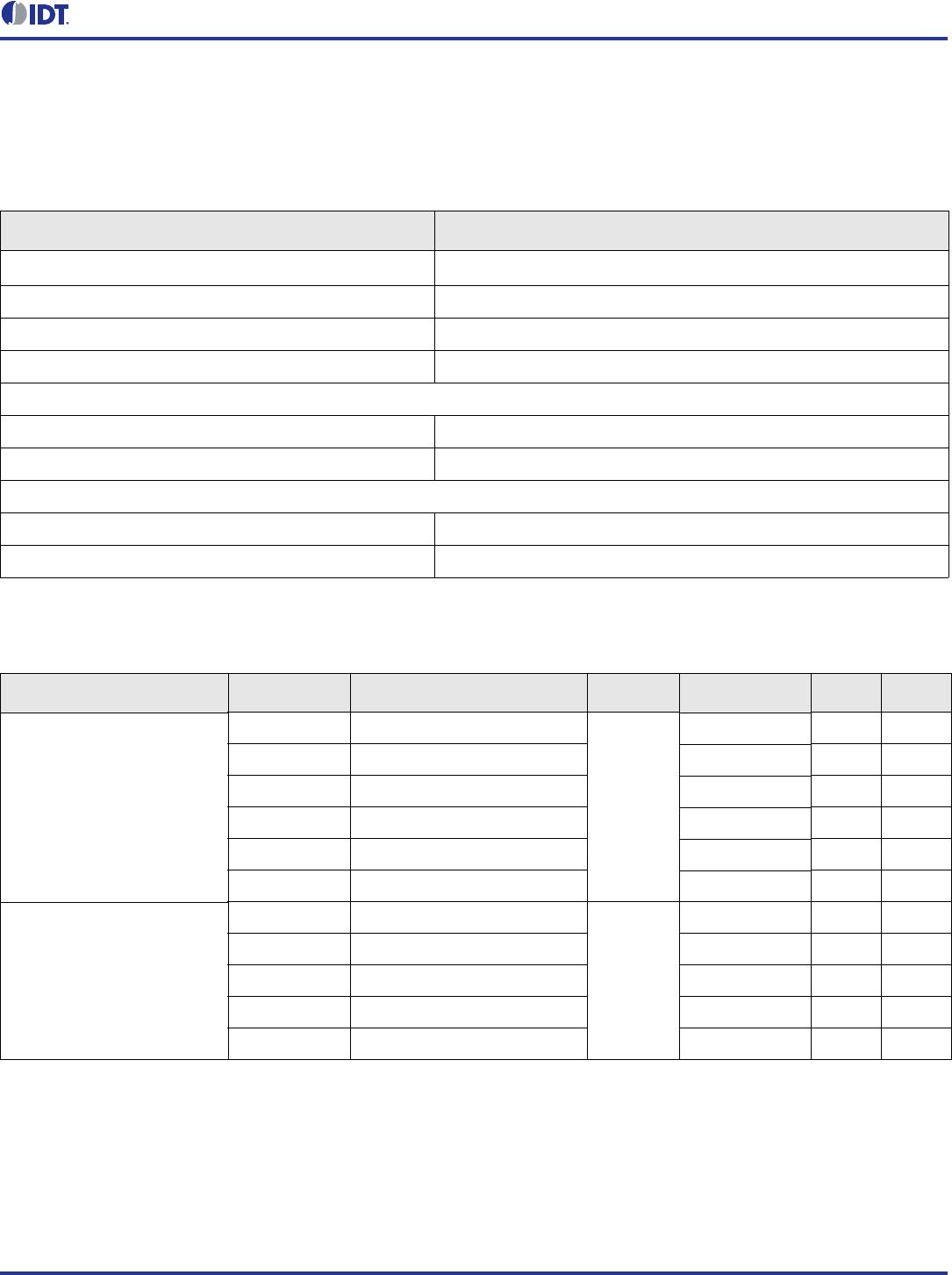

Table 6. Test Frequencies for Jitter Measurements in Common Electrical Characteristics Table

V

DDx

= 3.3V ±5%, 2.5V ±5%, 1.8V ±5%, T

A

= -40°C to +85°C unless stated otherwise.

Device XIN/CLKIN OUT0 OUT1 Unit Notes

9FGV1005 50 156.25 MHz 1,3

9FGV1005Q5 50 100 MHz 2,3

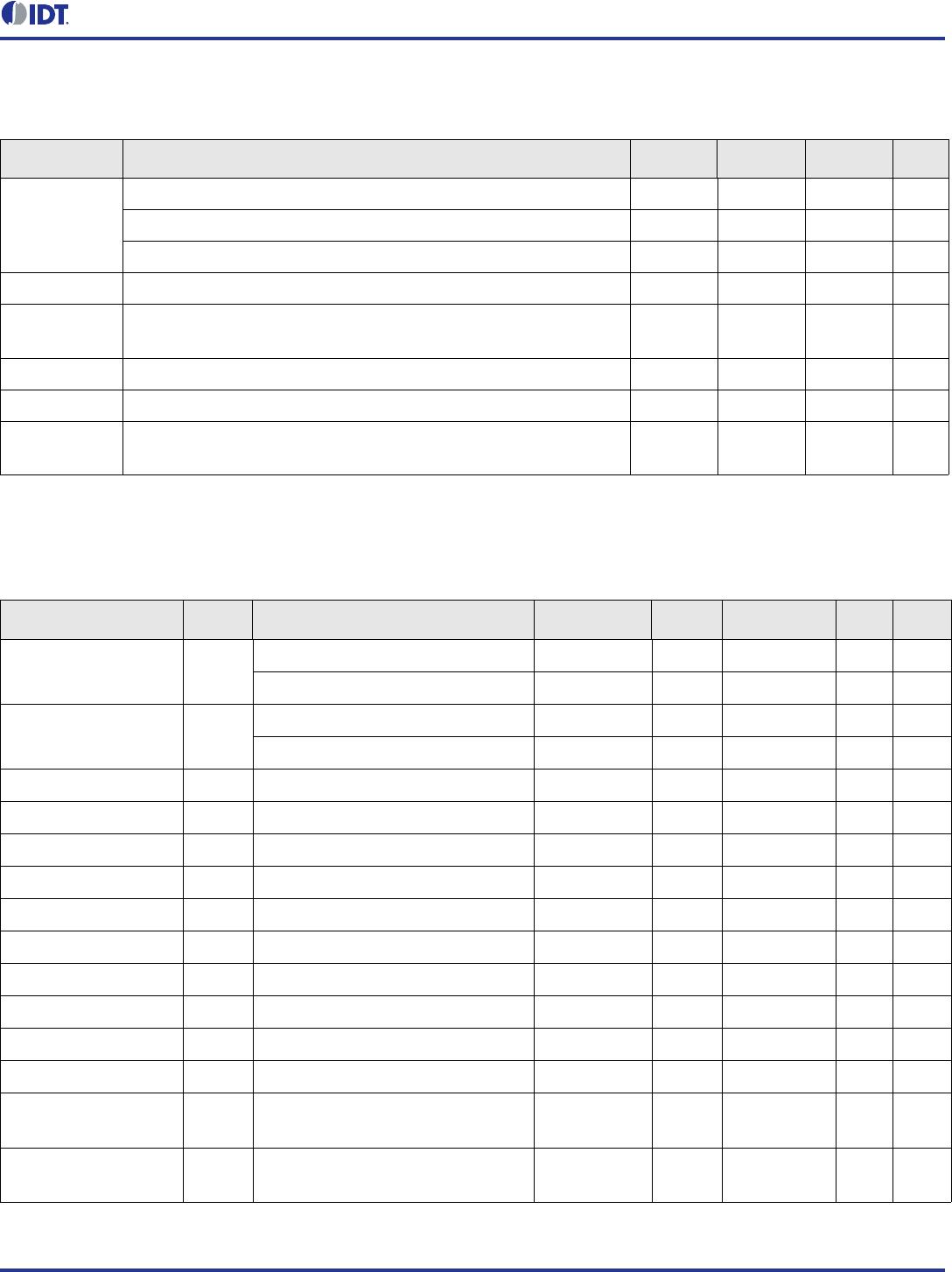

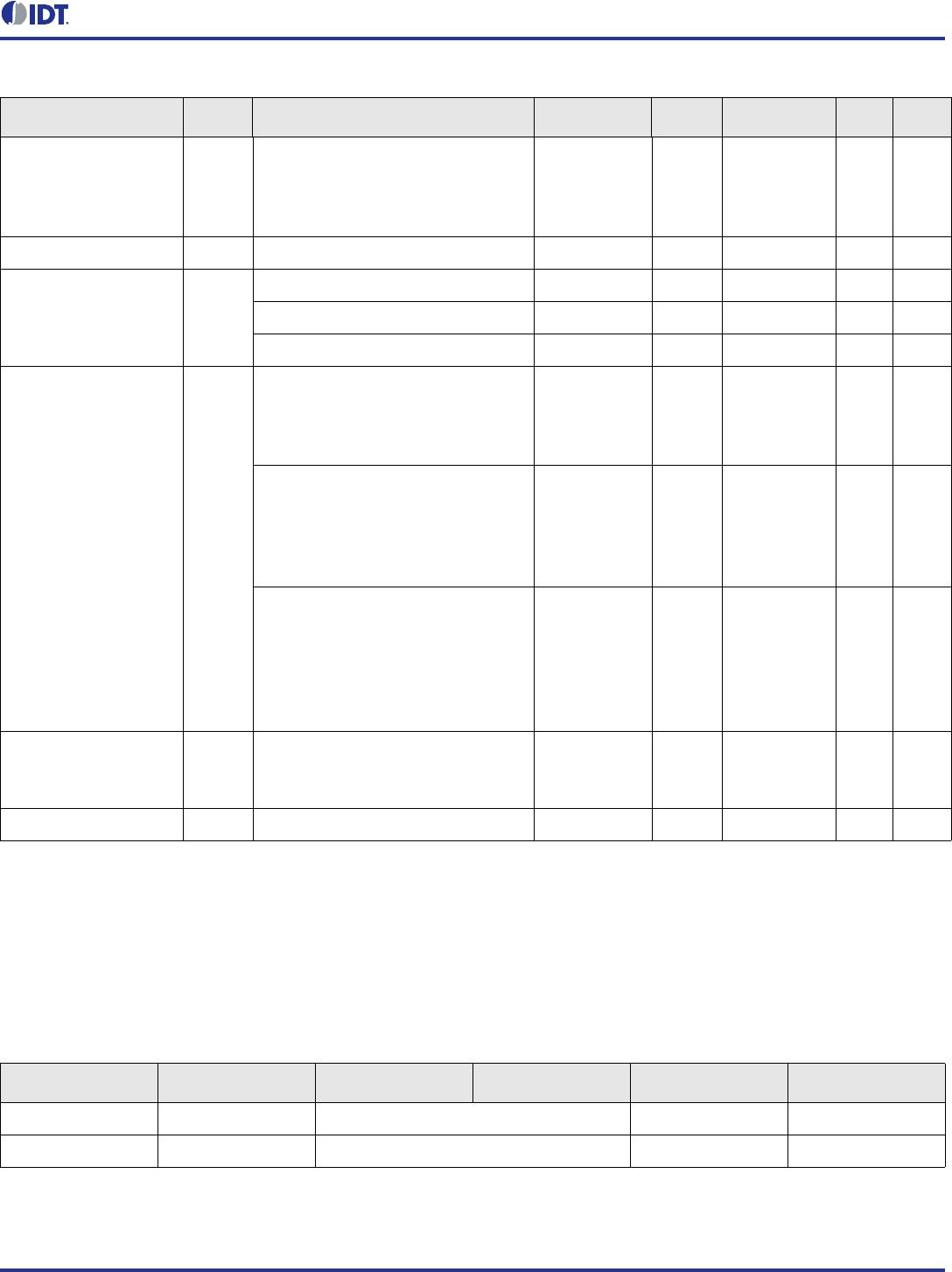

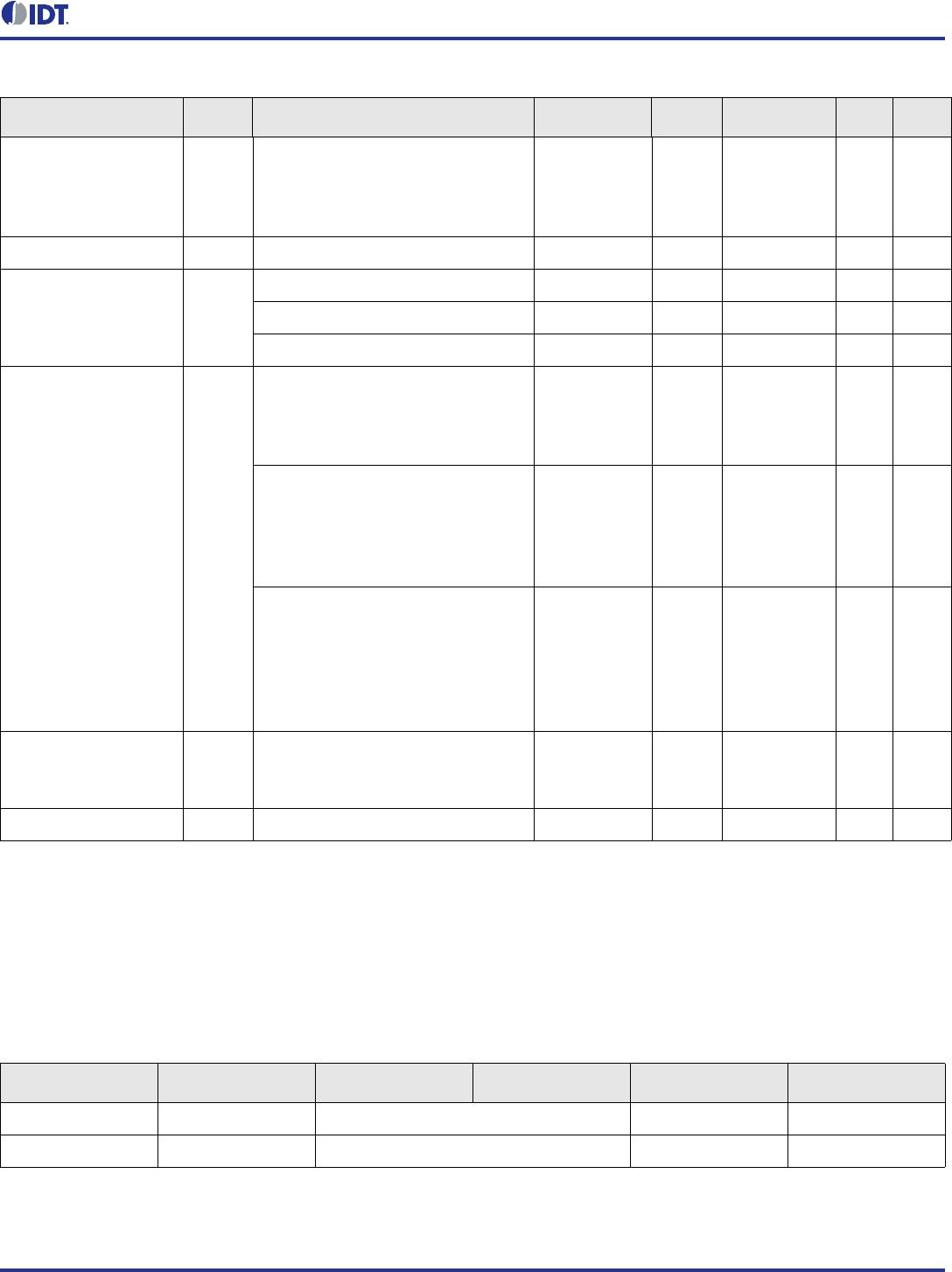

Table 5. Common Electrical Characteristics (Cont.)

Parameter Symbol Conditions Minimum Typical Maximum Units Notes