LC717A00AR

www.onsemi.com

2

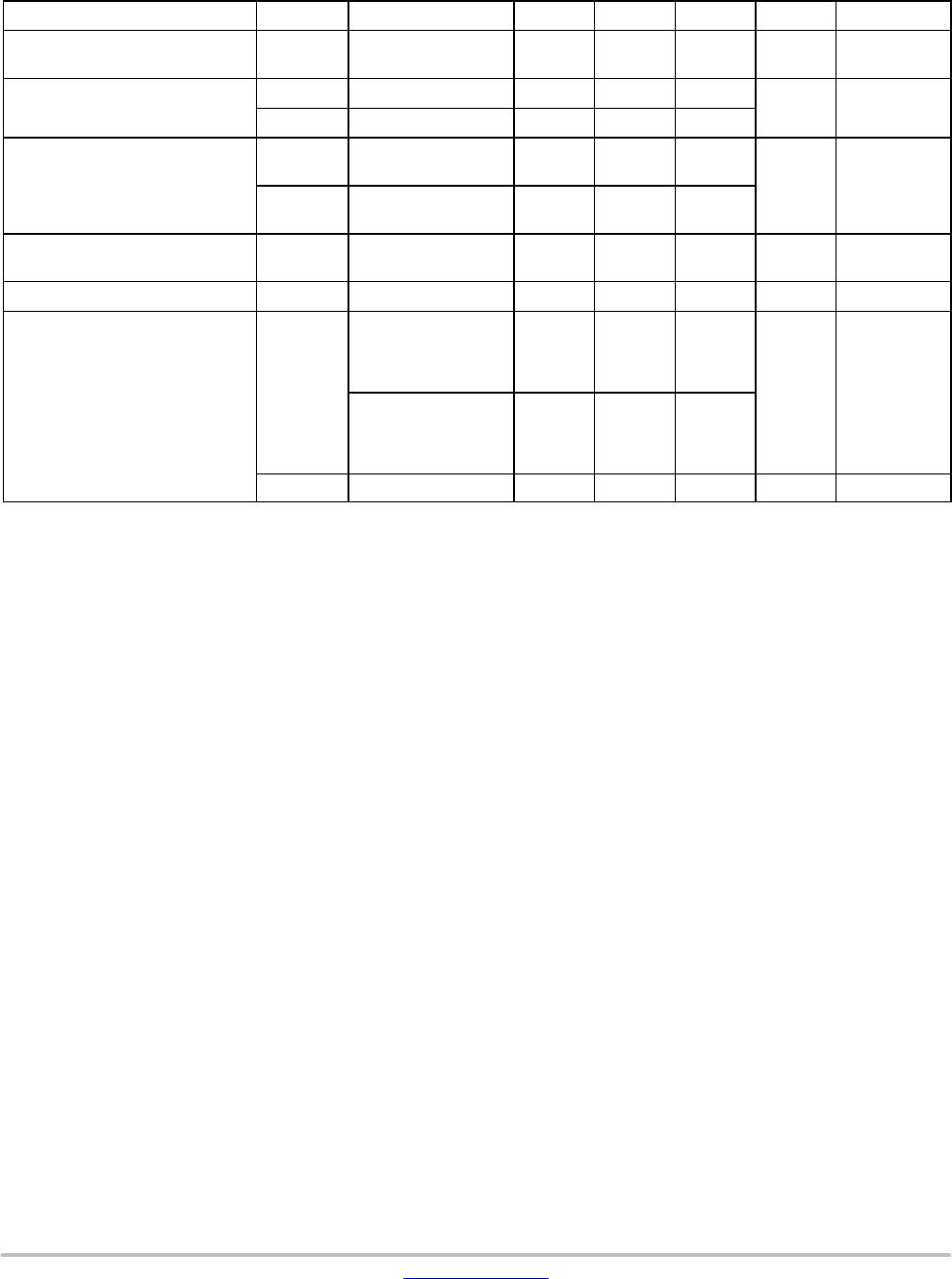

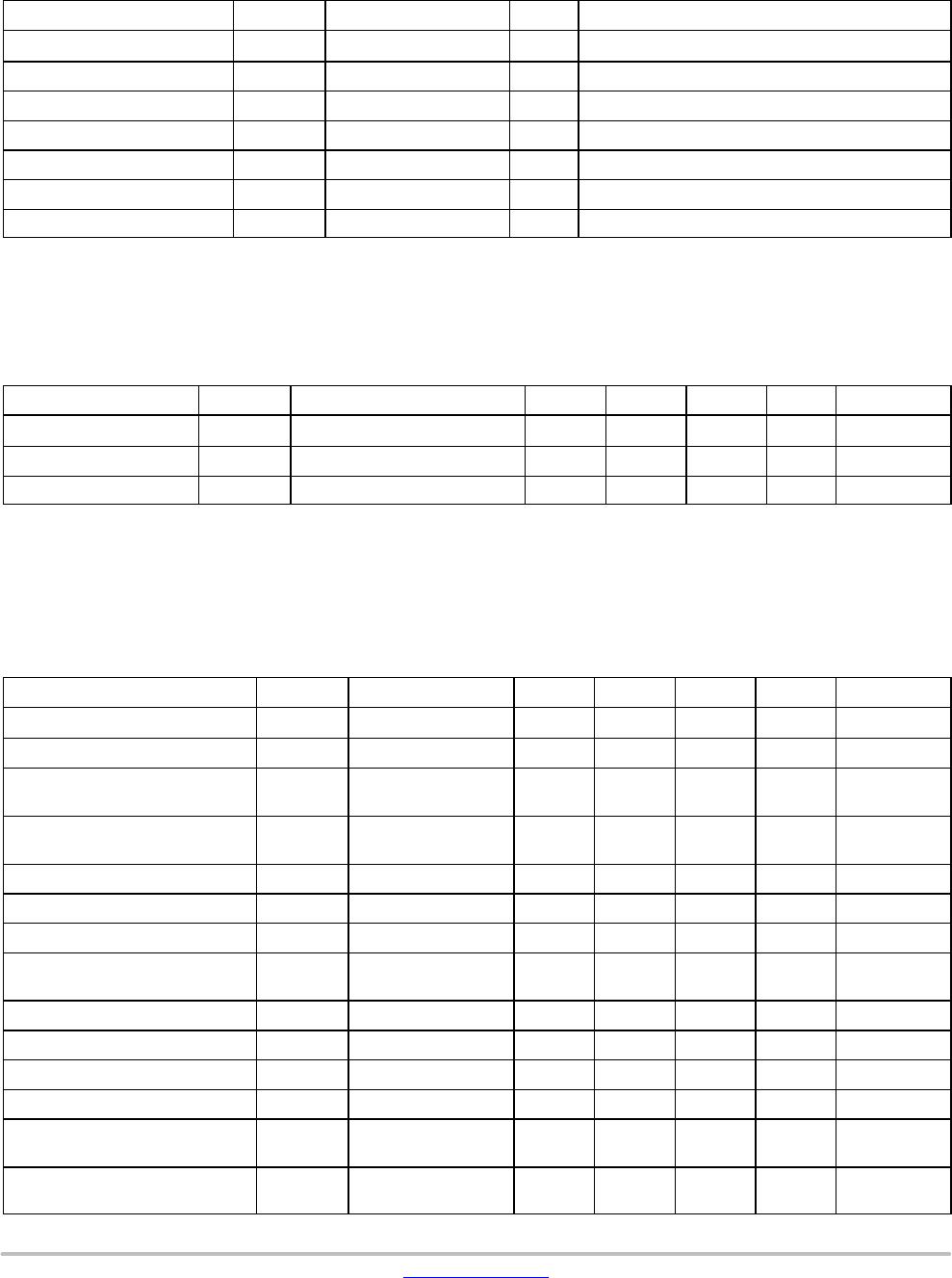

Specifications

Table 1. ABSOLUTE MAXIMUM RATINGS

(T

A

= 25°C, V

SS

= 0 V)

Parameter Symbol Ratings Unit Remarks

Supply Voltage V

DD

−0.3 to +6.5 V

Input Voltage V

IN

−0.3 to V

DD

+ 0.3 V (Note 1)

Output Voltage V

OUT

−0.3 to V

DD

+ 0.3 V (Note 2)

Power Dissipation P

d

max

160 mW

T

A

= +105_C, Mounted on a substrate (Note 3)

Peak Output Current I

OP

±8 mA Per terminal, 50% Duty ratio (Note 2)

Total Output Current I

OA

±40 mA Output total value of LSI, 25% Duty ratio

Storage Temperature T

stg

−55 to +125

_C

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. Apply to Cin0 to 7, Cref, nRST, SCL, SDA, SA, SCK, SI, nCS, GAIN.

2. Apply to Cdrv, Pout0 to 7, SDA, SO, ERROR, INTOUT.

3. 4-layer glass epoxy board (40 × 50 × 0.8t mm).

Table 2. RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Conditions Min Typ Max Unit Remarks

Operating Supply Voltage V

DD

2.6 − 5.5 V

Supply Ripple + Noise V

PP

− − ±20 mV (Note 4)

Operating Temperature T

opr

−40 25 105

_C

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond

the Recommended Operating Ranges limits may affect device reliability.

4. Inserting a high-valued capacitor and a low-valued capacitor in parallel between V

DD

and V

SS

is recommended. In this case, the small-valued

capacitor should be at least 0.1 mF, and is mounted near the LSI.

Table 3. ELECTRICAL CHARACTERISTICS

(V

SS

= 0 V, V

DD

= 2.6 to 5.5 V, T

A

= −40 to +105°C, Unless otherwise specified, the Cdrv drive frequency is f

CDRV

= 143 kHz.

Not tested at low temperature before shipment.)

Parameter Symbol Conditions Min Typ Max Unit Remarks

Capacitance Detection Resolution N − − 8 bit

Output Noise RMS N

RMS

Minimum gain setting − − ±1.0 LSB (Notes 5, 7)

Input Offset Capacitance

Adjustment Range

Coff

RANGE

− ±8.0 −

pF

(Notes 5, 7)

Input Offset Capacitance

Adjustment Resolution

Coff

RESO

− 8 −

bit

Cin Offset Drift Cin

DRIFT

Minimum gain setting − − ±8

LSB

(Note 5)

Cin Detection Sensitivity Cin

SENSE

Minimum gain setting 0.04 − 0.12

LSB/fF

(Note 6)

Cin Pin Leak Current I

Cin

Cin = Hi−Z − ±25 ±500

nA

Cin Allowable Parasitic Input

Capacitance

Cin

SUB

Cin against V

SS

− − 30

pF

(Notes 5, 7)

Cdrv Drive Frequency f

CDRV

100 143 186

kHz

Cdrv Pin Leak Current I

CDRV

Cdrv = Hi−Z − ±25 ±500

nA

nRST Minimum Pulse Width t

NRST

1 − −

ms

Power-on Reset Time t

POR

− − 20 ms

Power-on Reset Operation

Condition: Hold Time

t

POROP

10 − − ms (Note 5)

Power-on Reset Operation

Condition: Input Voltage

V

POROP

− − 0.1 V (Note 5)