13

LTC3404

3404fb

APPLICATIO S I FOR ATIO

WUUU

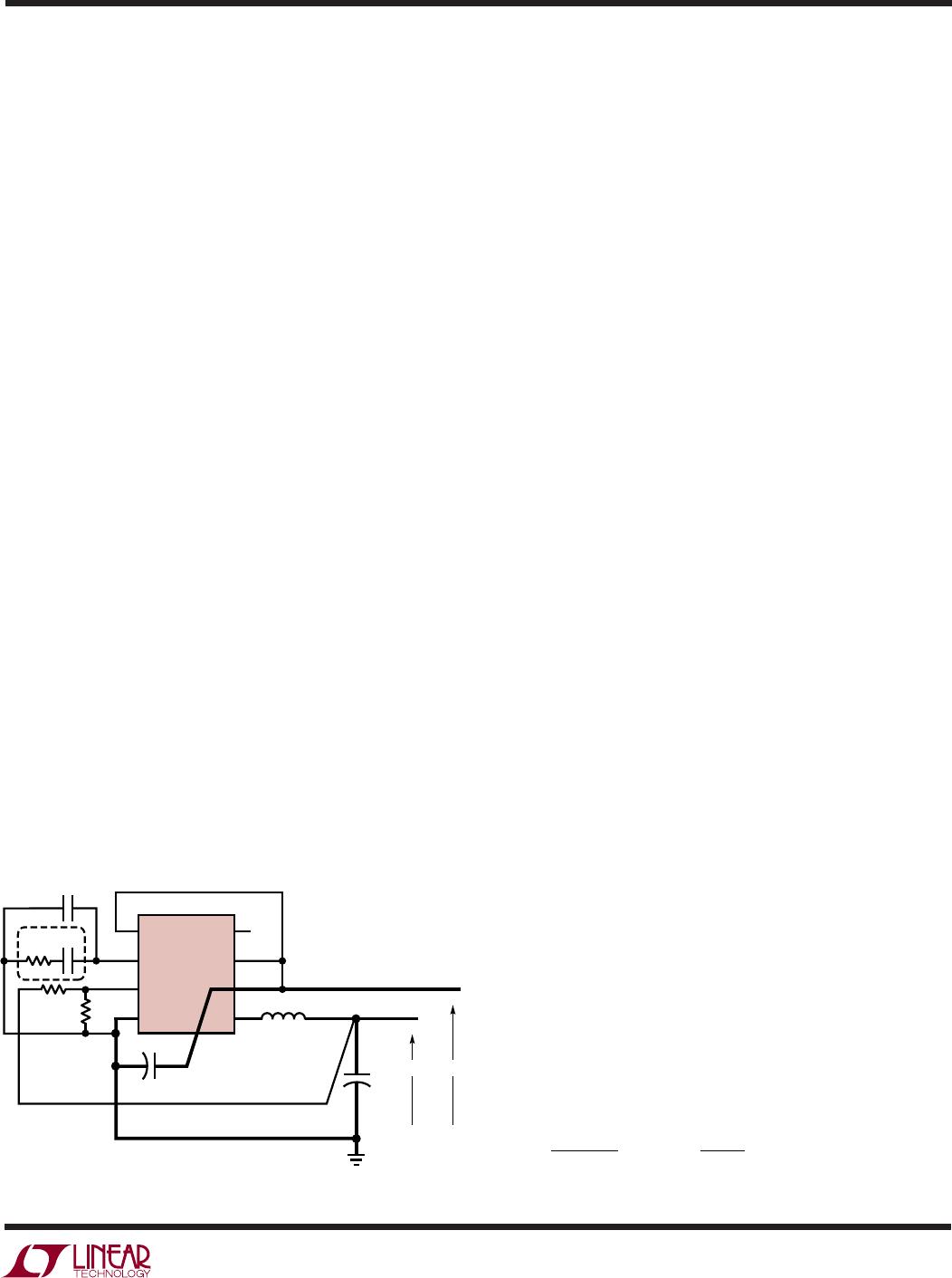

Figure 7. LTC3404 Layout Diagram

–

+

RUN

I

TH

V

FB

GND

PLL LPF

SYNC/MODE

SW

LTC3404

C

C2

C

C1

R

C

C

OUT

3404 F07

L1

V

IN

BOLD LINES INDICATE

HIGH CURRENT PATHS

1

2

3

4

8

7

6

5

OPTIONAL

+

–

+

V

OUT

V

IN

R2

C

IN

+

R1

which is below the maximum junction temperature of

125°C.

Note that at higher supply voltages, the junction tempera-

ture is lower due to reduced switch resistance (R

DS(ON)

).

Checking Transient Response

The regulator loop response can be checked by looking at

the load transient response. Switching regulators take

several cycles to respond to a step in load current. When

a load step occurs, V

OUT

immediately shifts by an amount

equal to (ΔI

LOAD

• ESR), where ESR is the effective series

resistance of C

OUT

. ΔI

LOAD

also begins to charge or

discharge C

OUT

, which generates a feedback error signal.

The regulator loop then acts to return V

OUT

to its steady-

state value. During this recovery time V

OUT

can be moni-

tored for overshoot or ringing that would indicate a stabil-

ity problem. The internal compensation provides adequate

compensation for most applications. But if additional

compensation is required, the I

TH

pin can be used for

external compensation using R

C

, C

C1

as shown in

Figure 7. (The 47pF capacitor, C

C2

, is typically needed for

noise decoupling.)

A second, more severe transient is caused by switching in

loads with large (>1μF) supply bypass capacitors. The

discharged bypass capacitors are effectively put in parallel

with C

OUT

, causing a rapid drop in V

OUT

. No regulator can

deliver enough current to prevent this problem if the load

switch resistance is low and it is driven quickly. The only

solution is to limit the rise time of the switch drive so that

the load rise time is limited to approximately (25 • C

LOAD

).

Thus, a 10μF capacitor charging to 3.3V would require a

250μs rise time, limiting the charging current to about

130mA.

PC Board Layout Checklist

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation of the

LTC3404. These items are also illustrated graphically in

the layout diagram of Figure 7. Check the following in your

layout:

1. Are the signal and power grounds segregated? The

LTC3404 signal ground consists of the resistive

divider, the optional compensation network (R

C

and

C

C1

) and C

C2

. The power ground consists of the (–)

plate of C

IN

, the (–) plate of C

OUT

and Pin 4 of the

LTC3404. The power ground traces should be kept

short, direct and wide. The signal ground and power

ground should converge to a common node in a star-

ground configuration.

2. Does the V

FB

pin connect directly to the feedback

resistors? The resistive divider R1/R2 must be con-

nected between the (+) plate of C

OUT

and signal ground.

3. Does the (+) plate of C

IN

connect to V

IN

as closely as

possible? This capacitor provides the AC current to the

internal power MOSFETs.

4. Keep the switching node SW away from sensitive small

signal nodes.

Design Example

As a design example, assume the LTC3404 is used in a

single lithium-ion battery-powered cellular phone applica-

tion. The input voltage will be operating from a maximum

of 4.2V down to about 2.7V. The load current requirement

is a maximum of 0.3A but most of the time it will be in

standby mode, requiring only 2mA. Efficiency at both low

and high load currents is important. Output voltage is

2.5V. With this information we can calculate L using

equation (1),

L

fI

V

V

V

L

OUT

OUT

IN

=

()

Δ

()

−

⎛

⎝

⎜

⎞

⎠

⎟

1

1

(3)