8

LTC3404

3404fb

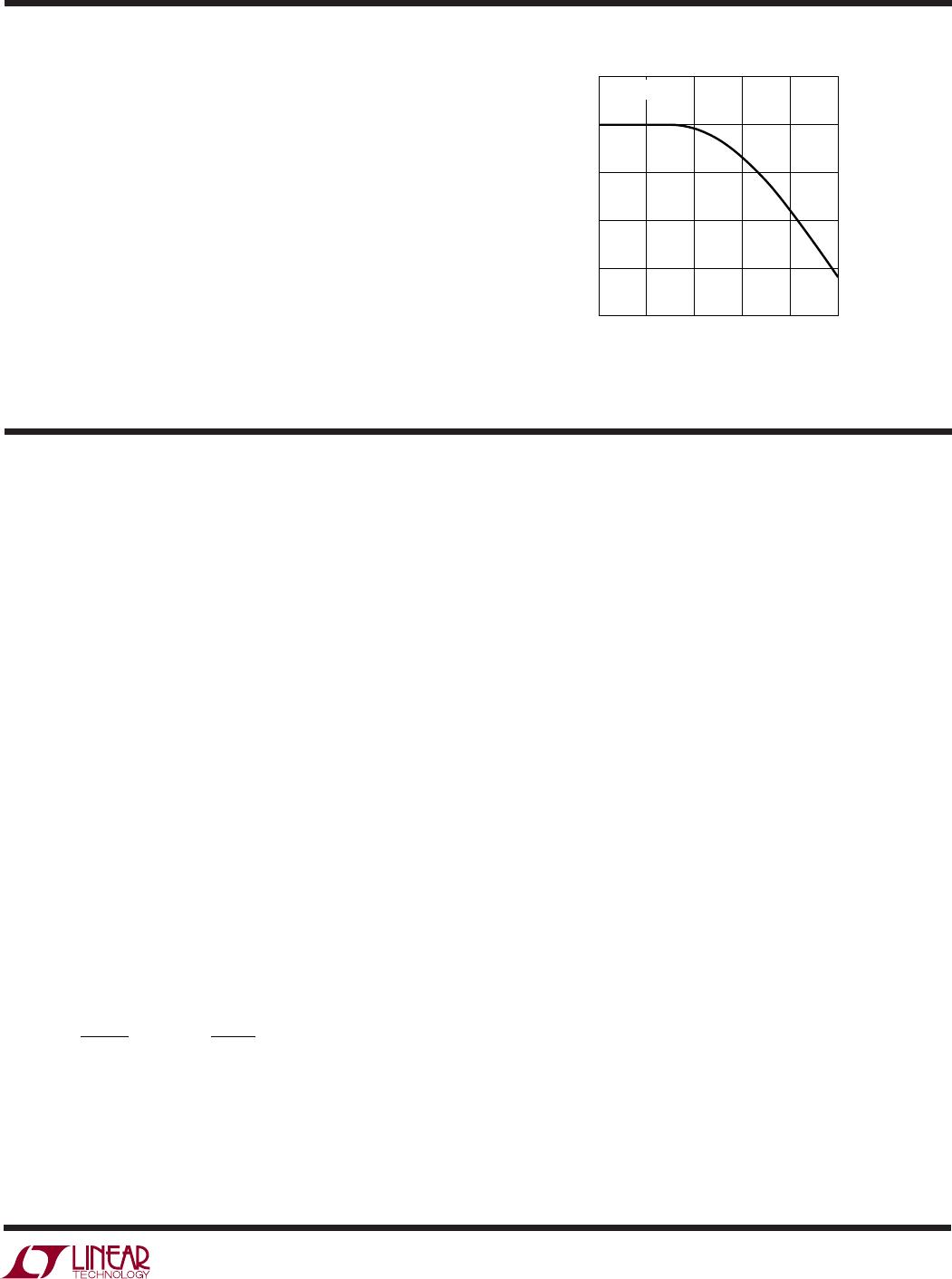

Figure 1. Maximum Output Current vs Input Voltage

SUPPLY VOLTAGE (V)

2.5

MAXIMUM OUTPUT CURRENT (mA)

1200

1000

800

600

400

200

0

3.5 4.5 5.5 6.5

3404 • F01

7.5

L = 4.7μH

V

OUT

= 3.3V

V

OUT

= 2.5V

V

OUT

= 1.5V

OPERATIO

U

When the converter is in Burst Mode operation, the peak

current of the inductor is set to approximately 250mA,

even though the voltage at the I

TH

pin indicates a lower

value. The voltage at the I

TH

pin drops when the inductor’s

average current is greater than the load requirement. As

the I

TH

voltage drops below approximately 0.55V, the

BURST comparator trips, causing the internal sleep line to

go high and forces off both power MOSFETs. The I

TH

pin

is then disconnected from the output of the EA amplifier

and held a diode voltage (0.7V) above ground.

In sleep mode, both power MOSFETs are held off and a

majority of the internal circuitry is partially turned off,

reducing the quiescent current to 10μA. The load current

is now being supplied solely from the output capacitor.

When the output voltage drops, the I

TH

pin reconnects to

the output of the EA amplifier and the top MOSFET is again

turned on and this process repeats.

Short-Circuit Protection

When the output is shorted to ground, the frequency of the

oscillator is reduced to about 200kHz, 1/7 the nominal

frequency. This frequency foldback ensures that the

inductor current has ample time to decay, thereby prevent-

ing runaway. The oscillator’s frequency will progressively

increase to 1.4MHz (or the synchronized frequency) when

V

FB

rises above 0.3V.

Frequency Synchronization

A phase-locked loop (PLL) is available on the LTC3404 to

allow the internal oscillator to be synchronized to an

external source connected to the SYNC/MODE pin. The

output of the phase detector at the PLL LPF pin operates

over a 0V to 2.4V range corresponding to 1MHz to 1.7MHz.

When locked, the PLL aligns the turn-on of the top MOS-

FET to the rising edge of the synchronizing signal.

When the LTC3404 is clocked by an external source, Burst

Mode operation is disabled; the LTC3404 then operates in

PWM pulse skipping mode. In this mode, when the output

load is very low, current comparator I

COMP

may remain

tripped for several cycles and force the main switch to stay

off for the same number of cycles. Increasing the output

load slightly allows constant frequency PWM operation to

resume. This mode exhibits low output ripple as well as

low audio noise and reduced RF interference while provid-

ing reasonable low current efficiency.

Frequency synchronization is inhibited when the feedback

voltage V

FB

is below 0.6V. This prevents the external clock

from interfering with the frequency foldback for short-

circuit protection.

Dropout Operation

When the input supply voltage decreases toward the

output voltage, the duty cycle increases toward the maxi-

mum on-time. Further reduction of the supply voltage

forces the main switch to remain on for more than one

cycle until it reaches 100% duty cycle. The output voltage

will then be determined by the input voltage minus the

voltage drop across the internal P-channel MOSFET and

the inductor.

Low Supply Operation

The LTC3404 is designed to operate down to an input

supply voltage of 2.65V although the maximum allowable

output current is reduced at this low voltage. Figure 1

shows the reduction in the maximum output current as a

function of input voltage for various output voltages.

Another important detail to remember is that at low input

supply voltages, the R

DS(ON)

of the P-channel switch

increases. Therefore, the user should calculate the power

dissipation when the LTC3404 is used at 100% duty cycle

with a low input voltage (see Thermal Considerations in

the Applications Information section).