5

LTC1569-6

PIN FUNCTIONS

UUU

IN

+

/IN

–

(Pins 1, 2): Signals can be applied to either or

both input pins. The DC gain from IN

+

(Pin 1) to OUT

(Pin␣ 8) is 1.0, and the DC gain from Pin 2 to Pin 8 is –1. The

input range, input resistance and output range are de-

scribed in the Applications Information section. Input

voltages which exceed the power supply voltages should

be avoided. Transients will not cause latchup if the current

into/out of the input pins is limited to 20mA.

GND (Pin 3): The GND pin is the reference voltage for the

filter and should be externally biased to 2V (1.11V) to

maximize the dynamic range of the filter in applications

using a single 5V (3V) supply. For single supply operation,

the GND pin should be bypassed with a quality 1µF

ceramic capacitor to V

–

(Pin 4). The impedance of the

circuit biasing the GND pin should be less than 2kΩ as the

GND pin generates a small amount of AC and DC current.

For dual supply operation, connect Pin␣ 3 to a high quality

DC ground. A ground plane should be used. A poor ground

will increase DC offset, clock feedthrough, noise and

distortion.

V

–

/V

+

(Pins 4, 7): For 3V, 5V and ±5V applications a

quality 1µF ceramic bypass capacitor is required from V

+

(Pin 7) to V

–

(Pin 4) to provide the transient energy for the

internal clock drivers. The bypass should be as close as

possible to the IC. In dual supply applications (Pin 3 is

grounded), an additional 0.1µF bypass from V

+

(Pin 7) to

GND (Pin 3) and V

–

(Pin 4) to GND (Pin 3) is recom-

mended.

The maximum voltage difference between GND (Pin 3) and

V

+

(Pin 7) should not exceed 5.5V.

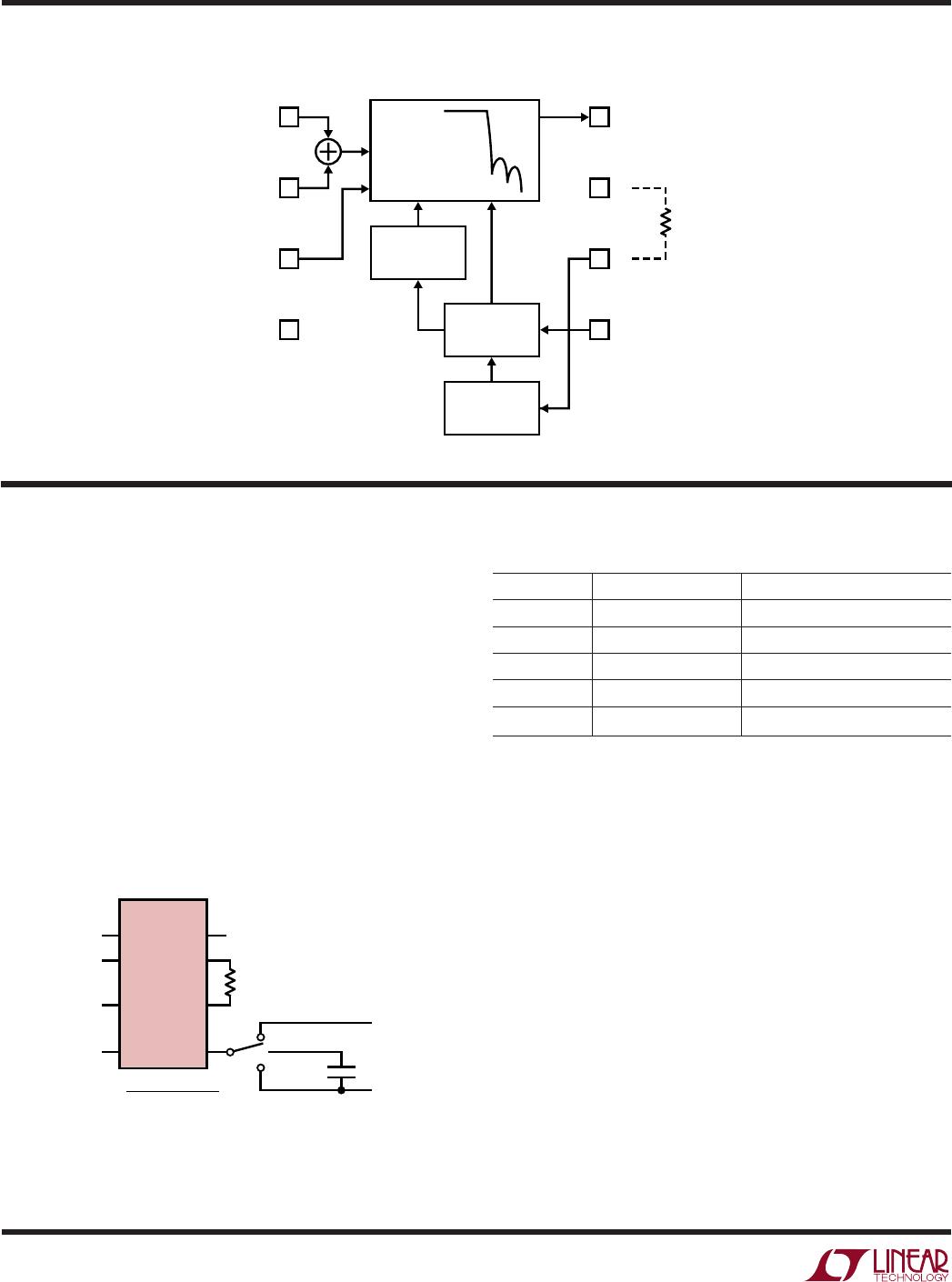

DIV/CLK (Pin 5): DIV/CLK serves two functions. When the

internal oscillator is enabled, DIV/CLK can be used to

engage an internal divider. The internal divider is set to 1:1

when DIV/CLK is shorted to V

–

(Pin 4). The internal divider

is set to 4:1 when DIV/CLK is allowed to float (a 100pF

bypass to V

–

is recommended). The internal divider is set

to 16:1 when DIV/CLK is shorted to V

+

(Pin 7). In the

divide-by-4 and divide-by-16 modes the power supply

current is reduced by as much as 40%.

When the internal oscillator is disabled (R

X

shorted

to V

–

) DIV/CLK becomes an input pin for applying an

external clock signal. For proper filter operation, the clock

waveform should be a squarewave with a duty cycle as

close as possible to 50% and CMOS voltages levels (see

Electrical Characteristics section for voltage levels). DIV/

CLK pin voltages which exceed the power supply voltages

should be avoided. Transients will not cause latchup if the

fault current into/out of the DIV/CLK pin is limited to 40mA.

R

X

(Pin 6): Connecting an external resistor between the R

X

pin and V

+

(Pin 7) enables the internal oscillator. The value

of the resistor determines the frequency of oscillation. The

maximum recommended resistor value is 40k and the

minimum is 3.8k. The internal oscillator is disabled by

shorting the R

X

pin to V

–

(Pin 4). (Please refer to the

Applications Information section.)

OUT (Pin 8): Filter Output. This pin can drive 10kΩ and/or

40pF loads. For larger capacitive loads, an external 100Ω

series resistor is recommended. The output pin can ex-

ceed the power supply voltages by up to ±2V without

latchup.