9

LTC1569-6

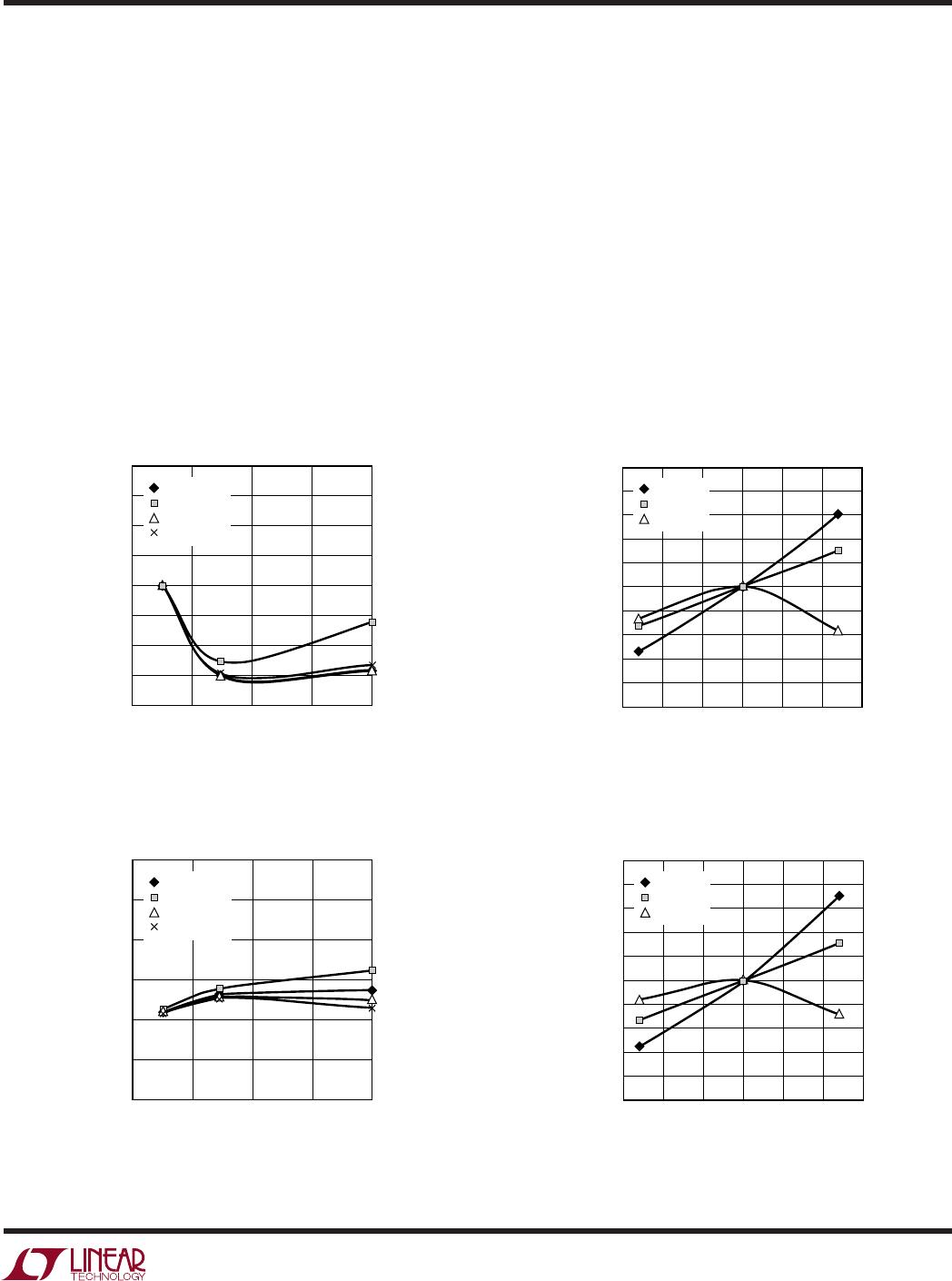

DC Accuracy

DC accuracy is defined as the error in the output voltage

after DC offset and DC gain errors are removed. This is

similar to the definition of the integral nonlinearity in A/D

converters. For example, after measuring values of V

OUT(DC)

vs V

IN(DC)

for a typical LTC1569-6, a linear regression

shows that V

OUT(DC)

= V

IN(DC)

• 0.99854 + 0.00134V is the

straight line that best fits the data. The DC accuracy

describes how much the actual data deviates from this

straight line (i.e., DCERROR = V

OUT(DC)

– (V

IN(DC)

• 0.99854

+ 0.00134V). In a 12-bit system with a full-scale value of

2V, the LSB is 488µV. Therefore, if the DCERROR of the

filter is less than 488µV over a 2V range, the filter has

12-bit DC accuracy. Figure 9 illustrates the typical DC

accuracy of the LTC1569-6 on a single 5V supply.

DC Offset

The output DC offset of the LTC1569-6 is trimmed to less

than ±5mV. The trimming is performed with V

S

= 1.9V,

–1.1V with the filter cutoff frequency set to 4kHz (R

EXT

=

10k, DIV/CLK shorted to V

+

). To obtain optimum DC offset

performance, appropriate PC layout techniques should be

used. The filter IC should be soldered to the PC board. The

power supplies should be well decoupled including a 1µF

ceramic capacitor from V

+

(Pin 7) to V

–

(Pin 4). A ground

plane should be used. Noisy signals should be isolated

from the filter input pins.

When the power supply is 3V, the output DC offset should

change less than ±2mV when the clock frequency varies

from 64kHz to 4096kHz. When the clock frequency is

fixed, the output DC offset will typically change by less

than ±3mV (±15mV) when the power supply varies from

3V to 5V (±5V) in the divide-by-1 mode. In the divide-by-

4 or divide-by-16 modes, the output DC offset will typically

change less than –9mV (–27mV) when the power supply

varies from 3V to 5V (±5V). The offset is measured with

respect to GND (Pin 3).

Aliasing

Aliasing is an inherent phenomenon of sampled data

filters. In lowpass filters significant aliasing only occurs

when the frequency of the input signal approaches the

sampling frequency or multiples of the sampling fre-

APPLICATIONS INFORMATION

WUU

U

f

CUTOFF

), as shown in the Typical Applications section. The

typical variation in dynamic input impedance for a given

clock frequency is ±10%.

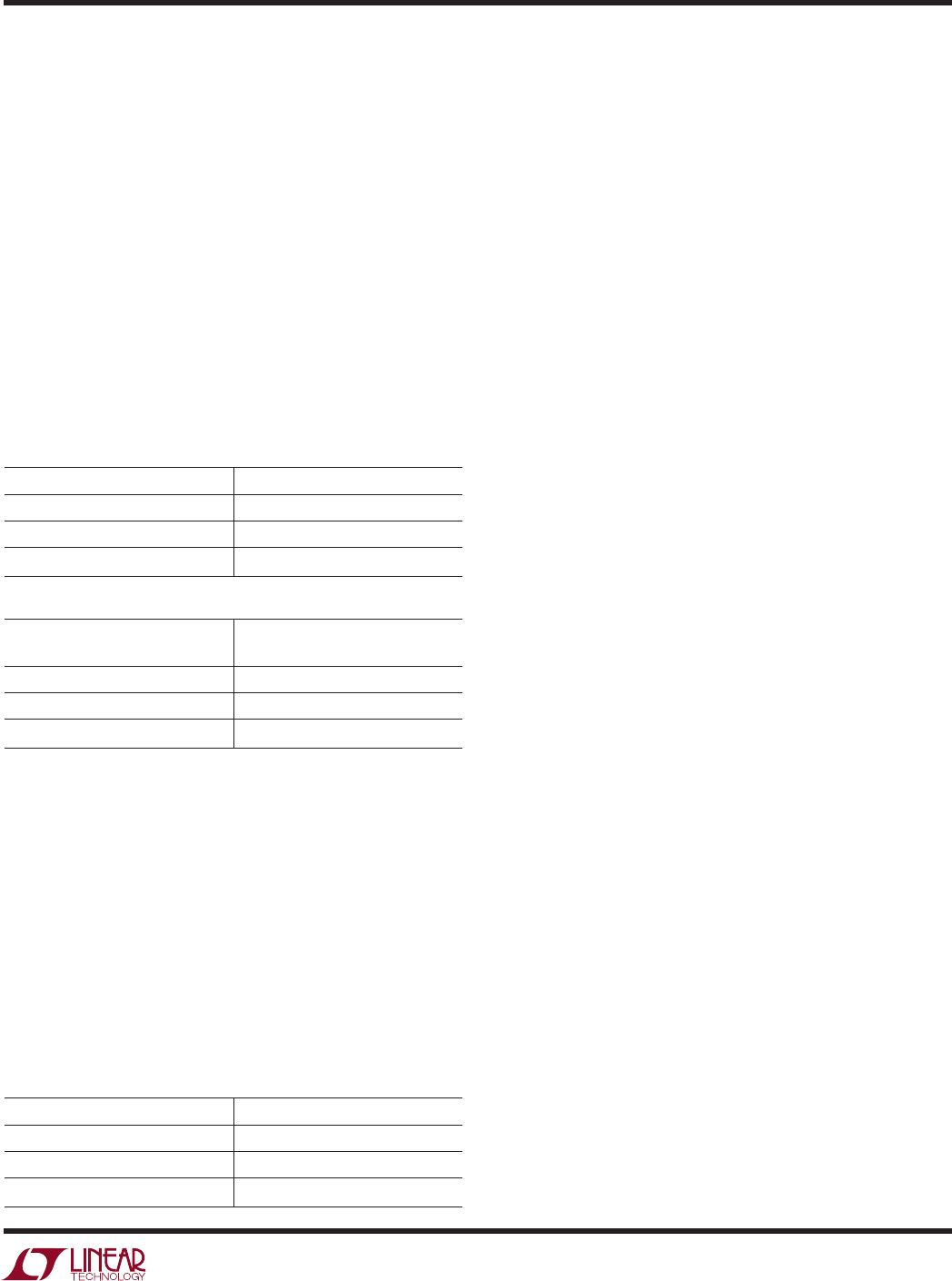

Wideband Noise

The wideband noise of the filter is the RMS value of the

device’s output noise spectral density. The wideband

noise data is used to determine the operating signal-to-

noise at a given distortion level. The wideband noise is

nearly independent of the value of the clock frequency and

excludes the clock feedthrough. Most of the wideband

noise is concentrated in the filter passband and cannot be

removed with post filtering (Table 2). Table 3 lists the

typical wideband noise for each supply.

Table 2. Wideband Noise vs Supply Voltage, Single 3V Supply

Bandwidth Total Integrated Noise

DC to f

CUTOFF

80µV

RMS

DC to 2 • f

CUTOFF

95µV

RMS

DC to f

CLK

110µV

RMS

Table 3. Wideband Noise vs Supply Voltage, f

CUTOFF

= 64kHz

Total Integrated Noise

Power Supply DC to 2 • f

CUTOFF

3V 95µV

RMS

5V 100µV

RMS

±5V 105µV

RMS

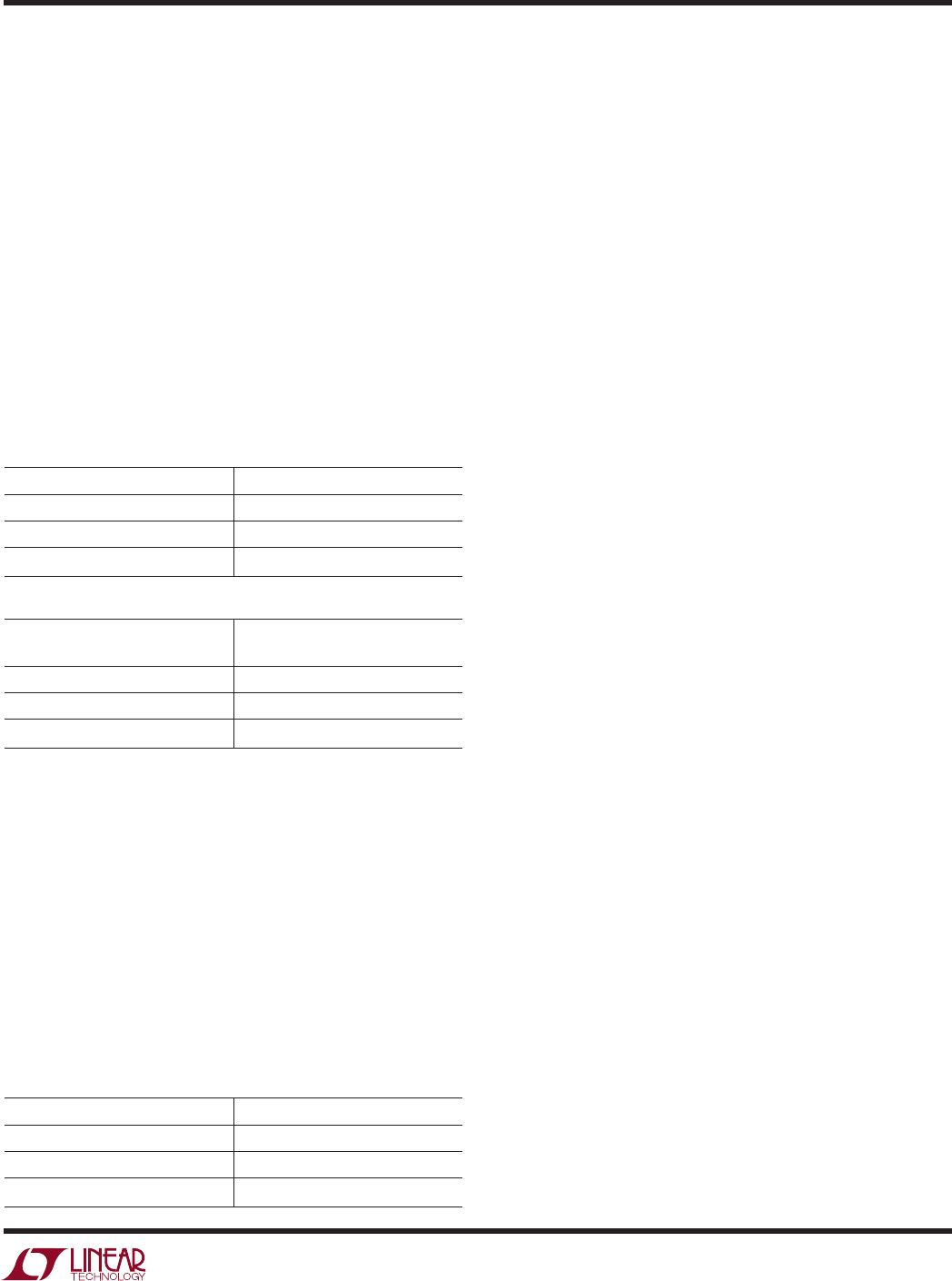

Clock Feedthrough

Clock feedthrough is defined as the RMS value of the clock

frequency and its harmonics that are present at the filter’s

OUT pin (Pin 8). The clock feedthrough is measured with

IN

+

and IN

–

(Pins 1 and 2) grounded and depends on the

PC board layout and the power supply decoupling. Table␣ 4

shows the clock feedthrough (the RMS sum of the first 11

harmonics) when the LTC1569-6 is self-clocked with

R

EXT

= 10k, DIV/CLK (Pin 5) open (divide-by-4 mode). The

clock feedthrough can be reduced with a simple RC post

filter.

Table 4. Clock Feedthrough

Power Supply Feedthrough

3V 0.1mV

RMS

5V 0.3mV

RMS

±5V 0.9mV

RMS