REV. A

AD7709

–22–

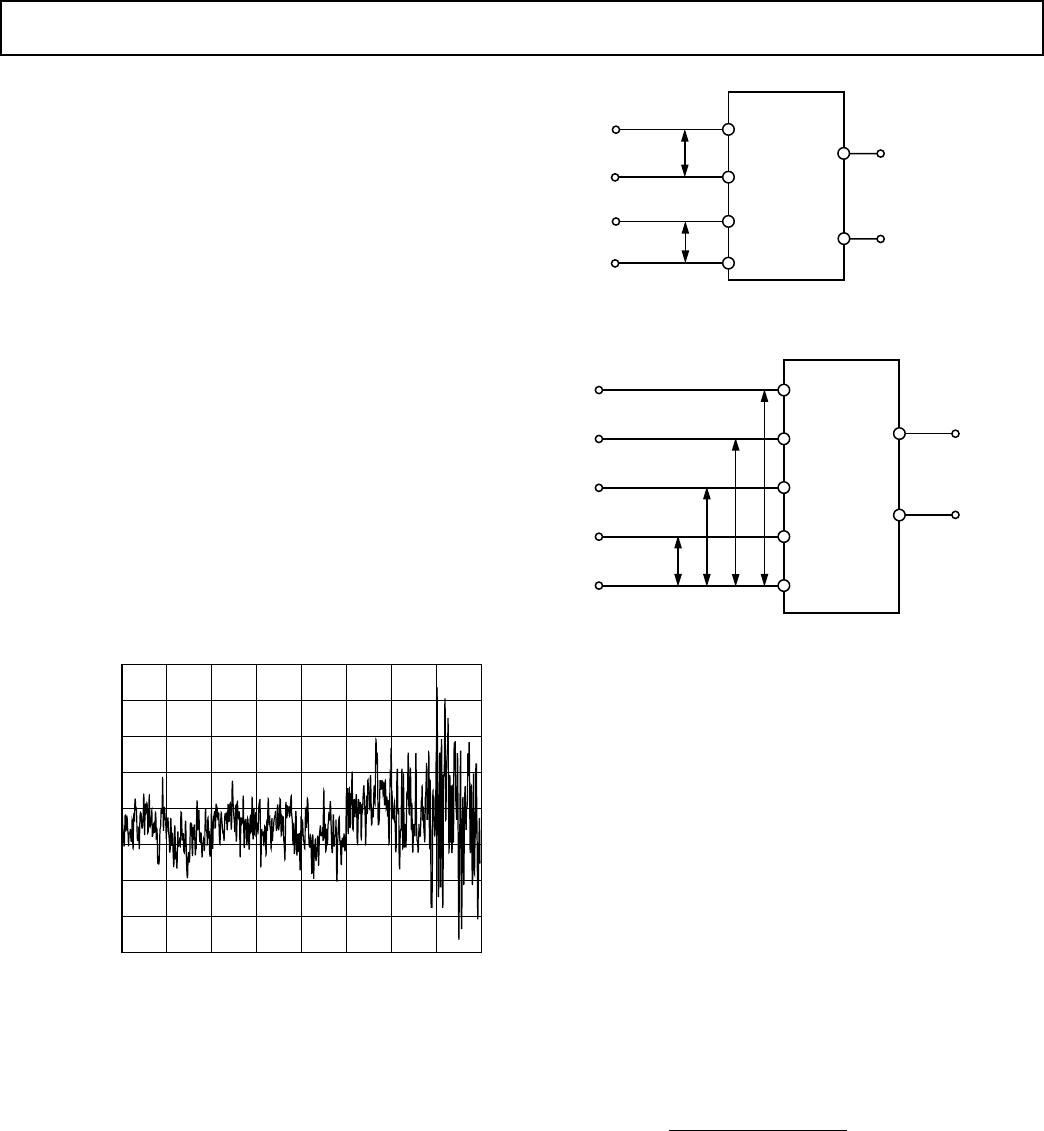

RDY output is connected to the IRQ2 input of the ADSP-2103/

ADSP-2105. The serial interface of the ADSP-2103/ADSP-2105

is set up for alternate framing mode. The RFS and TFS pins of

the ADSP-2103/ADSP-2105 are configured as active low

outputs and the ADSP-2103/ADSP-2105 serial clock line, SCLK,

is also configured as an output. The CS for the AD7709 is

active when either the RFS or TFS outputs from the ADSP-2103/

ADSP-2105 are active. The serial clock rate on the ADSP-2103/

ADSP-2105 should be limited to 3 MHz to ensure correct opera-

tion with the AD7709.

CIRCUIT DESCRIPTION

The AD7709 is a ⌺-⌬ A/D converter with on-chip digital filtering,

intended for the measurement of wide dynamic range, low

frequency signals such as those in weigh scale, pressure, tempera-

ture, industrial control, or process control applications. It employs

a ⌺-⌬ conversion technique to realize up to 16 bits of no-missing-

codes performance. The ⌺-⌬ modulator converts the sampled

input signal into a digital pulse train whose duty cycle contains

the digital information. A Sinc

3

programmable low-pass filter is

then employed to decimate the modulator output data stream to

give a valid data conversion result at programmable output rates

from 5.35 Hz (186.77 ms) to 105.03 Hz (9.52 ms). A chopping

scheme is also employed to minimize ADC offset and offset and

gain drift errors. The channel is buffered and can be programmed

for one of eight input ranges from ± 20 mV to ± 2.56 V. The input

channels can be configured for either fully differential inputs or

pseudo-differential input channels via the CH2, CH1, and CH0

bits in the Configuration Register. Buffering the input channel

allows the part to handle significant source impedances on the

analog input, allowing R/C filtering (for noise rejection or RFI

reduction) to be placed on the analog inputs if required. These

input channels are intended for converting signals directly from

sensors without the need for external signal conditioning. Other

functions contained on-chip that augment the operation of the

ADC include software configurable current sources, switchable

reference inputs, and low-side power switches.

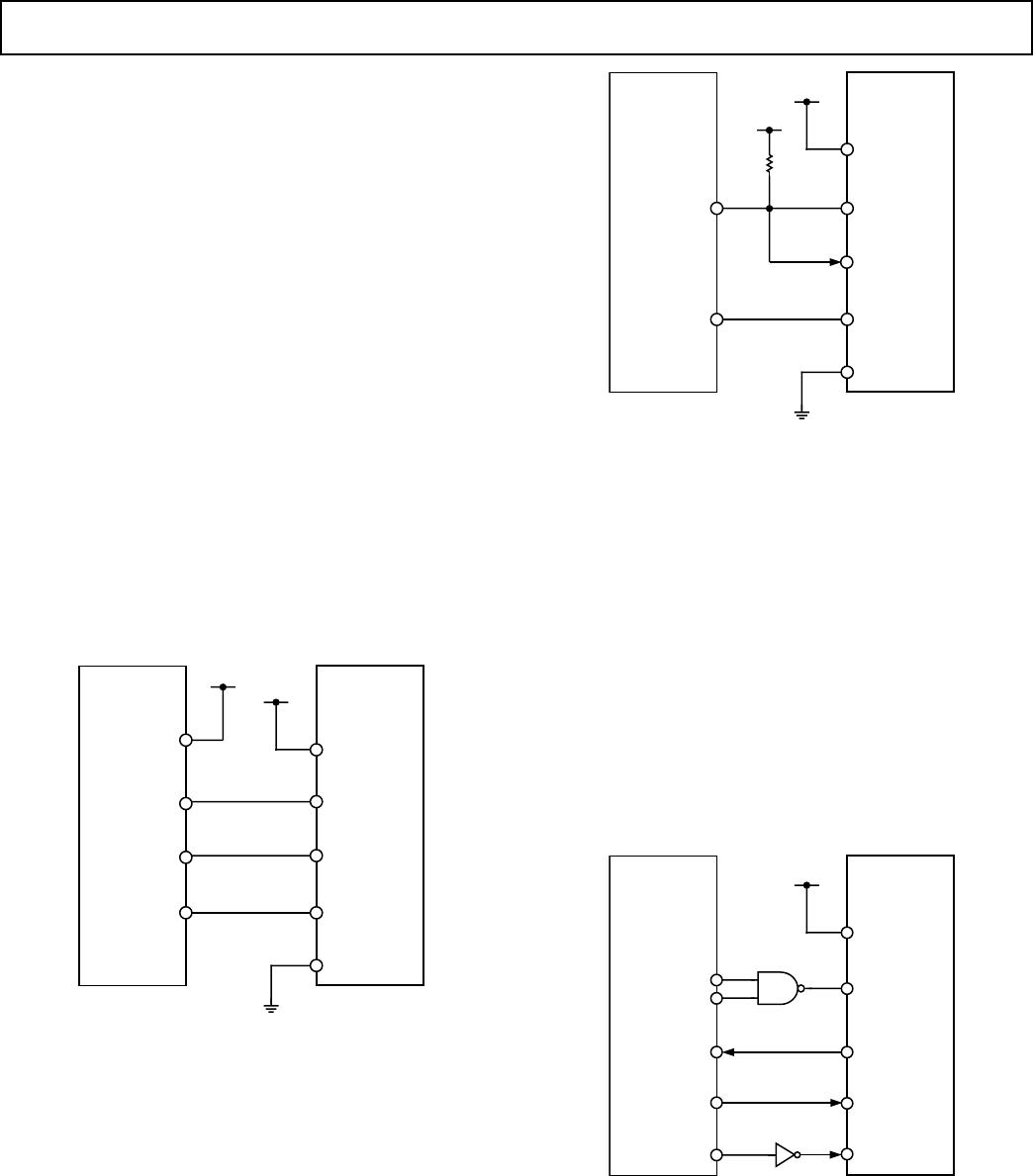

The basic connection diagram for the AD7709 is shown in

Figure 14. An AD780/REF195, precision 2.5 V reference, provides

the reference source for the part. A quartz crystal or ceramic

resonator provides the 32.768 kHz master clock source for the

part. In some cases, it will be necessary to connect capacitors on

the crystal or resonator to ensure that it does not oscillate at over-

tones

of its fundamental operating frequency. The values of

capacitors will vary depending on manufacturer specifications.

Analog Input Channels

The main ADC has five associated analog input pins (labeled

AIN1 to AIN4 and AINCOM) that can be configured as two

fully differential input channels (AIN1–AIN2 and AIN3–AIN4)

or four pseudo-differential input channels (AIN1–AINCOM,

AIN2–AINCOM, AIN3–AINCOM, and AIN4–AINCOM).

Channel selection bits CH2, CHI, and CH0 in the Configuration

Register detail the different configurations. When the analog

input

channel is switched, the settling time of the part must elapse

before a new valid word is available from the ADC.

IOUT1

AIN3/P3

AINCOM

AIN1

IOUT2

AIN4/P4

REFIN1(–)

AIN2

REFIN1(+)

REFIN2(–)

REFIN2(+)

RESET

CS

DOUT

DIN

SCLK

P2/SW2

P1/SW1

XTAL1

XTAL2

5V

CHIP

SELECT

RECEIVE

(READ)

SERIAL

CLOCK

32.768kHz

CRYSTAL

PWRGND

GND

AD780/

REF195

V

IN

V

OUT

GND

V

DD

ANALOG 5V

SUPPLY

0.1F

10F

0.1F

10F

ANALOG 5V

SUPPLY

AD7709

SERIAL DATA

(WRITE)

Figure 14. Basic Connection Diagram

The output of the ADC multiplexer feeds into a high impedance

input stage of the buffer amplifier. As a result, the ADC inputs can

handle significant source impedances and are tailored for direct

connection to external resistive-type sensors like strain gauges or

Resistance Temperature Detectors (RTDs).

The absolute input voltage range on the ADC inputs when buff-

ered (AIN1 to AIN4) is restricted to a range between GND +

100 mV and V

DD

– 100 mV. Care must be taken in setting up

the common-mode voltage and input voltage range so that these

limits are not exceeded; otherwise, there will be a degradation in

linearity and noise performance.

The absolute input voltage range on the ADC inputs when

unbuffered (AINCOM) includes the range between GND – 30 mV

to

V

DD

+ 30 mV as a result of being unbuffered. The negative abso-

lute input voltage limit does allow the possibility of monitoring

small true bipolar signals with respect to GND.