NCS2001, NCV2001

www.onsemi.com

10

APPLICATION INFORMATION AND OPERATING DESCRIPTION

GENERAL INFORMATION

The NCS2001 is an industry first rail−to−rail input,

rail−to−rail output amplifier that features guaranteed

sub−one voltage operation. This unique feature set is

achieved with the use of a modified analog CMOS process

that allows the implementation of depletion MOSFET

devices. The amplifier has a 1.0 MHz gain bandwidth

product, 2.2 V/ms slew rate and is operational over a power

supply range less than 0.9 V to as high as 7.0 V.

Inputs

The input topology chosen for this device series is

unconventional when compared to most low voltage

operational amplifiers. It consists of an N−Channel

depletion mode differential transistor pair that drives a

folded cascade stage and current mirror. This configuration

extends the input common mode voltage range to

encompass the V

EE

and V

CC

power supply rails, even when

powered from a combined total of less than 0.9 V. Figures 27

and 28 show the input common mode voltage range versus

power supply voltage.

The differential input stage is laser trimmed in order to

minimize offset voltage. The N−Channel depletion mode

MOSFET input stage exhibits an extremely low input bias

current of less than 10 pA. The input bias current versus

temperature is shown in Figure 4. Either one or both inputs

can be biased as low as V

EE

minus 300 mV to as high as

7.0 V without causing damage to the device. If the input

common mode voltage range is exceeded, the output will not

display a phase reversal. If the maximum input positive or

negative voltage ratings are to be exceeded, a series resistor

must be used to limit the input current to less than 2.0 mA.

The ultra low input bias current of the NCS2001 allows

the use of extremely high value source and feedback resistor

without reducing the amplifier’s gain accuracy. These high

value resistors, in conjunction with the device input and

printed circuit board parasitic capacitances C

in

, will add an

additional pole to the single pole amplifier in Figure 30. If

low enough in frequency, this additional pole can reduce the

phase margin and significantly increase the output settling

time. The effects of C

in

, can be canceled by placing a zero

into the feedback loop. This is accomplished with the

addition of capacitor C

fb

. An approximate value for C

fb

can

be calculated by:

C

fb

+

R

in

C

in

R

fb

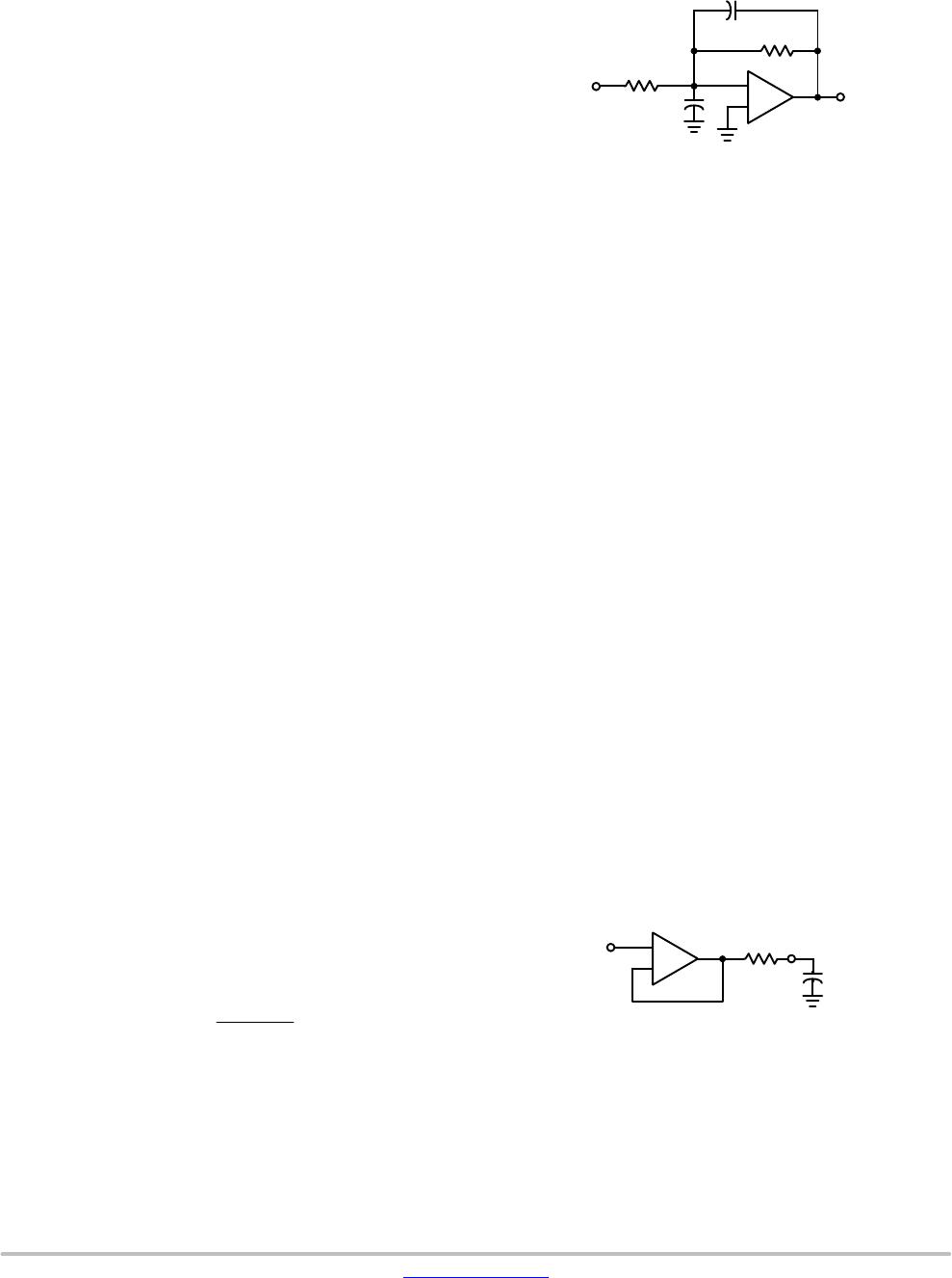

Figure 30. Input Capacitance Pole Cancellation

+

-

Output

R

fb

C

in

R

in

C

fb

C

in

= Input and printed circuit board capacitance

Input

Output

The output stage consists of complementary P and

N−Channel devices connected to provide rail−to−rail output

drive. With a 2.0 k load, the output can swing within 50 mV

of either rail. It is also capable of supplying over 75 mA

when powered from 5.0 V and 1.0 mA when powered from

0.9 V.

When connected as a unity gain follower, the NCS2001 can

directly drive capacitive loads in excess of 820 pF at room

temperature without oscillating but with significantly

reduced phase margin. The unity gain follower configuration

exhibits the highest bandwidth and is most prone to

oscillations when driving a high value capacitive load. The

capacitive load in combination with the amplifier’s output

impedance, creates a phase lag that can result in an

under−damped pulse response or a continuous oscillation.

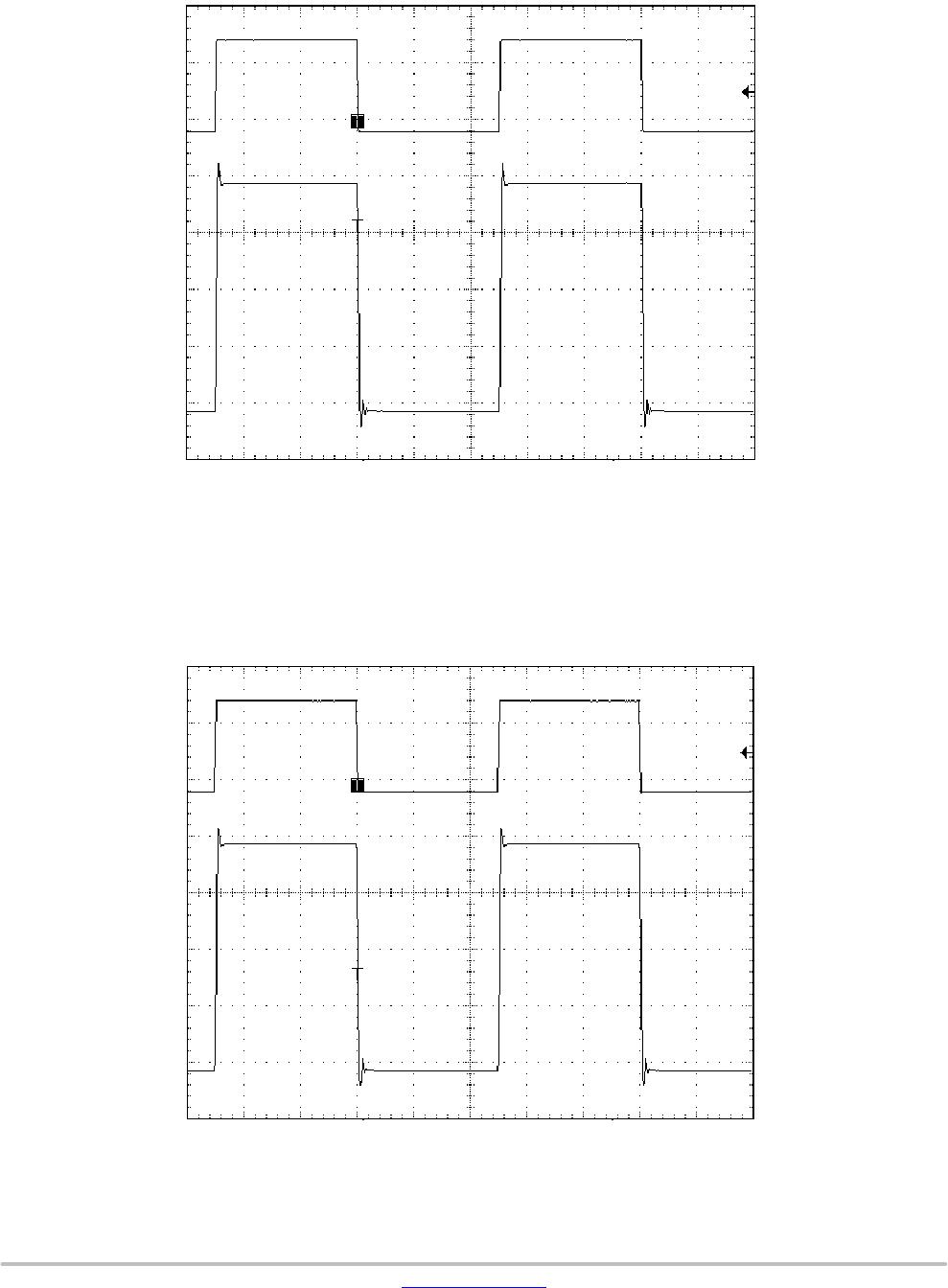

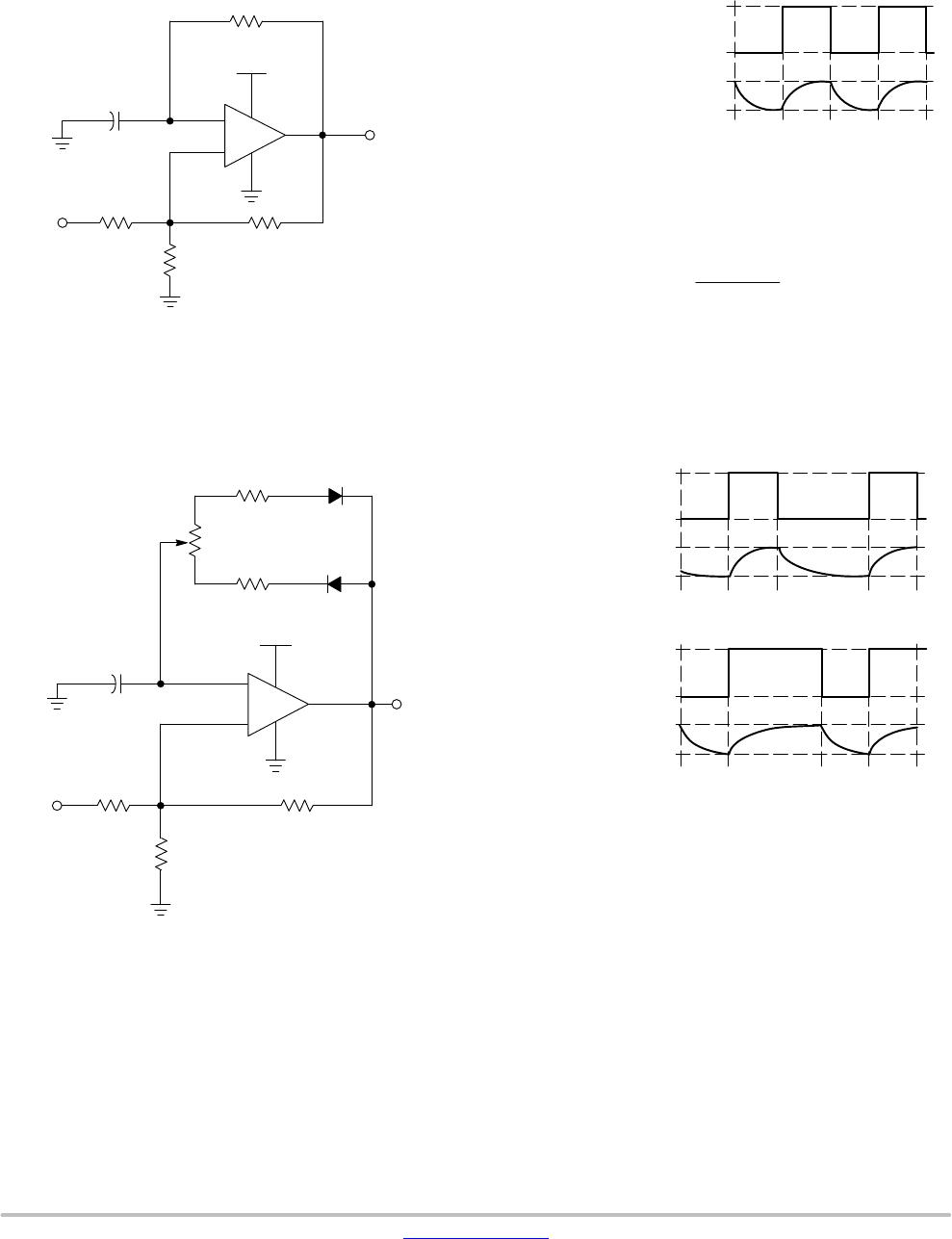

Figure 32 shows the effect of driving a large capacitive load

in a voltage follower type of setup. When driving capacitive

loads exceeding 820 pF, it is recommended to place a low

value isolation resistor between the output of the op amp and

the load, as shown in Figure 31. The series resistor isolates the

capacitive load from the output and enhances the phase

margin. Refer to Figure 33. Larger values of R will result in

a cleaner output waveform but excessively large values will

degrade the large signal rise and fall time and reduce the

output amplitude. Depending upon the capacitor

characteristics, the isolation resistor value will typically be

between 50 to 500 W. The output drive capability for resistive

and capacitive loads is shown in Figures 2, 3, and 23.

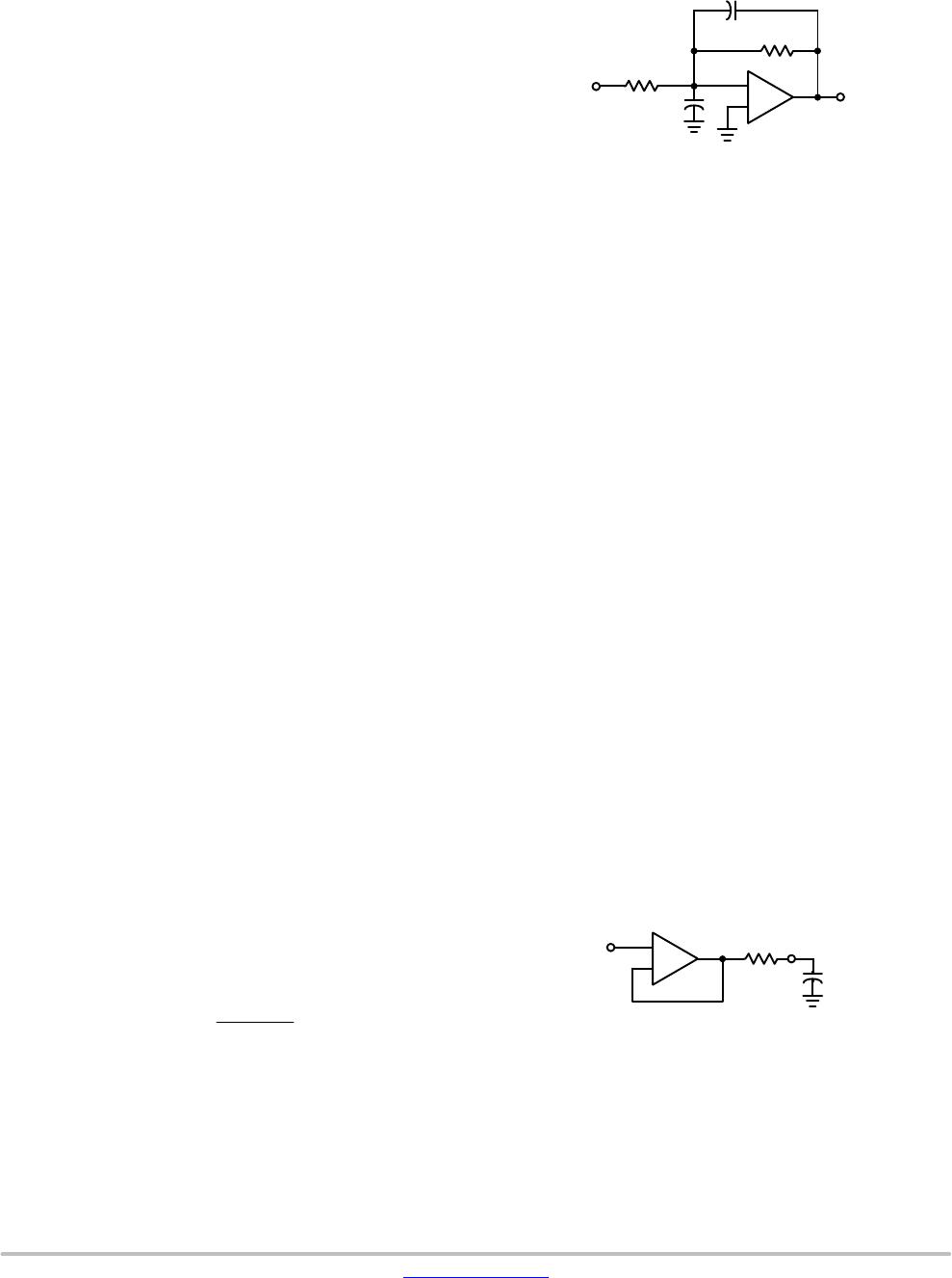

Figure 31. Capacitance Load Isolation

+

-

Output

R

Isolation resistor R = 50 to 500

C

L

Input

Note that the lowest phase margin is observed at cold

temperature and low supply voltage.