IDT8T49N008ANLGI REVISION A FEBRUARY 13, 2014 13 ©2014 Integrated Device Technology, Inc.

IDT8T49N008I Data Sheet PROGRAMMABLE FEMTOCLOCK

®

NG LVPECL/LVDS CLOCK GENERATOR WITH 8-OUTPUTS

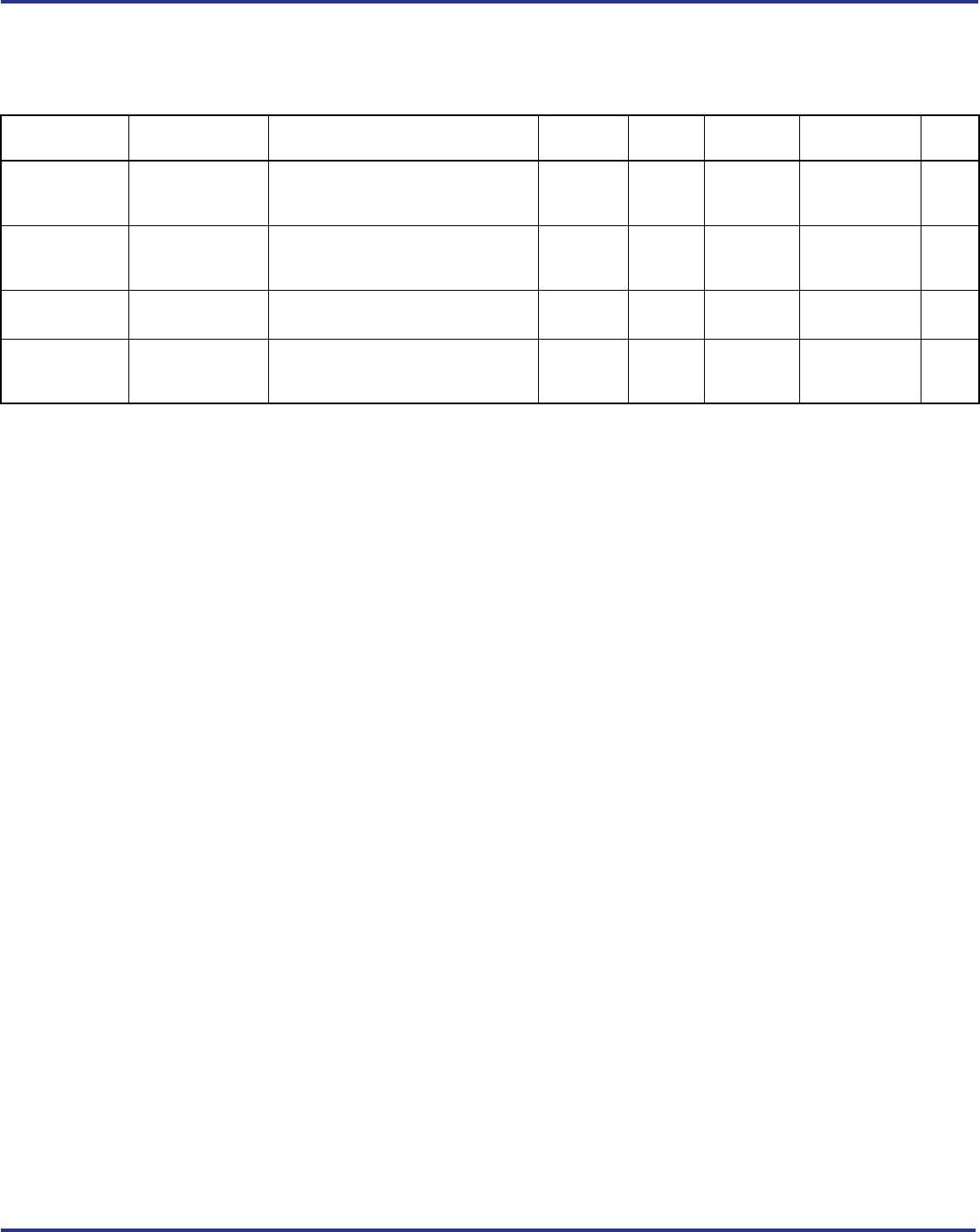

AC Electrical Characteristics

Table 6A. PCI Express Jitter Specifications, V

CC

= V

CCO

= 3.3V ± 5% or 2.5V ± 5%, V

EE

= 0V, T

A

= -40°C to 85°C

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is

mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium

has been reached under these conditions. For additional information, refer to the PCI Express Application Note section in the datasheet.

NOTE 1: Peak-to-Peak jitter after applying system transfer function for the Common Clock Architecture. Maximum limit for PCI Express Gen 1

is 86ps peak-to-peak for a sample size of 10

6

clock periods.

NOTE 2: RMS jitter after applying the two evaluation bands to the two transfer functions defined in the Common Clock Architecture and

reporting the worst case results for each evaluation band. Maximum limit for PCI Express Generation 2 is 3.1ps RMS for t

REFCLK_HF_RMS

(High Band) and 3.0ps RMS for t

REFCLK_LF_RMS

(Low Band).

NOTE 3: RMS jitter after applying system transfer function for the common clock architecture. This specification is based on the PCI Express

Base Specification Revision 0.7, October 2009 and is subject to change pending the final release version of the specification.

NOTE 4: This parameter is guaranteed by characterization. Not tested in production.

Symbol Parameter Test Conditions Minimum Typical Maximum

PCIe Industry

Specification Units

t

j

(PCIe Gen 1)

Phase Jitter

Peak-to-Peak;

NOTE 1, 4

ƒ = 100MHz, 25MHz Crystal Input

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

8.3 13.2 86 ps

t

REFCLK_HF_RMS

(PCIe Gen 2)

Phase Jitter RMS;

NOTE 2, 4

ƒ = 100MHz, 25MHz Crystal Input

High Band: 1.5MHz - Nyquist

(clock frequency/2)

0.78 1.35 3.1 ps

t

REFCLK_LF_RMS

(PCIe Gen 2)

Phase Jitter RMS;

NOTE 2, 4

ƒ = 100MHz, 25MHz Crystal Input

Low Band: 10kHz - 1.5MHz

0.05 0.10 3.0 ps

t

REFCLK_RMS

(PCIe Gen 3)

Phase Jitter RMS;

NOTE 3, 4

ƒ = 100MHz, 25MHz Crystal Input

Evaluation Band: 0Hz - Nyquist

(clock frequency/2)

0.175 0.34 0.8 ps