Chapter 1: Overview for the Arria II Device Family 1–3

Arria II Device Feature

July 2012 Altera Corporation Arria II Device Handbook Volume 1: Device Interfaces and Integration

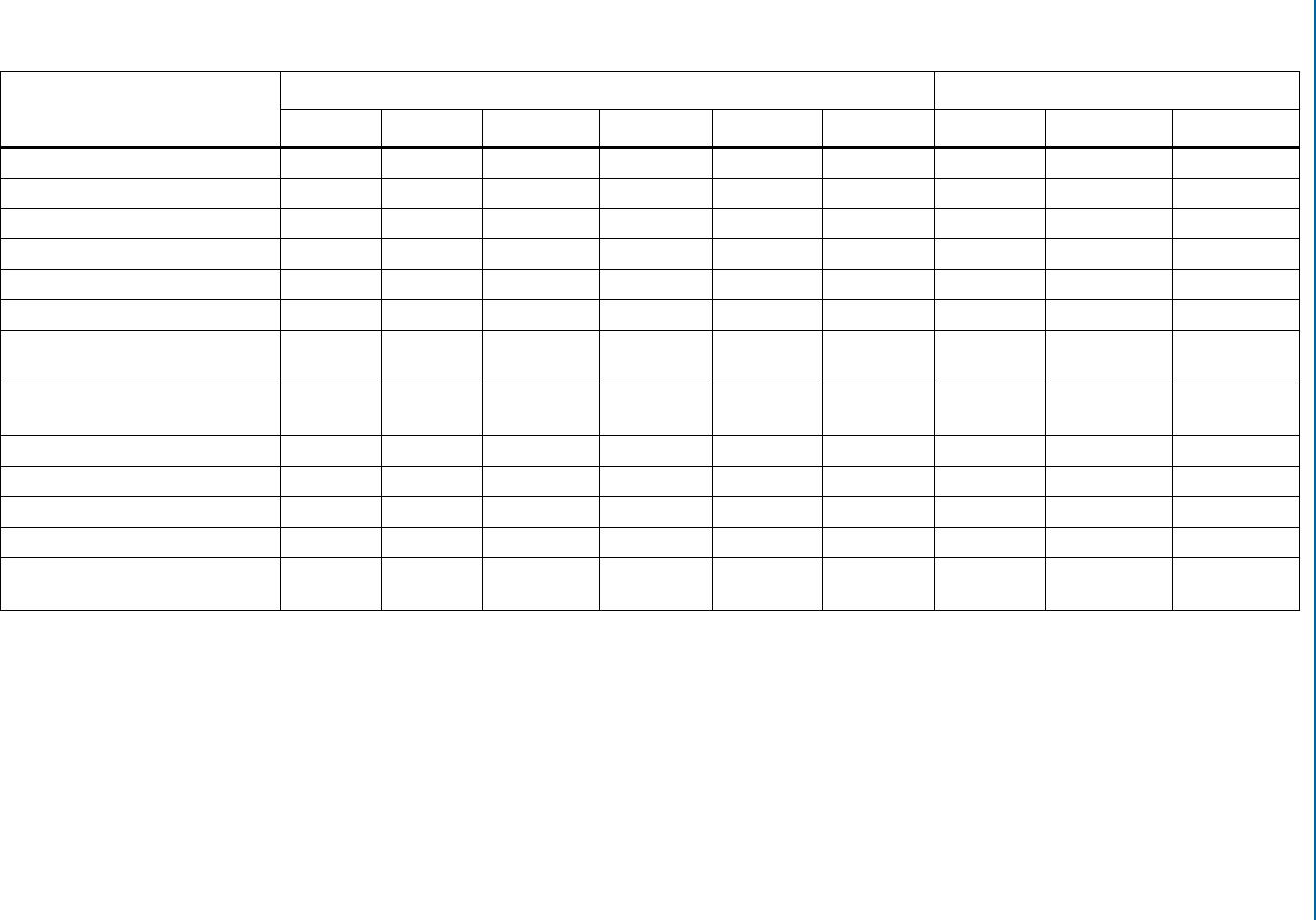

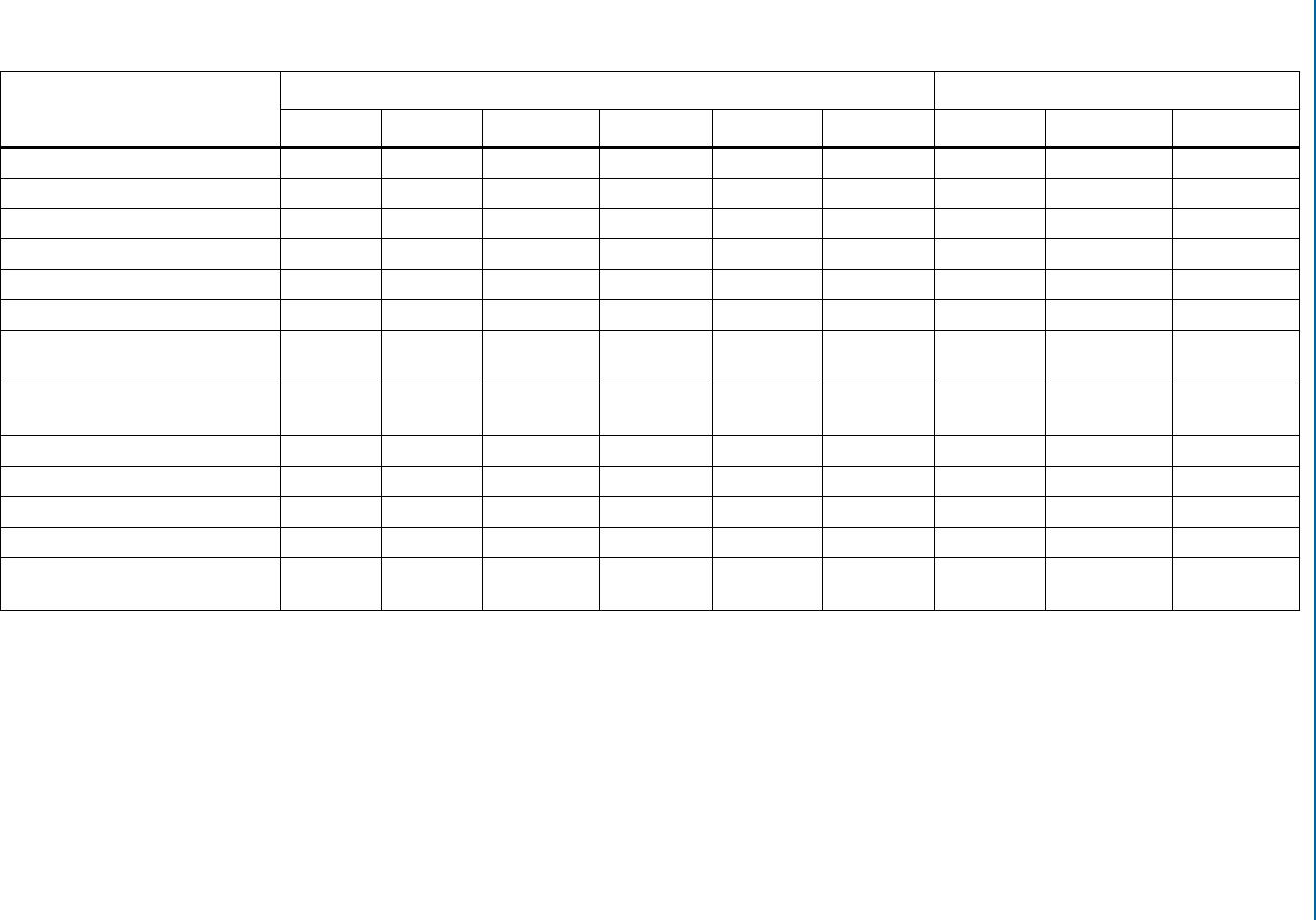

Table 1–1 lists the Arria II device features.

Table 1–1. Features in Arria II Devices

Feature

Arria II GX Devices Arria II GZ Devices

EP2AGX45 EP2AGX65 EP2AGX95 EP2AGX125 EP2AGX190 EP2AGX260 EP2AGZ225 EP2AGZ300 EP2AGZ350

Total Transceivers (1) 8 8 12 12 16 16 16 or 24 16 or 24 16 or 24

ALMs 18,050 25,300 37,470 49,640 76,120 102,600 89,600 119,200 139,400

LEs 42,959 60,214 89,178 118,143 181,165 244,188 224,000 298,000 348,500

PCIe hard IP blocks 1 1 1 1 1 1 1 1 1

M9K Blocks 319 495 612 730 840 950 1,235 1,248 1,248

M144K Blocks — — — — — — — 24 36

Total Embedded Memory in M9K

Blocks (Kbits)

2,871 4,455 5,508 6,570 7,560 8,550 11,115 14,688 16,416

Total On-Chip Memory

(M9K +M144K + MLABs) (Kbits)

3,435 5,246 6,679 8,121 9,939 11,756 13,915 18,413 20,772

Embedded Multipliers (18 x 18) (2) 232 312 448 576 656 736 800 920 1,040

General Purpose PLLs 4 4 6 6 6 6 6 or 8 4, 6, or 8 4, 6, or 8

Transceiver TX PLLs (3), (4) 2 or 4 2 or 4 4 or 6 4 or 6 6 or 8 6 or 8 8 or 12 8 or 12 8 or 12

User I/O Banks (5), (6) 6 6 8 8 12 12 16 or 20 8, 16, or 20 8, 16, or 20

High-Speed LVDS SERDES

(up to 1.25 Gbps) (7)

8, 24, or 28 8, 24, or 28 24, 28, or 32 24, 28, 32 28 or 48 24 or 48 42 or 86 0 (8), 42, or 86 0 (8), 42, or 86

Notes to Table 1–1:

(1) The total number of transceivers is divided equally between the left and right side of each device, except for the devices in the F780 package. These devices have eight transceiver channels located only on

the right side of the device.

(2) This is in four multiplier adder mode.

(3) The FPGA fabric can use these phase locked-loops (PLLs) if they are not used by the transceiver.

(4) The number of PLLs depends on the package. Transceiver transmitter (TX) PLL count = (number of transceiver blocks)

× 2.

(5) Banks 3C and 8C are dedicated configuration banks and do not have user I/O pins.

(6) For Arria II GZ devices, the user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins

are not included in the pin count.

(7) For Arria II GZ devices, total pairs of high-speed LVDS SERDES take the lowest channel count of RX/TX. For more information, refer to the High-Speed I/O Interfaces and DPA in Arria II Devices chapter.

(8) The smallest pin package (780-pin package) does not support high-speed LVDS SERDES.