Chapter 1: Overview for the Arria II Device Family 1–11

Arria II Device Architecture

July 2012 Altera Corporation Arria II Device Handbook Volume 1: Device Interfaces and Integration

■ Arria II GX devices have dedicated configuration banks at Bank 3C and 8C, which

support dedicated configuration pins and some of the dual-purpose pins with a

configuration scheme at 1.8, 2.5, 3.0, and 3.3 V. For Arria II GZ devices, the

dedicated configuration pins are located in Bank 1A and Bank 1C. However, these

banks are not dedicated configuration banks; therefore, user I/O pins are available

in Bank 1A and Bank 1C.

■ Dedicated

VCCIO

,

VREF

, and

VCCPD

pin per I/O bank to allow voltage-referenced

I/O standards. Each I/O bank can operate at independent V

CCIO

, V

REF

, and V

CCPD

levels.

High-Speed LVDS I/O and DPA

■ Dedicated circuitry for implementing LVDS interfaces at speeds from 150 Mbps to

1.25 Gbps

■ R

D

OCT for high-speed LVDS interfacing

■ DPA circuitry and soft-CDR circuitry at the receiver automatically compensates for

channel-to-channel and channel-to-clock skew in source-synchronous interfaces

and allows for implementation of asynchronous serial interfaces with embedded

clocks at up to 1.25 Gbps data rate (SGMII and GbE)

■ Emulated LVDS output buffers use two single-ended output buffers with an

external resistor network to support LVDS, mini-LVDS, BLVDS (only for

Arria II GZ devices), and RSDS standards.

Clock Management

■ Provides dedicated global clock networks, regional clock networks, and periphery

clock networks that are organized into a hierarchical structure that provides up to

192 unique clock domains

■ Up to eight PLLs with 10 outputs per PLL to provide robust clock management

and synthesis

■ Independently programmable PLL outputs, creating a unique and

customizable clock frequency with no fixed relation to any other clock

■ Inherent jitter filtration and fine granularity control over multiply and divide

ratios

■ Supports spread-spectrum input clocking and counter cascading with PLL

input clock frequencies ranging from 5 to 500 MHz to support both low-cost

and high-end clock performance

■ FPGA fabric can use the unused transceiver PLLs to provide more flexibility

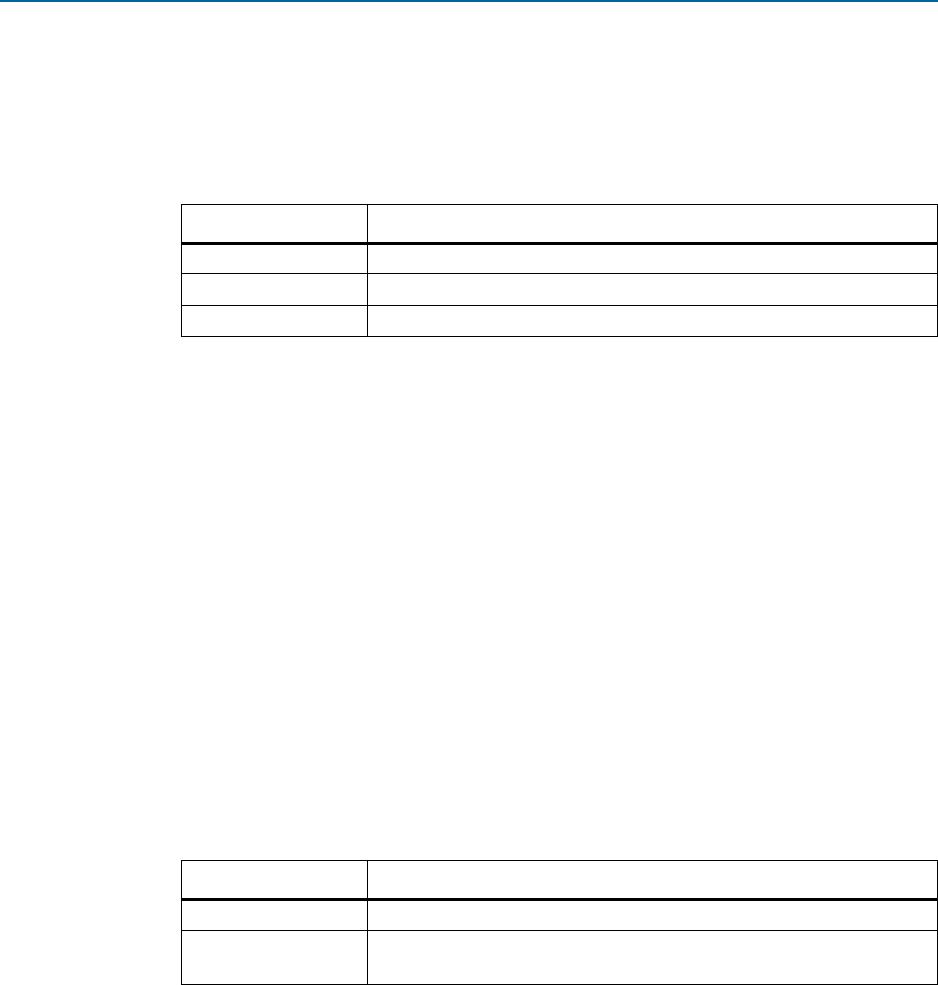

Table 1–9. Location of OCT Calibration Block in Arria II Devices

Device Package Option I/O Bank

Arria II GX All pin packages Bank 3A, Bank 7A, and Bank 8A

Arria II GZ

780-pin flip chip FBGA Bank 3A, Bank 4A, Bank 7A, and Bank 8A

1152-pin flip chip FBGA Bank 1A, Bank 3A, Bank 4A, Bank 6A, Bank 7A, and Bank 8A

1517-pin flip chip FBGA Bank 1A, Bank 2A, Bank 3A, Bank 4A, Bank 5A, Bank 6A, Bank 7A, and Bank 8A