X9317

2

FN8183.9

November 4, 2014

Submit Document Feedback

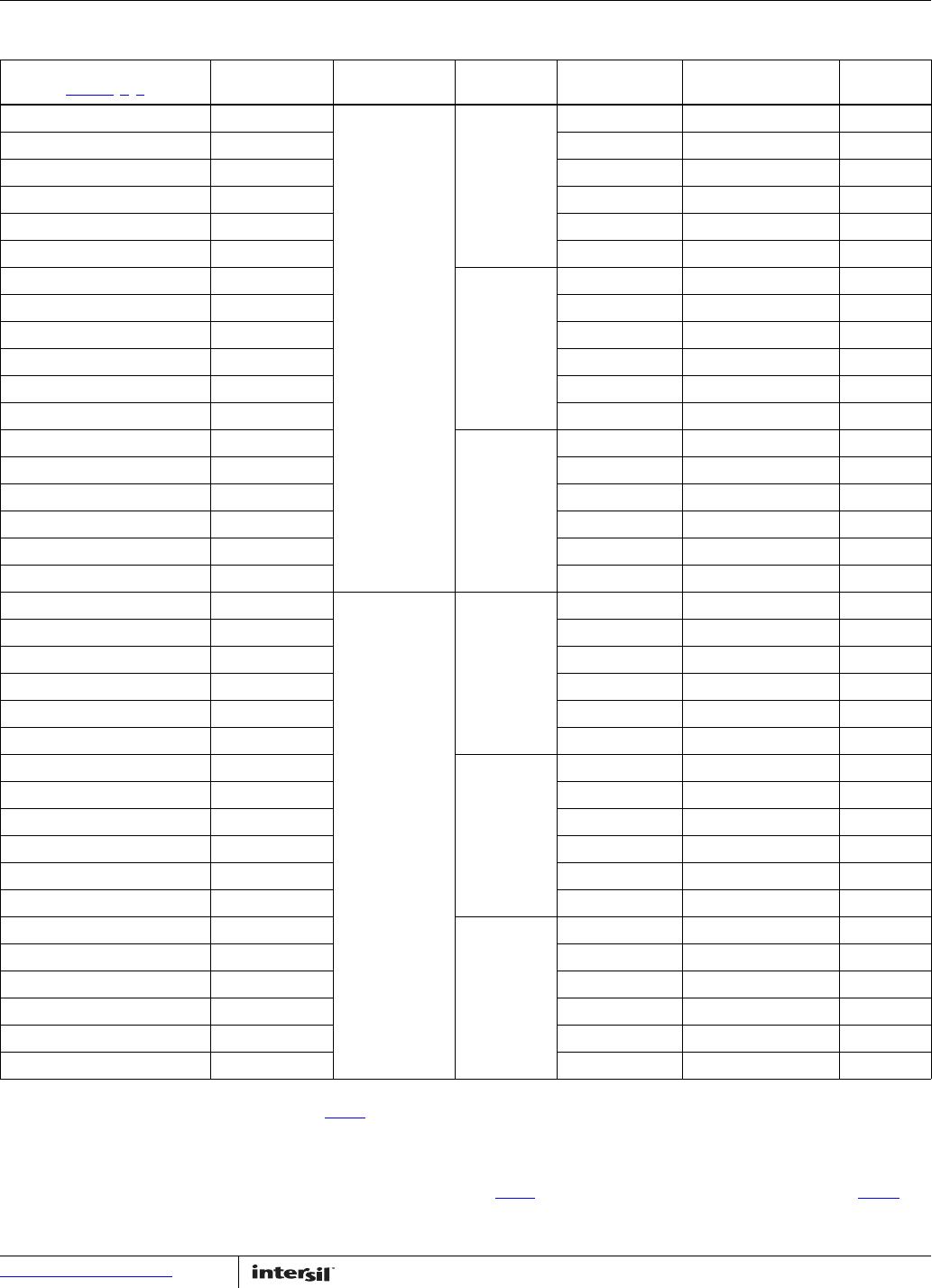

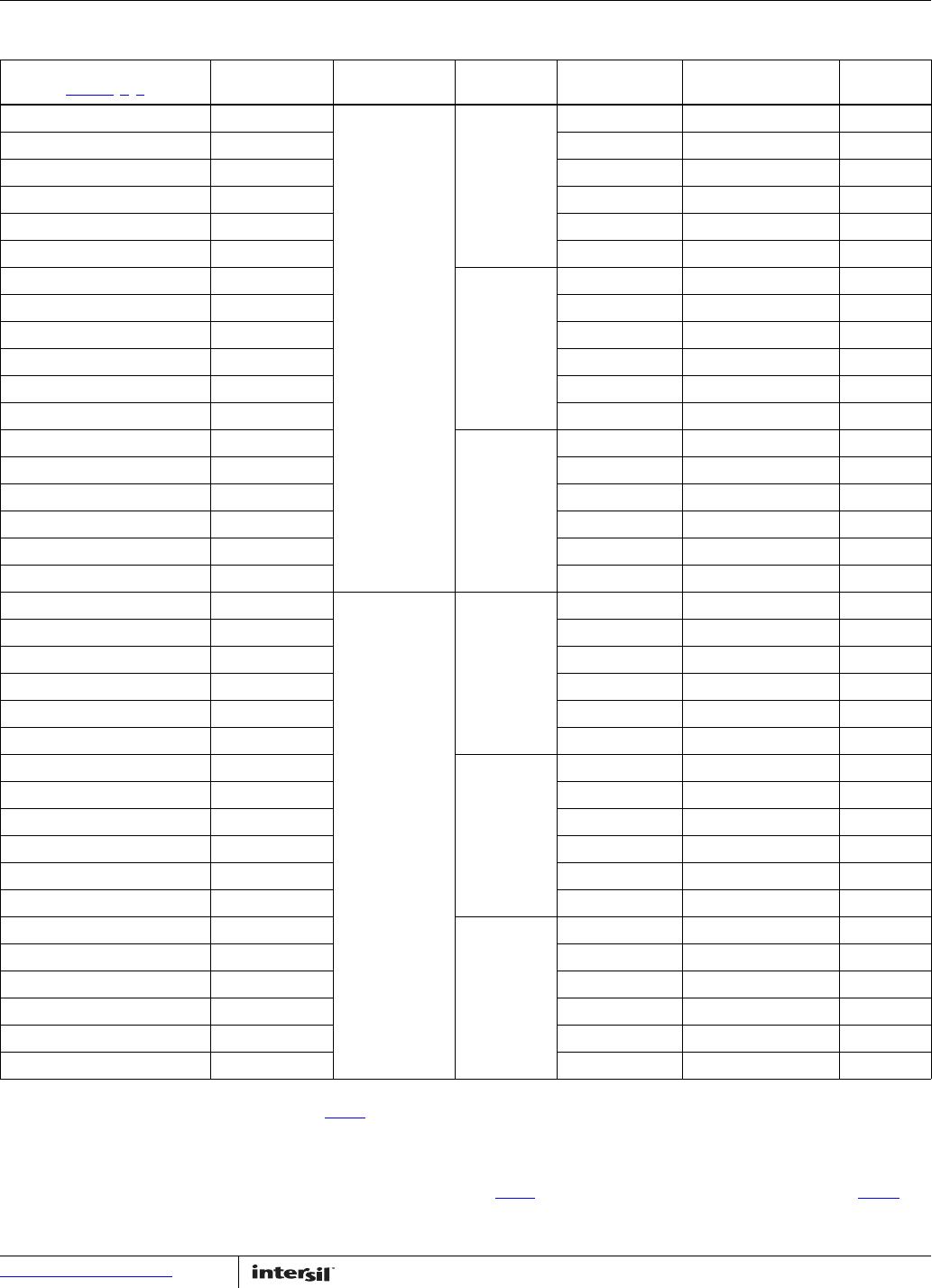

Ordering Information

PART NUMBER

(Notes 1

, 2, 3)PART MARKING

V

CC

LIMITS

(V)

R

TOTAL

(kΩ)

TEMPERATURE

RANGE (°C)

PACKAGE

(Pb-Free)

PKG.

DWG. #

X9317WM8Z DCW 5 ±10% 10 0 to +70 8 Ld MSOP M8.118

X9317WM8IZ DCT -40 to +85 8 Ld MSOP M8.118

X9317WS8Z X9317W Z 0 to +70 8 Ld SOIC M8.15E

X9317WS8IZ X9317W ZI -40 to +85 8 Ld SOIC M8.15E

X9317WV8Z 9317W Z 0 to +70 8 Ld TSSOP M8.173

X9317WV8IZ 9317W IZ -40 to +85 8 Ld TSSOP M8.173

X9317UM8Z DCS 50 0 to +70 8 Ld MSOP M8.118

X9317UM8IZ DCR -40 to +85 8 Ld MSOP M8.118

X9317US8Z X9317U Z 0 to +70 8 Ld SOIC M8.15E

X9317US8IZ X9317U ZI -40 to +85 8 Ld SOIC M8.15E

X9317UV8Z 9317U Z 0 to +70 8 Ld TSSOP M8.173

X9317UV8IZ 9317U IZ -40 to +85 8 Ld TSSOP M8.173

X9317TM8Z DCN 100 0 to +70 8 Ld MSOP M8.118

X9317TM8IZ DCL -40 to +85 8 Ld MSOP M8.118

X9317TS8Z X9317T Z 0 to +70 8 Ld SOIC M8.15E

X9317TS8IZ X9317T ZI -40 to +85 8 Ld SOIC M8.15E

X9317TV8Z 9317T Z 0 to +70 8 Ld TSSOP M8.173

X9317TV8IZ 9317T IZ -40 to +85 8 Ld TSSOP M8.173

X9317WM8Z-2.7 DCX 2.7 to 5.5 10 0 to +70 8 Ld MSOP M8.118

X9317WM8IZ-2.7 DCU -40 to +85 8 Ld MSOP M8.118

X9317WS8Z-2.7 X9317W ZF 0 to +70 8 Ld SOIC M8.15E

X9317WS8IZ-2.7

X9317W ZG -40 to +85 8 Ld SOIC M8.15E

X9317WV8Z-2.7

9317W FZ 0 to +70 8 Ld TSSOP M8.173

X9317WV8IZ-2.7 AKZ -40 to +85 8 Ld TSSOP M8.173

X9317UM8Z-2.7 AOB 50 0 to +70 8 Ld MSOP M8.118

X9317UM8IZ-2.7 AOH -40 to +85 8 Ld MSOP M8.118

X9317US8Z-2.7 X9317U ZF 0 to +70 8 Ld SOIC M8.15E

X9317US8IZ-2.7 X9317U ZG -40 to +85 8 Ld SOIC M8.15E

X9317UV8Z-2.7 9317U FZ 0 to +70 8 Ld TSSOP M8.173

X9317UV8IZ-2.7 9317U GZ -40 to +85 8 Ld TSSOP M8.173

X9317TM8Z-2.7 DCP 100 0 to +70 8 Ld MSOP M8.118

X9317TM8IZ-2.7 DCM -40 to +85 8 Ld MSOP M8.118

X9317TS8Z-2.7 X9317T ZF 0 to +70 8 Ld SOIC M8.15E

X9317TS8IZ-2.7 X9317T ZG -40 to +85 8 Ld SOIC M8.15E

X9317TV8Z-2.7 9317T FZ 0 to +70 8 Ld TSSOP M8.173

X9317TV8IZ-2.7 9317T GZ -40 to +85 8 Ld TSSOP M8.173

NOTES:

1. Add “T1” suffix for tape and reel. Please refer to TB347

for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte

tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-

free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC JSTD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for X9317

. For more information on MSL please see tech brief TB363.