AD8344

Rev. 0 | Page 14 of 20

AC INTERFACES

The AD8344 is a high-side downconverter. It is designed to

downconvert radio frequencies (RF) to lower intermediate

frequencies (IF) using a high-side local oscillator (LO). The LO

is injected into the mixer core at a frequency greater than the

desired input RF frequency. The difference between the LO and

RF frequencies, f

LO

− f

RF,

is the IF frequency, f

IF

. In addition to

the desired RF signal, an RF image will be downconverted to the

same IF frequency. The image frequency is at f

LO

+ f

IF

. The con-

version gain of the AD8344 decreases with increasing input

frequency. By choosing to use a high-side LO the image fre-

quency at f

LO

+ f

IF

is translated with less conversion gain than

the desired RF signal at f

LO

− f

IF

. Additionally, any wideband

noise present at the image frequency will be downconverted

with less conversion gain than would be the case if a low-side

LO was applied. In general, a high-side LO should be used with

the AD8344 to ensure optimal noise performance and image

rejection.

The AD8344 is designed to operate using RF frequencies in the

400 MHz to 1200 MHz frequency range, with high-side LO

injection within the 470 MHz to 1600 MHz range. It is essential

to ac-couple RF and LO ports to prevent dc offsets from skew-

ing the mixer core in an asymmetrical manner, potentially

degrading linear input swing and impacting distortion and

input compression characteristics.

The AD8344 RFIN port presents a 50 Ω impedance relative to

RFCM. In order to ensure a good impedance match, the RFIN

ac-coupling capacitor should be large enough in value so that

the presented reactance is negligible at the intended RF fre-

quency. Additionally, the RFCM bypassing capacitor should be

sufficiently large to provide a low impedance return path to

board ground. Low inductance ceramic grade capacitors of no

more than 330 pF are sufficient for most applications.

Similarly the LOIN port provides a 50 Ω load impedance with

common-mode decoupling on LOCM. Again, common grade

ceramic capacitors will provide sufficient signal coupling and

bypassing of the LO interface.

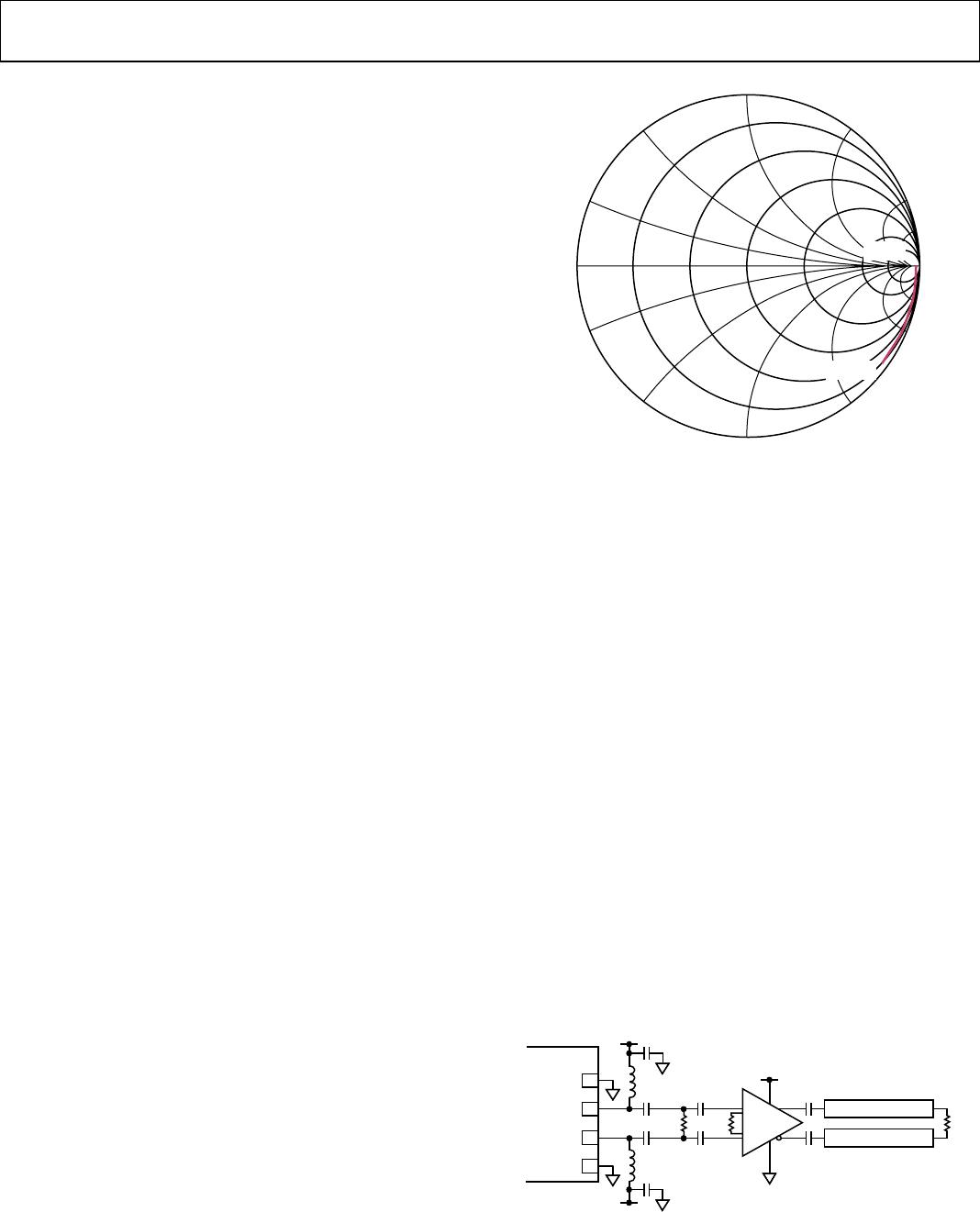

04826-0-040

0180

30

330

10MHz

500MHz

60

90

270

300

120

240

150

210

Figure 37. IF Port Reflection Coefficient from 10 MHz to 500 MHz

IF PORT

The IF port uses an open collector differential output interface.

The NPN open collectors can be modeled as high impedance

current sources. The stray capacitance associated with the IC

package presents a slightly capacitive source impedance as in

Figure 37. In general, the IFOP and IFOM output ports can be

modeled as current sources with an impedance of ~10 kΩ in

parallel with ~1 pF of shunt capacitance. Circuit board traces

connecting the IF outputs to the load should be narrow and

short to prevent excessive capacitive loading. In order to main-

tain the specified conversion gain of the mixer, the IF output

ports should be loaded into 200 Ω. It is not necessary to attempt

to provide a conjugate match to the IF port output source

impedance. If the IF signal needs to be delivered to a remote

load, more than a few centimeters away, it may be necessary to

use an appropriate buffer amplifier to present a real 200 Ω load-

ing impedance at the IF output interface. The buffer amplifier

should have the appropriate source impedance to match the

characteristic impedance of the selected transmission line. An

example is provided in Figure 38, where the AD8351 differential

amplifier is used to drive a pair of 75 Ω transmission lines. The

gain of the buffer can be independently set by choosing an

appropriate gain resistor, R

G

.

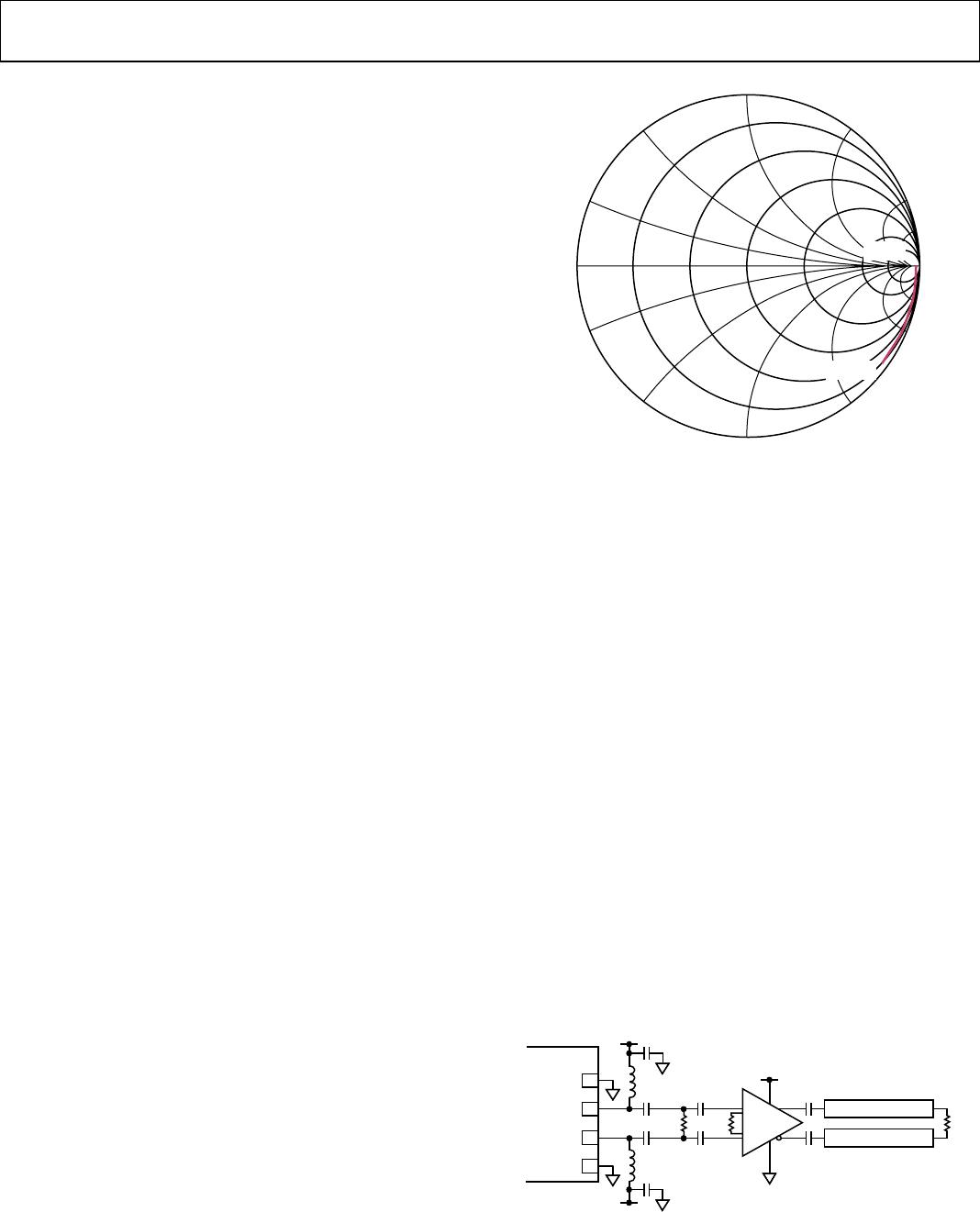

04826-0-041

COMM

8

IFOP

7

IFOM

6

COMM

5

AD8344

AD8351

+

–

R

F

C

+

V

S

R

F

C

Z

L

=

2

0

0

Ω

+

V

S

+

V

S

200Ω R

G

Z

L

Tx LINE Z

O

= 75Ω

Tx LINE Z

O

= 75Ω

Figure 38. AD8351 Used as Transmission Line Driver and Impedance Buffer