KS8721CL Micrel, Inc.

M9999-041405 4 April 2005

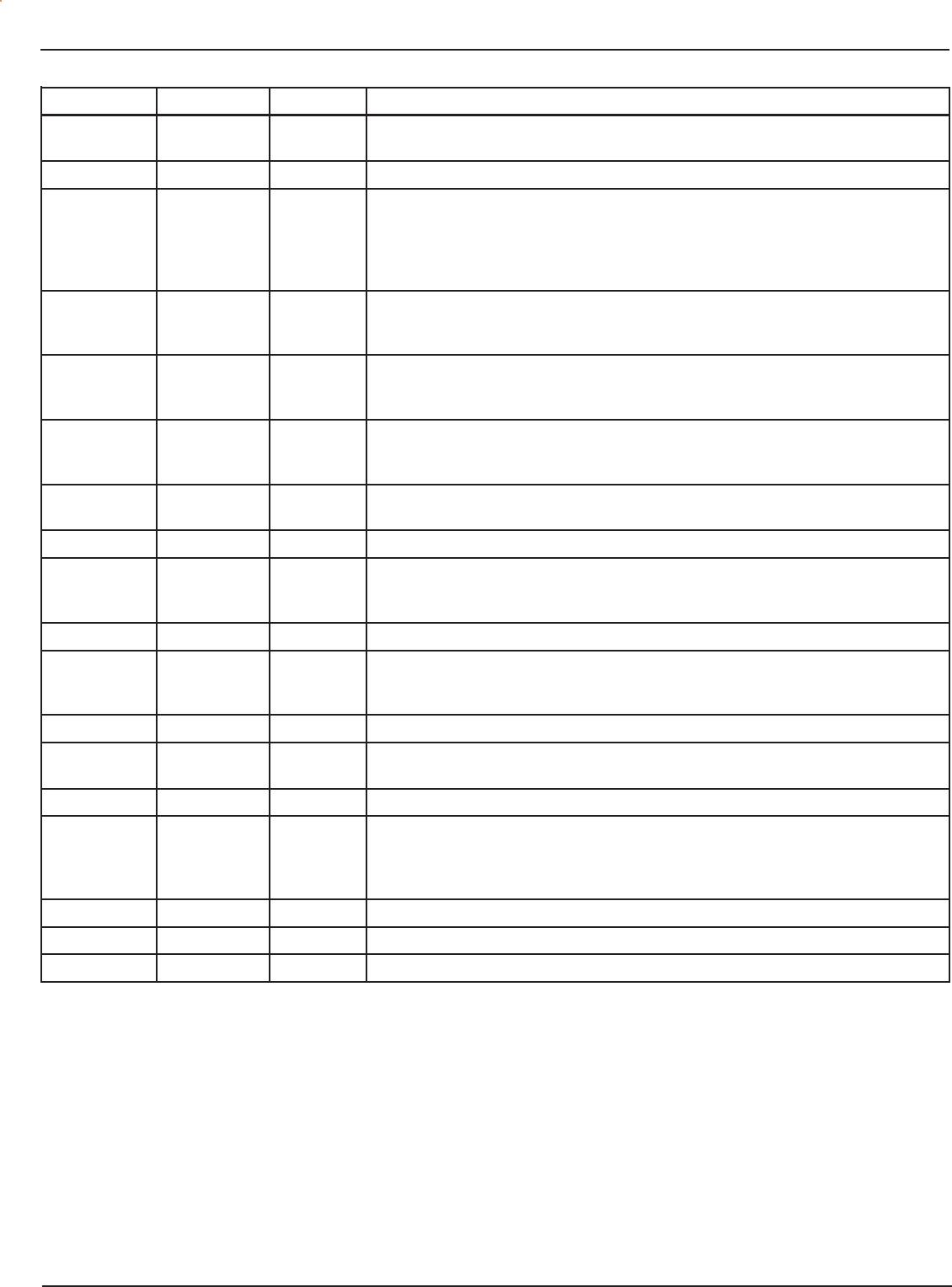

Table Of Contents

Pin Description ............................................................................................................................................................ 6

Strapping Option ......................................................................................................................................................... 9

Pin Configuration ...................................................................................................................................................... 10

Introduction ........................................................................................................................................................... 11

100BASE-TX Transmit ........................................................................................................................................ 11

100BASE-TX Receive ......................................................................................................................................... 11

PLL Clock Synthesizer......................................................................................................................................... 11

Scrambler/De-scrambler (100BASE-TX only) ..................................................................................................... 11

10BASE-T Transmit ............................................................................................................................................. 11

10BASE-T Receive .............................................................................................................................................. 11

SQE and Jabber Function (10BASE-T only) ....................................................................................................... 11

Auto-Negotiation .................................................................................................................................................. 11

MII Management Interface................................................................................................................................... 12

MII Data Interface ................................................................................................................................................ 12

Transmit Clock ............................................................................................................................................. 12

Receive Clock .............................................................................................................................................. 12

Transmit Enable ........................................................................................................................................... 12

Receive Data Valid ...................................................................................................................................... 12

Error Signals ................................................................................................................................................ 12

Carrier Sense ............................................................................................................................................... 12

Collision ........................................................................................................................................................ 13

RMII (Reduced MII) Data Interface ..................................................................................................................... 13

RMII Signal Definition .......................................................................................................................................... 13

Reference Clock .................................................................................................................................................. 13

Carrier Sense/Receive Data Valid ....................................................................................................................... 13

Receive Data ....................................................................................................................................................... 13

Transmit Enable................................................................................................................................................... 13

Transmit Data ...................................................................................................................................................... 14

Collision Detection ............................................................................................................................................... 14

RX_ER ........................................................................................................................................................... 14

RMII AC Characteristics ...................................................................................................................................... 14

Unused RMII Pins ................................................................................................................................................ 14

Auto-Crossover (Auto-MDI/MDI-X) ...................................................................................................................... 15

Power Management ............................................................................................................................................. 16

100BT FX Mode .................................................................................................................................................. 16

Media Converter Operation ................................................................................................................................. 16

Circuit Design Reference for Power Supply ........................................................................................................ 17

Register Map ........................................................................................................................................................... 18

Register 0h: Basic Control .................................................................................................................................. 18

Register 1h: Basic Status ................................................................................................................................... 18

Register 2h: PHY Identifier 1 .............................................................................................................................. 19

Register 3h: PHY Identifier 2 .............................................................................................................................. 19

Register 4h: Auto-Negotiation Advertisement ..................................................................................................... 19

Register 5h: Auto-Negotiation Link Partner Ability .............................................................................................. 19

Register 6h: Auto-Negotiation Expansion ........................................................................................................... 20

Register 7h: Auto-Negotiation Next Page ........................................................................................................... 20

Register 8h: Link Partner Next Page Ability ........................................................................................................ 20