1

DATASHEET

Dual Supply/Low Power/1024-Tap/SPI Bus, Single

Digitally-Controlled (XDCP™) Potentiometer

X9110

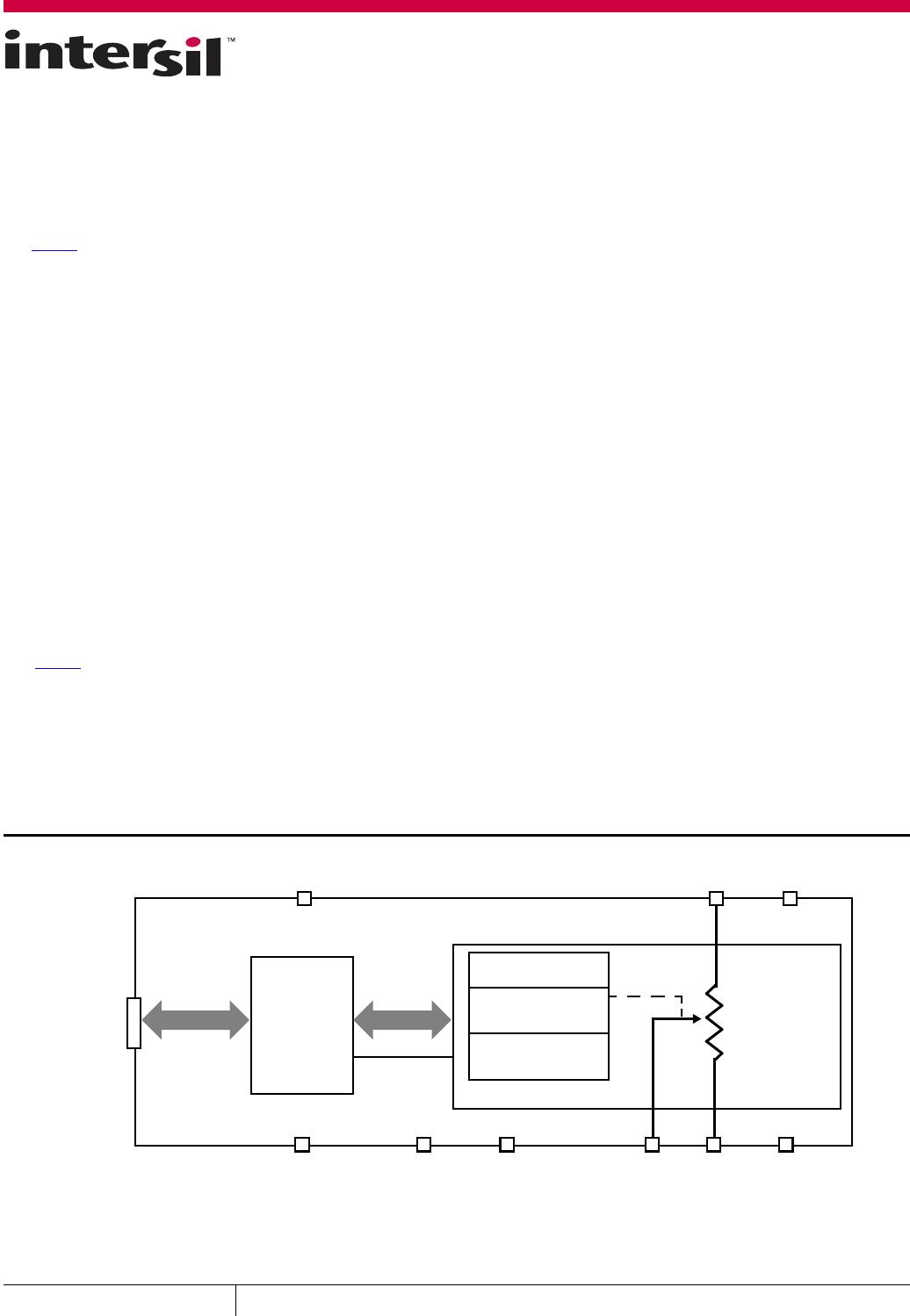

The X9110 integrates a Single Digitally Controlled

Potentiometer (XDCP) on a monolithic CMOS integrated circuit.

The digital controlled potentiometer is implemented using

1023 resistive elements in a series array. Between each

element are tap points connected to the wiper terminal

through switches. The position of the wiper on the array is

controlled by the user through the SPI bus interface. The

potentiometer has associated with it a volatile Wiper Counter

Register (WCR) and four nonvolatile data registers that can be

directly written to, and read by, the user. The contents of the

WCR controls the position of the wiper on the resistor array

though the switches. Power-up recalls the contents of the

default data register (DR0) to the WCR.

The XDCP can be used as a three-terminal potentiometer or as

a two terminal variable resistor in a wide variety of

applications including control, parameter adjustments, and

signal processing.

Related Literature

• For a full list of related documents, visit our website

- X9110

product page

Features

• 1024 resistor taps – 10-bit resolution

• SPI serial interface for write, read, and transfer operations of

the potentiometer

• Wiper resistance, 40Ωtypical at 5V

• Four nonvolatile data registers

• Nonvolatile storage of multiple wiper positions

• Power-on recall, loads saved wiper position on power-up

• Standby current <5µA maximum

•System V

CC

: 2.7V to 5.5V operation

• Analog V+/V-: -5V to +5V

• 100kΩend-to-end resistance

• 100 year data retention

• Endurance: 100,000 data changes per bit per register

•14 Ld TSSOP

• Dual supply version of the X9111

•Low power CMOS

• Pb-free (RoHS compliant)

FIGURE 1. FUNCTIONAL DIAGRAM

R

H

R

L

BUS

R

W

INTERFACE

CONTROL

POT

V

CC

V

SS

SPI

BUS

ADDRESS

DATA

STATUS

WRITE

READ

WIPER

1024-TAPS

TRANSFER

NC NC

100kΩ

POWER-ON RECALL

WIPER COUNTER

REGISTER (WCR)

DATA REGISTERS

(DR0-DR3)

CONTROL

INTERFACE

V+

V-

AND

October 28, 2016

FN8158.5

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774

| Copyright Intersil Americas LLC 2005, 2008, 2016. All Rights Reserved

Intersil (and design) and XDCP are trademarks owned by Intersil Corporation or one of its subsidiaries.

All other trademarks mentioned are the property of their respective owners.