REV. A

AD7390/AD7391

–8–

OPERATION

The AD7390 and AD7391 are a set of pin compatible, 12-bit/

10-bit digital-to-analog converters. These single-supply opera-

tion devices consume less than 100 microamps of current while

operating from power supplies in the 2.7 V to 5.5 V range mak-

ing them ideal for battery operated applications. They contain a

voltage-switched, 12-bit/10-bit, laser-trimmed digital-to-analog

converter, rail-to-rail output op amps, serial-input register, and

a DAC register. The external reference input has constant input

resistance independent of the digital code setting of the DAC.

In addition, the reference input can be tied to the same supply

voltage as V

DD

resulting in a maximum output voltage span of

0 to V

DD

. The SPI compatible, serial-data interface consists of

a serial data input (SDI), clock (CLK), and load (LD) pins.

A CLR pin is available to reset the DAC register to zero-scale.

This function is useful for power-on reset or system failure

recovery to a known state.

D/A CONVERTER SECTION

The voltage switched R-2R DAC generates an output voltage

dependent on the external reference voltage connected to the

V

REF

pin according to the following equation:

VV

D

OUT REF

N

=×

2

(1)

where D is the decimal data word loaded into the DAC register,

and N is the number of bits of DAC resolution. In the case of the

10-bit AD7391 using a 2.5 V reference, Equation 1 simplifies to:

V

D

OUT

=×25

1024

.

(2)

Using Equation 2 the nominal midscale voltage at V

OUT

is

1.25 V for D = 512; full-scale voltage is 2.497 V. The LSB step

size is = 2.5 1/1024 = 0.0024 V.

For the 12-bit AD7390 operating from a 5.0 V reference

Equation 1 becomes:

V

D

OUT

=×50

4096

.

(3)

Using Equation 3 the AD7390 provides a nominal midscale

voltage of 2.5 V for D = 2048, and a full-scale output of 4.998 V.

The LSB step size is = 5.0 1/4096 = 0.0012 V.

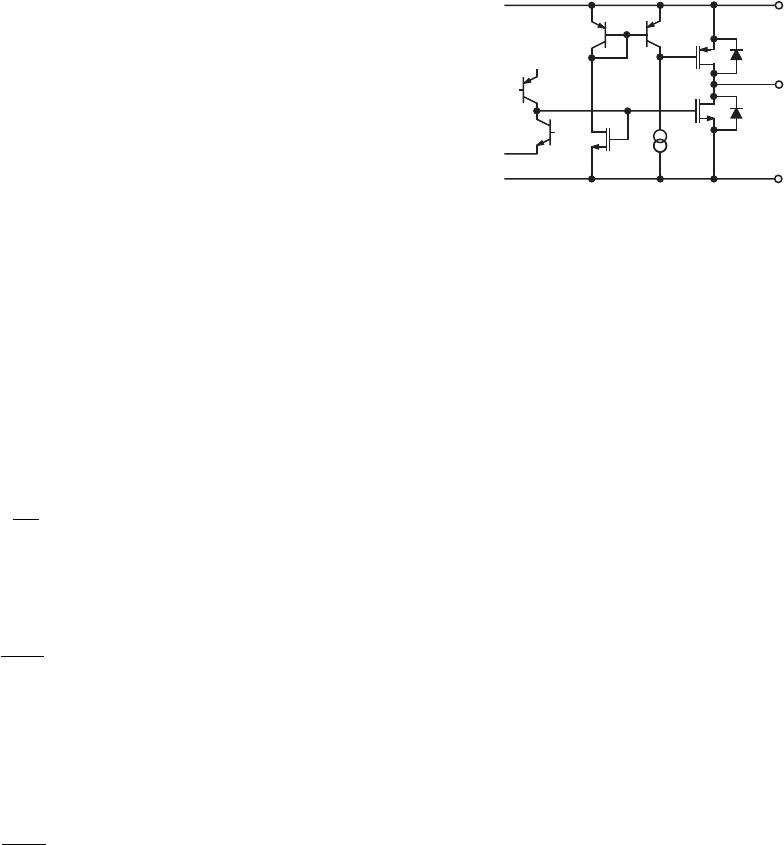

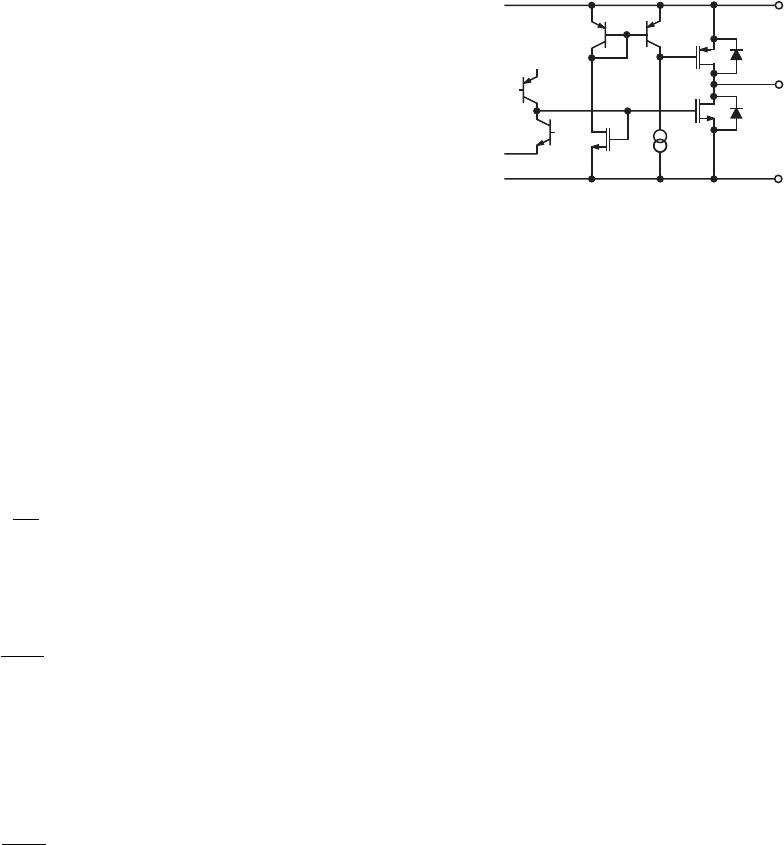

AMPLIFIER SECTION

The internal DAC’s output is buffered by a low power con-

sumption precision amplifier. The op amp has a 60 µs typical

settling time to 0.1% of full scale. There are slight differences in

settling time for negative slewing signals versus positive. Also,

negative transition settling time to within the last 6 LSBs of zero

volts has an extended settling time. The rail-to-rail output stage

of this amplifier has been designed to provide precision perfor-

mance while operating near either power supply. Figure 5

shows an equivalent output schematic of the rail-to-rail ampli-

fier with its N-channel pull-down FETs that will pull an output

load directly to GND. The output sourcing current is provided

by a P-channel pull-up device that can source current to GND

terminated loads.

AGND

V

OUT

V

DD

P-CH

N-CH

Figure 5. Equivalent Analog Output Circuit

The rail-to-rail output stage provides ±1 mA of output current.

The N-channel output pull-down MOSFET shown in Figure 5

has a 35 Ω ON resistance, which sets the sink current capability

near ground. In addition to resistive load driving capability, the

amplifier has also been carefully designed and characterized for

up to 100 pF capacitive load driving capability.

REFERENCE INPUT

The reference input terminal has a constant input-resistance

independent of digital code which results in reduced glitches on

the external reference voltage source. The high 2 MΩ input-

resistance minimizes power dissipation within the AD7390/

AD7391 D/A converters. The V

REF

input accepts input voltages

ranging from ground to the positive-supply voltage V

DD

. One of

the simplest applications which saves an external reference

voltage source is connection of the V

REF

terminal to the positive

V

DD

supply. This connection results in a rail-to-rail voltage

output span maximizing the programmed range. The reference

input will accept ac signals as long as they are kept within the

supply voltage range, 0 < V

REF IN

< V

DD

. The reference band-

width and integral nonlinearity error performance are plotted in

the typical performance section (see TPCs 14 and 15). The

ratiometric reference feature makes the AD7390/AD7391 an

ideal companion to ratiometric analog-to-digital converters such

as the AD7896.

POWER SUPPLY

The very low power consumption of the AD7390/AD7391 is a

direct result of a circuit design optimizing the use of a CBCMOS

process. By using the low power characteristics of CMOS for the

logic, and the low noise, tight-matching of the complementary

bipolar transistors, excellent analog accuracy is achieved. One

advantage of the rail-to-rail output amplifiers used in the AD7390/

AD7391 is the wide range of usable supply voltage. The part is

fully specified and tested for operation from 2.7 V to 5.5 V.

POWER SUPPLY BYPASSING AND GROUNDING

Precision analog products, such as the AD7390/AD7391, require

a well filtered power source. Since the AD7390/AD7391 operates

from a single 3 V to 5 V supply, it seems convenient to simply tap

into the digital logic power supply. Unfortunately, the logic sup-

ply is often a switch-mode design, which generates noise in the

20 kHz to 1 MHz range. In addition, fast logic gates can generate

glitches hundred of millivolts in amplitude due to wiring resis-

tance and inductance. The power supply noise generated thereby

means that special care must be taken to assure that the inherent

precision of the DAC is maintained. Good engineering judgment

should be exercised when addressing the power supply ground-

ing and bypassing of the AD7390.