NB3V110xC Series

www.onsemi.com

5

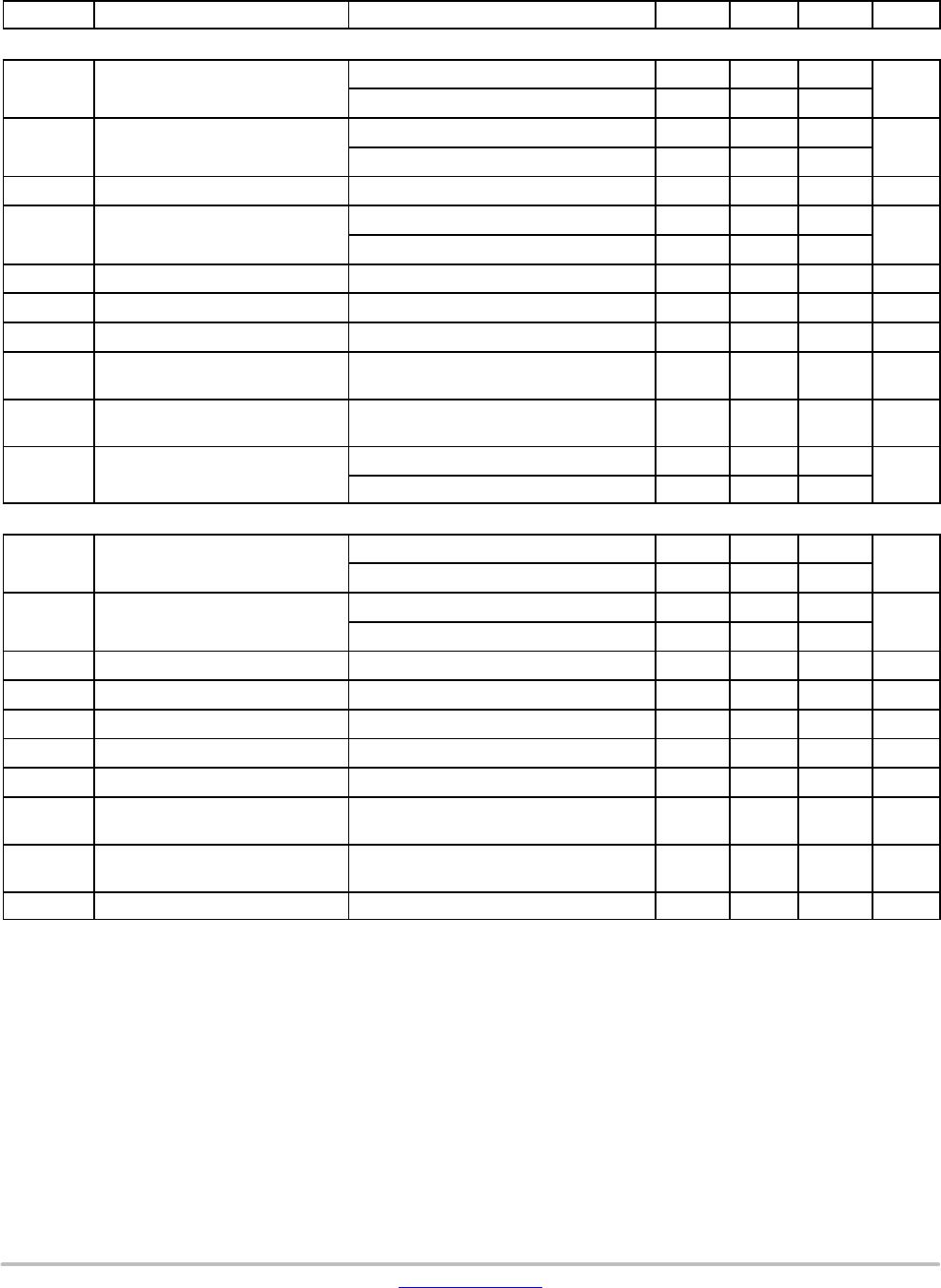

Table 6. DEVICE CHARACTERISTICS Over recommended operating free−air temperature range (unless otherwise noted) (Note 5)

Symbol

Parameter Condition Min Typ Max Unit

OVERALL PARAMETERS FOR ALL VERSIONS

I

DD

Static device current

OE = V

DD

; CLKIN = 0 V or V

DD

; I

O

= 0 mA; V

DD

=

3.6 V

0.2

mA

OE = V

DD

; CLKIN = 0 V or V

DD

; I

O

= 0 mA; V

DD

=

2.7 V

0.2

OE = V

DD

; CLKIN = 0 V or V

DD

; I

O

= 0 mA; V

DD

=

1.89 V

0.2

I

PD

Power down current

OE = 0 V; CLKIN = 0 V or V

DD

; I

O

= 0 mA; V

DD

=

3.6 V, 2.7 V or 1.89 V (For 1102C, 1103C, 1104C)

60

mA

OE = 0 V; CLKIN = 0 V or V

DD

; I

O

= 0 mA; V

DD

=

3.6 V, 2.7 V or 1.89 V (For 1106C, 1108C)

75

C

PD

Power dissipation capacitance per out-

put (Note 6)

V

DD

= 3.3 V; f = 10 MHz 9

pF

V

DD

= 2.5 V; f = 10 MHz 9

V

DD

= 1.8 V; f = 10 MHz 9

I

I

Input leakage current at OE

V

I

= 0 V or V

DD

, V

DD

= 3.6 V or 2.7 V

± 8

mA

Input leakage current at CLKIN ± 8

Input leakage current at OE, CLKIN V

I

= 0 V or V

DD

, V

DD

= 1.89 V ± 8

R

OUT

Output impedance

V

DD

= 3.3 V 40

W

V

DD

= 2.5 V 45

V

DD

= 1.8 V 60

f

OUT

Output frequency

V

DD

= 3.0 V to 3.6 V DC 250

MHz

V

DD

= 2.3 V to 2.7 V DC 180

V

DD

= 1.71 V to 1.89 V DC 133

OUTPUT PARAMETERS FOR V

DD

= 3.3 V + 0.3 V

V

OH

High−level output voltage

V

DD

= 3 V, I

OH

= –0.1 mA 2.9

V

V

DD

= 3 V, I

OH

= –8 mA 2.5

V

DD

= 3 V, I

OH

= –12 mA 2.2

V

OL

Low−level output voltage

V

DD

= 3 V, I

OL

= 0.1 mA 0.1

V

V

DD

= 3 V, I

OL

= 8 mA 0.5

V

DD

= 3 V, I

OL

= 12 mA 0.8

t

PLH

, t

PHL

Propagation delay (Note 7) CLKIN to Qn 0.8 2.0 ns

t

sk(o)

Output skew (Note 7)

Equal load of each output 85°C 50

ps

Equal load of each output 105°C 60

t

r

/t

f

Rise and fall time 20%–80% (V

OH

− V

OL

) 0.12 0.8 ns

t

DIS

Output disable time (Note 7) OE to Qn 6 ns

t

EN

Output enable time (Note 7) OE to Qn 6 ns

t

sk(p)

Pulse skew; tPLH(Qn) – tPHL(Qn) (Note 8) To be measured with input duty cycle of 50% 180 ps

t

sk(pp)

Part−to−part skew Under equal operating conditions for two parts 0.5 ns

T

jit(

f

)

Additive jitter rms

12 kHz...20 MHz f

OUT

= 100 MHz

100 fs

12 kHz...20 MHz f

OUT

= 156.25 MHz

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. All typical values are at respective nominal V

DD

. For switching characteristics, outputs are terminated to 50 W to V

DD

/2 (see Figure 2).

6. This is the formula for the power dissipation calculation.

Ptot = Pstat + Pdyn + PCload [W] P

stat

= V

DD

x I

DD

[W]

P

dyn

= C

PD

x V

DD

2 x ƒ x n [W]

P

Cload

= C

load

x V

DD

2 x ƒ x n [W]

n = Number of switching output pins

7. With rail to rail input clock.

8. t

sk(p)

depends on output rise− and fall−time (t

r

/t

f

). The output duty−cycle can be calculated: odc = (t

w(OUT)

± t

sk(p)

)/t

period

; t

w(OUT)

is

pulse−width of ideal output waveform and tperiod is 1/f

OUT

.