2©2015 Integrated Device Technology, Inc. Revision C, December 8, 2015

8545 Datasheet

Pin Description and Pin Characteristic Tables

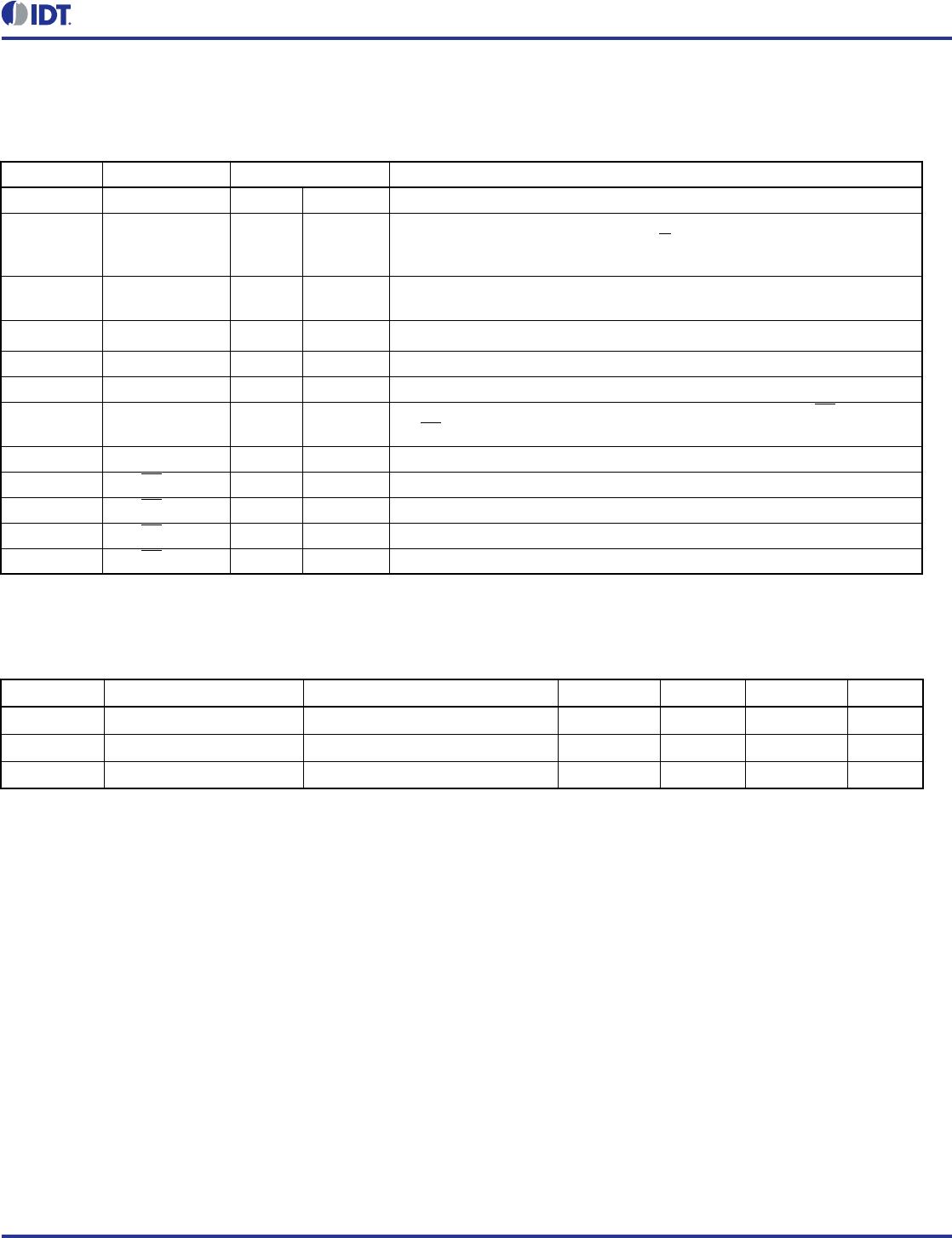

Table 1. Pin Descriptions

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

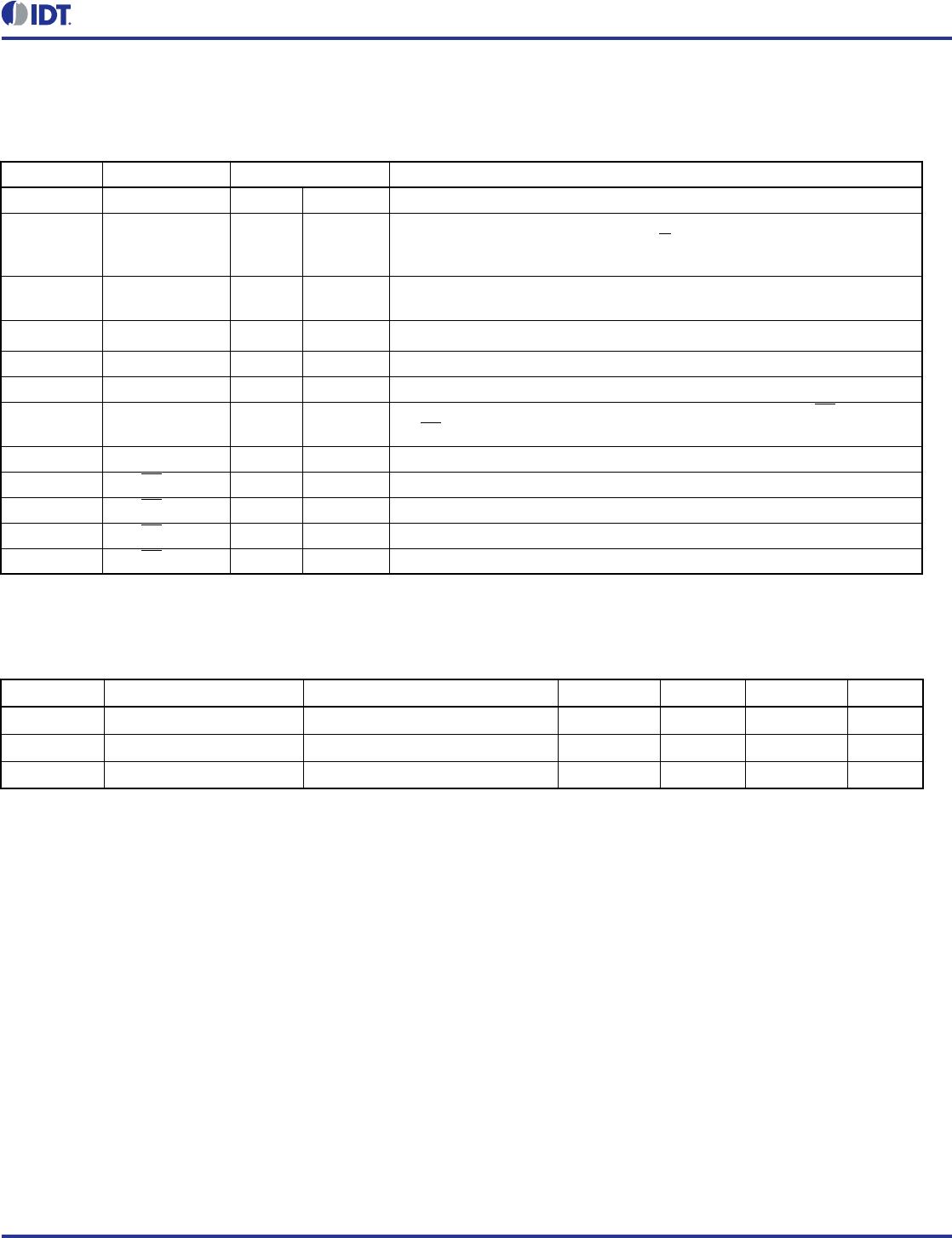

Table 2. Pin Characteristics

Number Name Type Description

1, 9, 13 GND Power Power supply ground.

2 CLK_EN Input Pullup

Synchronizing clock enable. When HIGH, clock outputs follows clock input.

When LOW, Q outputs are forced low, Q

outputs are forced high.

LVCMOS / LVTTL interface levels.

3 CLK_SEL Input Pulldown

Clock select input. When HIGH, selects CLK2 input.

When LOW, selects CLK1 input. LVCMOS / LVTTL interface levels.

4 CLK1 Input Pulldown Single-ended clock input. LVCMOS/LVTTL interface levels.

5, 7 nc Unused No connect.

6 CLK2 Input Pulldown Single-ended clock input. LVCMOS/LVTTL interface levels.

8 OE Input Pullup

Output enable. Controls enabling and disabling of outputs Q0/Q0

through

Q3/Q3

. LVCMOS/LVTTL interface levels.

10, 18 V

DD

Power Positive supply pins.

11, 12 Q3

, Q3 Output Differential output pair. LVDS interface levels.

14, 15 Q2

, Q2 Output Differential output pair. LVDS interface levels.

16, 17 Q1

, Q1 Output Differential output pair. LVDS interface levels.

19, 20 Q0

, Q0 Output Differential output pair. LVDS interface levels.

Symbol Parameter Test Conditions Minimum Typical Maximum Units

C

IN

Input Capacitance 4 pF

R

PULLUP

Input Pullup Resistor 51 k

R

PULLDOWN

Input Pulldown Resistor 51 k