MAX5417/MAX5418/MAX5419

256-Tap, Nonvolatile, I

2

C-Interface,

Digital Potentiometers

_______________________________________________________________________________________ 9

Analog Circuitry

The MAX5417/MAX5418/MAX5419 consist of a resistor

array with 255 resistive elements; 256 tap points are

accessible to the wiper, W, along the resistor string

between H and L. The wiper tap point is selected by

programming the potentiometer through the 2-wire (I

2

C)

interface. Eight data bits, an address byte, and a con-

trol byte program the wiper position. The H and L termi-

nals of the MAX5417/MAX5418/MAX5419 are similar to

the two end terminals of a mechanical potentiometer.

The MAX5417/MAX5418/MAX5419 feature power-on

reset circuitry that loads the wiper position from non-

volatile memory at power-up.

Digital Interface

The MAX5417/MAX5418/MAX5419 feature an internal,

nonvolatile EEPROM that stores the wiper state for ini-

tialization during power-up. The shift register decodes

the control and address bits, routing the data to the

proper memory registers. Data can be written to a

volatile memory register, immediately updating the

wiper position, or data can be written to a nonvolatile

register for storage.

The volatile register retains data as long as the device

is powered. Once power is removed, the volatile regis-

ter is cleared. The nonvolatile register retains data even

after power is removed. Upon power-up, the power-on

reset circuitry controls the transfer of data from the non-

volatile register to the volatile register.

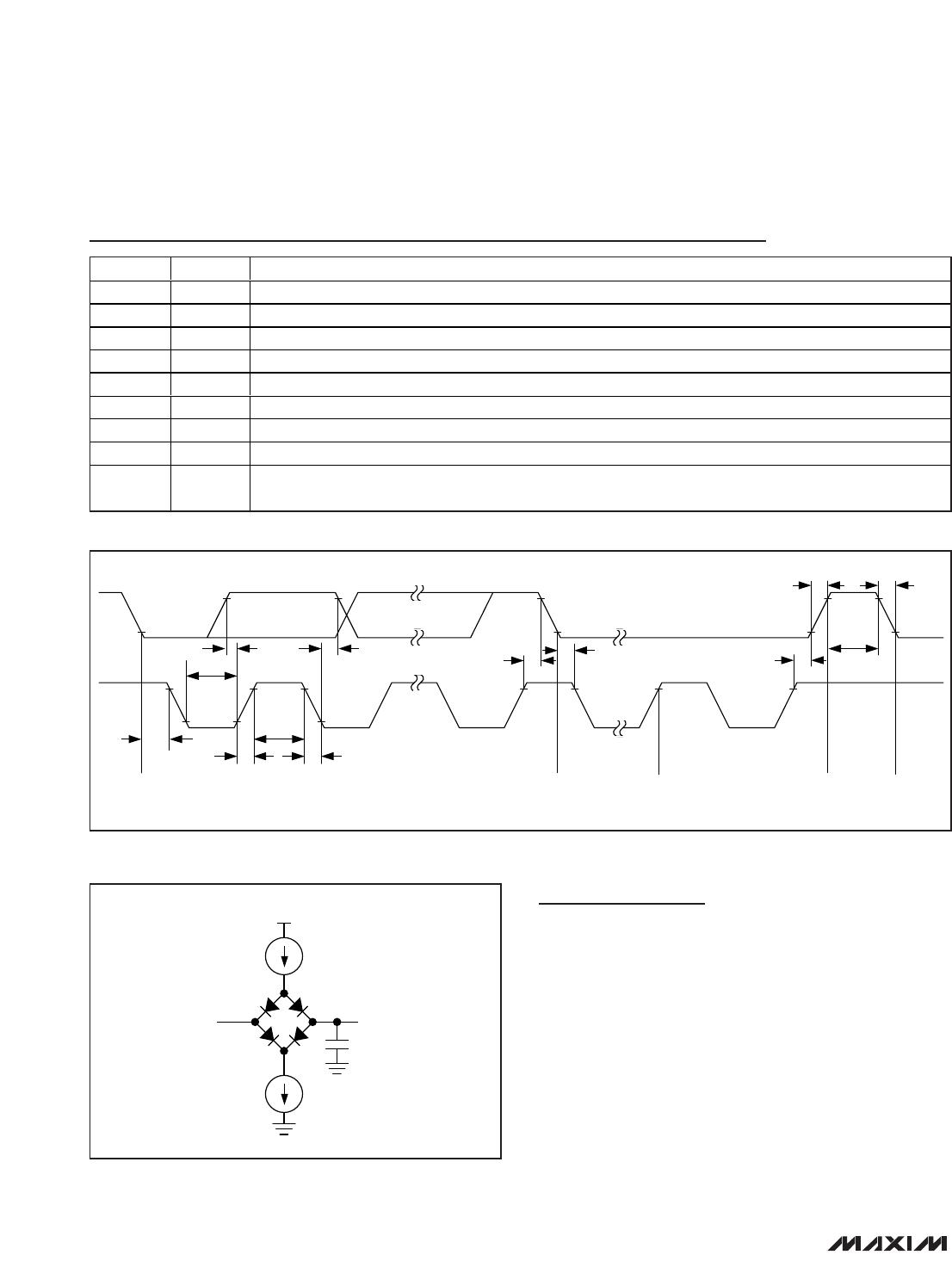

Serial Addressing

The MAX5417/MAX5418/MAX5419 operate as a slave

that receives data through an I

2

C- and SMBus™-com-

patible 2-wire interface. The interface uses a serial data

access (SDA) line and a serial clock line (SCL) to

achieve communication between master(s) and

slave(s). A master, typically a microcontroller, initiates

all data transfers to the MAX5417/MAX5418/MAX5419,

and generates the SCL clock that synchronizes the

data transfer (Figure 1).

The MAX5417/MAX5418/MAX5419 SDA line operates

as both an input and an open-drain output. A pullup

resistor, typically 4.7kΩ, is required on the SDA bus.

The MAX5417/MAX5418/MAX5419 SCL operates only

as an input. A pullup resistor, typically 4.7kΩ, is

required on the SCL bus if there are multiple masters

on the 2-wire interface, or if the master in a single-mas-

ter system has an open-drain SCL output.

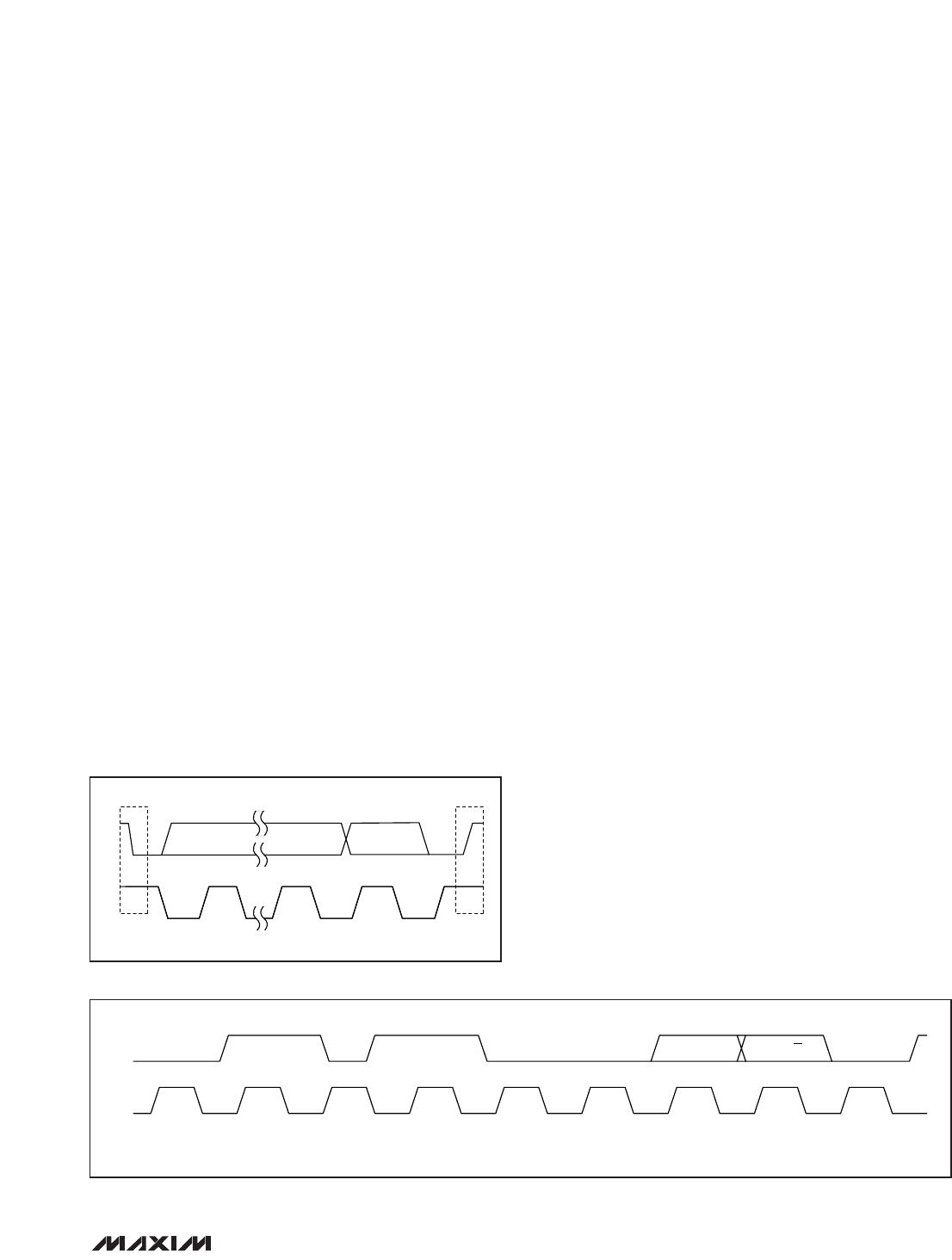

Each transmission consists of a START (S) condition

(Figure 3) sent by a master, followed by the

MAX5417/MAX5418/MAX5419 7-bit slave address plus

the 8th bit (Figure 4), 1 command byte (Figure 7) and 1

data byte, and finally a STOP (P) condition (Figure 3).

Start and Stop Conditions

Both SCL and SDA remain high when the interface is

not busy. A master signals the beginning of a transmis-

sion with a START condition by transitioning SDA from

high to low while SCL is high. When the master has fin-

ished communicating with the slave, it issues a STOP

condition by transitioning the SDA from low to high

while SCL is high. The bus is then free for another

transmission (Figure 3).

Bit Transfer

One data bit is transferred during each clock pulse.

The data on the SDA line must remain stable while SCL

is high (Figure 5).