AD421

–10–

REV. C

A capacitor of 0.01 µF connected between COMP and DRIVE

is required to stabilize the feedback loop formed with the

regulator op amp and the external pass transistor. An external

snubber circuit of 1 kΩ and 1000 pF is required between the

DRIVE pin and COM and a 0.1 µF cap between COMP and

DRIVE to stabilize the feedback loop formed by the regulator

op amp and the external pass transistor.

The internal 2.5 V reference on the AD421 is used as the refer-

ence for the AD421 and this has to be decoupled with a 4.7 µF

capacitor for compensation and stability purposes. The sigma-

delta DAC on the part consists of a second order modulator

followed by a continuous time filter. The resistors for each of

the filter sections are on-chip while the capacitors are external

on the C1 to C3 pins. To meet the specified full-scale settling

on the part, low dielectric absorption capacitors (NPO) are

required. Suitable values for these capacitors are C1 = C2 =

0.01 µF, and C3 = 0.0033 µF.

The digital interface on the AD421 consists of just three wires:

DATA, CLOCK and LATCH. The interface connects directly

to the serial ports of commonly-used microcontrollers without

the need for any external glue logic. Data is loaded into an input

shift register on the rising edge of the CLOCK signal and is

transferred to the DAC latch on the rising edge of the LATCH

signal.

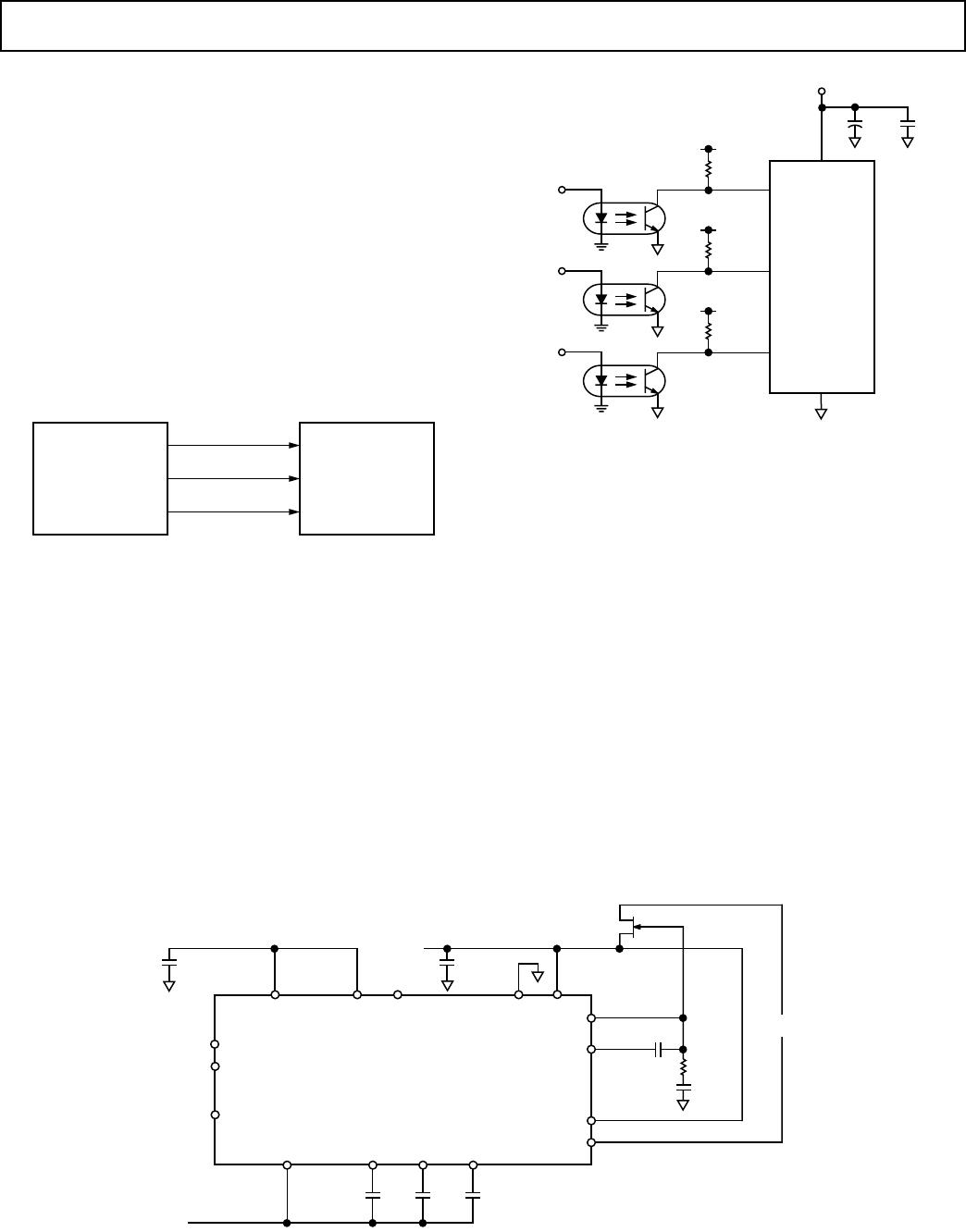

Reduce Power Load on External FET

Figure 12 shows a circuit where an external NPN transistor is

added to reduce the power loading on the FET. The FET will

supply the V

CC

and an external high voltage NPN bipolar tran-

sistor can carry the BOOST current. The BOOST pin sinks the

necessary current from the loop so that the current flowing into

BOOST plus the current flowing into COM is equal to the

programmed loop current. The external NPN transistor reduces

the external power load that the FET has to carry to less than

750 µA if no other components share the V

CC

line and to less

than 4 mA in applications that share the same V

CC

line as the

AD421.

1.21V

112.5k⍀

134k⍀

75k⍀

121k⍀

V

CC

LV

2.2F

COM

V

CC

TO EXTERNAL

CIRCUITRY

DN25D

DRIVE

COMP

0.01F

1k⍀

1000pF

LOOP(+)

BANDGAP

REFERENCE

AD421

BC639/BC337

BOOST

40⍀

80k⍀

LOOP RTN

LOOP(–)

Figure 12. External NPN Transistor Reduces Power Load

on FET

Smart Transmitter

The AD421 is intended for use in 4 mA to 20 mA smart trans-

mitters. A smart transmitter is a system that incorporates a

microprocessor system which is used for linearization and

communication. Figure 13 shows a block diagram of a typical

smart transmitter. In this example, the transmitter does not have

any digital communication capabilities.

4mA TO 20mA

MEASUREMENT

CIRCUIT

MICRO-

PROCESSOR

D/A

CONVERTER

A/D

CONVERTER

MEMORY

SENSORS

Figure 13. Typical Smart Transmitter

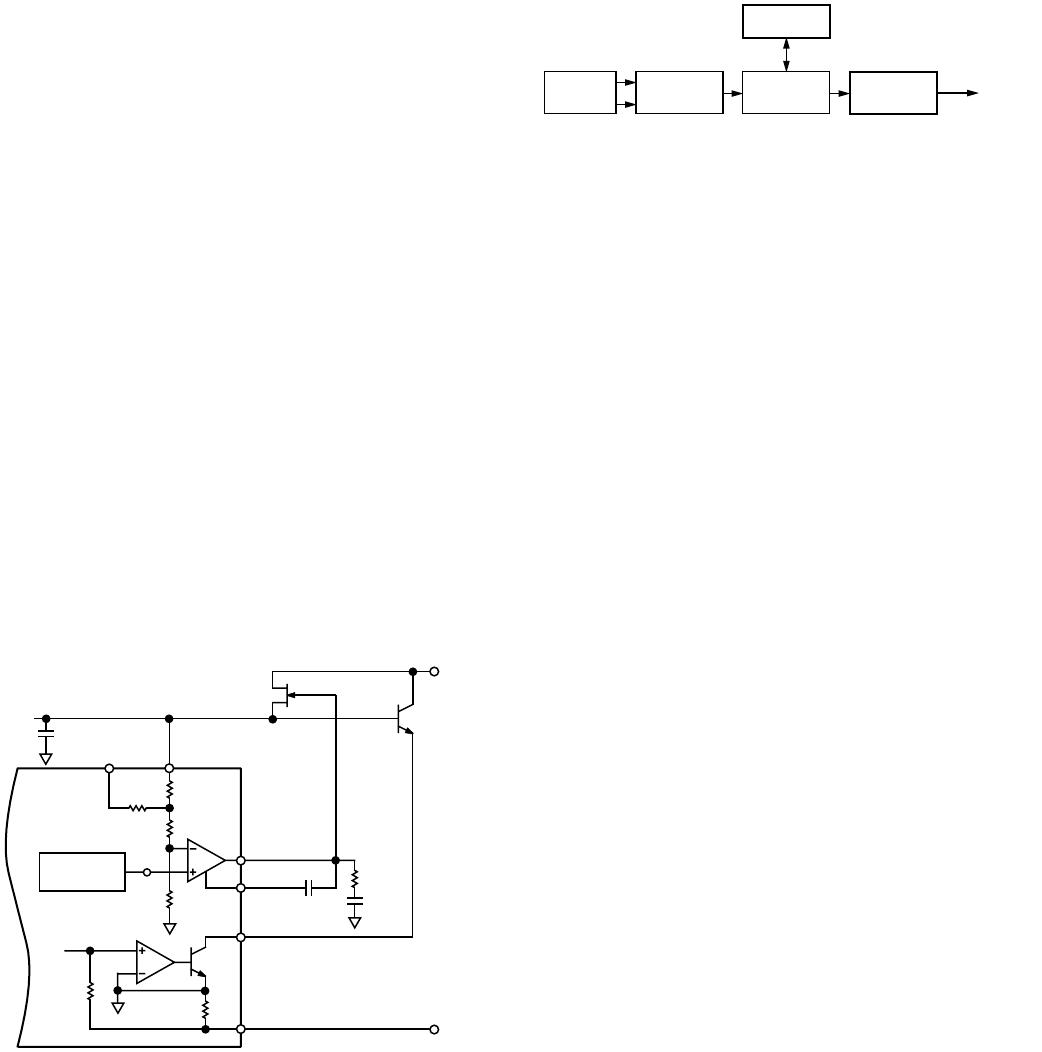

Figure 14 shows a typical smart transmitter application circuit

using the AD421.

The sensor voltage to be measured at the transmitter is con-

verted using a high resolution sigma-delta converter such as

the AD7714 or AD7715. These devices have an on-board PGA

which can provide gains on the analog front end from 1 to 128.

This allows for an analog input range as low as 10 mV which

allows the transducer to be connected directly to the ADC. The

AD7714/AD7715 have digital calibration techniques which are

used to eliminate gain and offset errors. In addition, back-

ground calibration techniques are provided whereby the part

continually calibrates itself and the user does not have to

worry about issuing periodic calibration commands to remove

effects of time and temperature drift.

In normal operation the microprocessor reads the data from the

AD7714/AD7715. After the data is processed by the micro-

controller, the data is transferred from the serial port of the

processor to the AD421 for transmission over the 4 to 20 mA

loop back to the control center.

The AD421 regulates the loop voltage to create power for the

rest of the transmitter circuitry. In Figure 14, the derived V

CC

voltage is 3.3 V which is achieved by connecting the LV pin to

V

CC

through 0.01 µF. REF OUT2 provides the reference volt-

age for the AD421 itself while REF OUT1 provides the refer-

ence voltage for the AD7714/AD7715.