IDT5V49EE503

EEPROM PROGRAMMABLE CLOCK GENERATOR CLOCK SYNTHESIZER

IDT®

EEPROM PROGRAMMABLE CLOCK GENERATOR 21

IDT5V49EE503 REV Q 071015

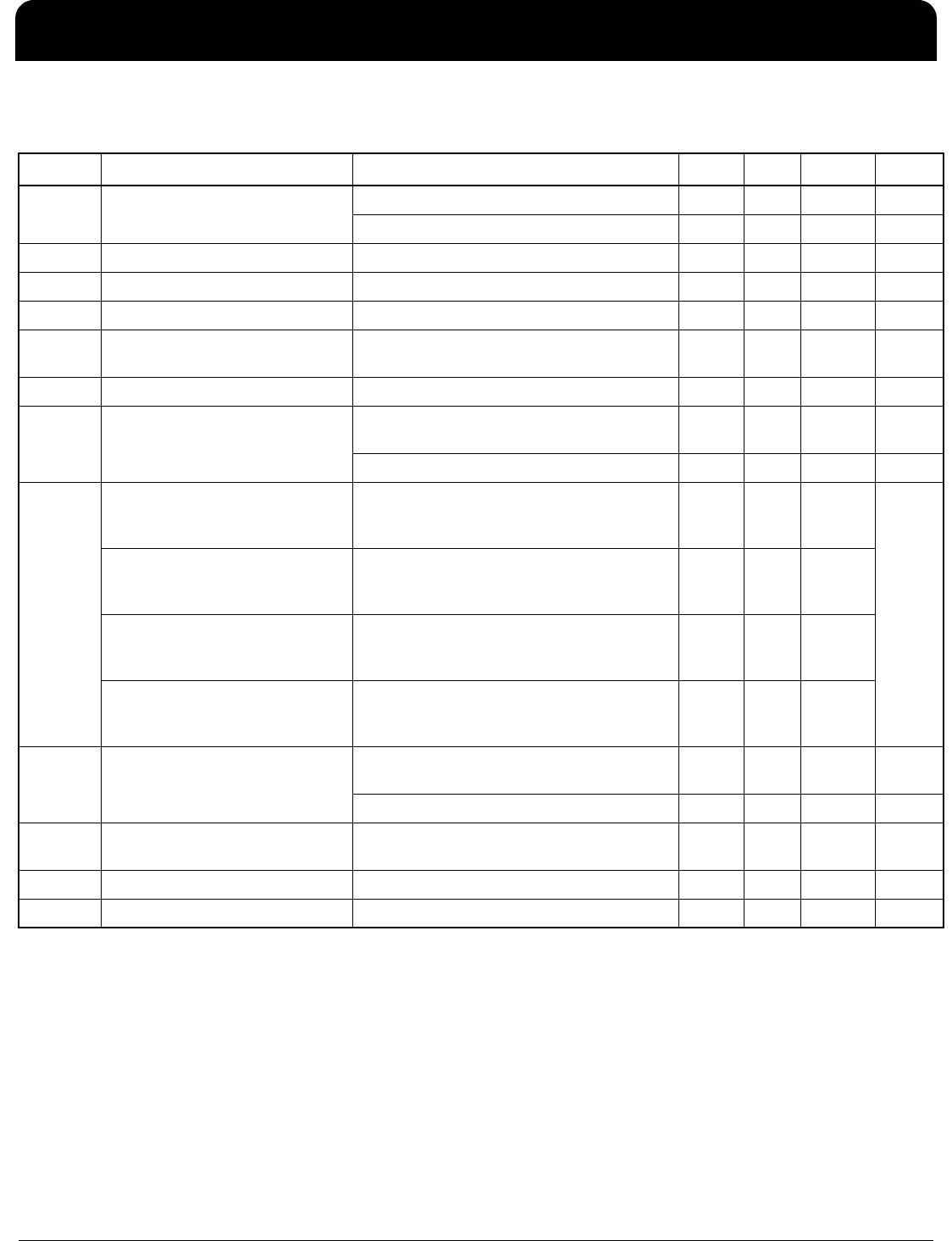

Programming Registers Table

Addr

Default

Register

Hex

Value

Bit #

Description

7654321 0

0x00 00

Reserved HW/SW

Hardware/Software Mode control

HW/SW - 0=HW, 1=SW

0x01 00

Reserved SEL[2:0]

SEL[2:0] - selects configuration in

SW mode

0x02 02

SP OE6 Reserved Reserved OE3 OE2 OE1 OE0

OEx=Output Power Suspend

function for OUTx (‘1’=OUTx will

be suspended on SD/OE pin.

Disable mode is defined by OEMx

bits), ‘0’=outputs enabled and no

association with OE pin (default).

0x03 02

Reserved OS*6 Reserved Reserved OS*3 OS*2 OS*1 OS*0

OS*[6:0] - output suspend, active

low. Overwrites OE setting.

0x04 0F

SH OS*Reserved PLLS*[3:0]

PLLS*[3:0] - PLL Suspend, active

low

SH - shutdown/OE configuration

0x05 04

Reserved XTCLKSEL Reserved

XTCLKSEL - crystal/clock select.

0=Crytal, 1=ICLK

0x06 00

Reserved

0x07 00

Reserved

XTAL[4:0] XTAL[4:0] - crystal cap

0x08 00

Reserved

0x09 00

Reserved

0x0A 10

CZ0_CFG4 IP0[2:0]_CFG4 RZ0[3:0]_CFG4

PLL0 loop parameter

0x0B 10

CZ0_CFG5 IP0[2:0]_CFG5 RZ0[3:0]_CFG5

0x0C 10

CZ0_CFG0 IP0[2:0]_CFG0 RZ0[3:0]_CFG0

0x0D 10

CZ0_CFG1 IP0[2:0]_CFG1 RZ0[3:0]_CFG1

0x0E 10

CZ0_CFG2 IP0[2:0]_CFG2 RZ0[3:0]_CFG2

0x0F 10

CZ0_CFG3 IP0[2:0]_CFG3 RZ0[3:0]_CFG3

0x10 00

Reserved D0[6:0]_CFG0

PLL0 input divider and input sel

D0[6:0] - 127 step Ref Div

D0 = 0 means power down.

0x11 00

Reserved D0[6:0]_CFG1

0x12 00

Reserved D0[6:0]_CFG2

0x13 00

Reserved D0[6:0]_CFG3

0x14 00

Reserved D0[6:0]_CFG4

0x15 00

Reserved D0[6:0]_CFG5

0x16 01

N0[7:0]_CFG4

N - Feedback Divider

2 - 4095 (values of “0” and “1” are

not allowed) Total feedback with

A, using provided calculation

0x17 01

N0[7:0]_CFG5

0x18 01

N0[7:0]_CFG0

0x19 01

N0[7:0]_CFG1

0x1A 01

N0[7:0]_CFG2

0x1B 01

N0[7:0]_CFG3

0x1C 00

A0[3:0]_CFG0 N0[11:8]_CFG0

0x1D 00

A0[3:0]_CFG1 N0[11:8]_CFG1

0x1E 00

A0[3:0]_CFG2 N0[11:8]_CFG2

0x1F 00

A0[3:0]_CFG3 N0[11:8]_CFG3

0x20 00

A0[3:0]_CFG4 N0[11:8]_CFG4

0x21 00

A0[3:0]_CFG5 N0[11:8]_CFG5

0x22 10

CZ1_CFG4 IP1[2:0]_CFG4 RZ1[3:0]_CFG4

PLL1 Loop Parameter

0x23 10

CZ1_CFG5 IP1[2:0]_CFG5 RZ1[3:0]_CFG5

0x24 10

CZ1_CFG0 IP1[2:0]_CFG0 RZ1[3:0]_CFG0

0x25 10

CZ1_CFG1 IP1[2:0]_CFG1 RZ1[3:0]_CFG1

0x26 10

CZ1_CFG2 IP1[2:0]_CFG2 RZ1[3:0]_CFG2

0x27 10

CZ1_CFG3 IP1[2:0]_CFG3 RZ1[3:0]_CFG3